Многоканальное адаптивное аналого-цифровое устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для преобразования в цифровые коды множества аналоговых сигналов, изменение которых от канала к каналу имеет равномерный закон распределения по всему динамическому диапазону. Цель изобретения - повышение быстродействия устройствыа. В устройство, содержащее N триггеров (N -число каналов) 8.1-8.N, элемент И 9, цифровой сумматор 4, регистр 5 памяти, цифроаналоговый преобразователь 6, с целью повышения быстродействия введены аналоговый коммутатор 2, аналого-цифровой преобразователь 3, N вычитателей 1.1-1.N и блок 7 определения канала с минимальным сигналом. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5g 4 Н 03 М 1/48

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

Н д ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4234302/24-24 (22) 22.04.87 (46) 07.11.89 Бюл. № 41 (71) Новосибирский электротехнический институт (72) A.Б.Жуков, В.М.Сидоров и Д.В.Шелемин (53) 681.325 (088.8) (56) Золотова Т.М., Кербликов A.È., Резенблат М.А. Резервирование аналоговых устройств автоматики. — М., 1986,. с. 95 °

Авторское свидетельство СССР

¹ 1267618, кл. Н 03 M 1/48, 1986. (54) МНОГОКАНАЛЬНОЕ АДАПТИВНОЕ АНАЛОГО-ЦИФРОВОЕ УСТРОЙСТВО (57) Изобретение относится к области автоматики и вычислительной техники

Я0 1520 60 А1

2 и может быть использовано для преобразования в цифровые коды множества аналоговых сигналов, изменение которых от канала к каналу имеет равномерный закон распределения по всему динамическому диапазону. Цель изобретения — повьппение быстродействия устройства. В устройство, содержащее

N триггеров (N — число каналов)

8,1-8.N, элемент И9, цифровой сумматор 4, регистр 5 памяти, цифроаналоговый преобразователь 6, с целью повыщения быстродействия введены аналоговый коммутатор 2, аналого-цифровой преобразователь 3, N вычитателей

1.1-1.N и блок 7 определения канала с минимальным сигналом. 1 э.п. ф-лы, 3 ил.

1520660

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования в цифровые коды множества аналоговых сигналов„ изменение которых от канала к каналу имеет равномерный закон распределения по всему динамическому диапазону.

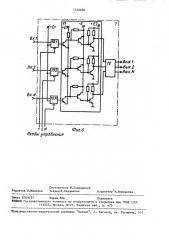

Целью изобретения является повыше- 10 ние быстродействия, На фиг.1 приведена структурная схема многоканального адаптивного аналого-цифрового устройства; на фиг.2 - временная диаграмма, поясняю- 1 щая работу устройства; на фиг. 3 функциональная схема блока определения канала с минимальным сигналом.

Устройство (фиг.1) содержит И вычитателей 1.1-1,N аналоговый коммутатор 2, аналого-цифровой преобразователь (АЦП) 3, цифровой сумматор

4, регистр 5 памяти, цифроаналоговый преобразователь (ЦАП) 6, блок 7 определения канала с минимальным сигна- 25 лом, N триггеров 8.1-8.N, элемент

И9 и ключи 10.1-10.N.

Блок 7 (фиг.3) содержит элемент Il выбора канала и приоритетный шифратор 12.

Многоканальное адаптивное аналогоцифровое устройство работает следующим образом.

В начальный момент t, триггеры

8.1-8,N и регистр 5 находятся в нулевом состоянии (установка в "0" на

35 схеме не наказана), Напряжение на вычитающих входах вычитателей

1.1-1.N равно нулю, и входные сигналы без изменения проходят на входы аналогового коммутатора 2. Входные сигналы подаются также на входы блока 7 определения канала с минимальным сигналом. На выходе этого блока, соответсгвующем входу с минимальным 45 в данный момент времени сигналом (например, втором), вырабатывается сигнал уровня логической "1", на остальных выходах блока 7 — "0", Уровень логической "1" с выхода блока 7 определения канала -с минимальным сигналом поступает на вход управления аналогового коммутатора 2,подключающего к АЦП 3 минимальный из входЪ ных сигналов и на I-вход соответстФ

55 вующего триггера 8.2. При помощи

АЦП 3 производится аналого-цифровое преобразование входного сигнала,т.е. на выходе АЦП 3 возникает кад,соответствующий величине минимального из входных сигнала (2-й канал). Этот код суммируется цифровым сумматором 4 с кодом, хранящимся в регистре 5 памяти, и подается на входы регистра

5 памяти. По переднему фронту тактового импульса код записывается в регистр 5 памяти. В дальнейшем код,соответствующий аналоговой величине второго канала, поступает на вход

ЦАП 6 и на выходные шины устройства.

При помощи ЦАП 6 осуществляется преобразование двоичного кода в аналоговый сигнал, т.е. с выхода ЦАП 6 снимается сигнал, напряжение которого равно наименьшему из входных напряжений. Это напряжение поступает на вычитающие входы вычитателей 1.1

1.N. По заднему фронту тактового импульса триггер 8.2, íà I-входе которого находится уровень логической

t3 11

1, устанавливается в единичное состояние. В дальнейшем сигнал уровня логической "1" с выхода триггера 8.2 поступает на соответствующий вход управления блока 7 определения канала с минимальным сигналом и выключает второй канал. Затем блок 7 определяет канал с минимальным по величине входным сигналом из оставшихся включенными каналов (1-й канал) и формирует сигнал уровня логической "1" на соответствующем выходе.

По сигналу с выхода блока 7 определения канала с минимальным сигналом аналоговый коммутатор 2 подключает к входу АЦП 3 выход первого вычитателя 1.1, на котором находится напряжение, равное разности между вторым по величине и наименьшим входными сигналами. В дальнейшем устройство работает аналогично, АЦП 3 преобразует разности между соседними по величине входными сигналами канала, а в регистре 5 памяти поочередно формируются коды, соответствующие входным сигналам, которые возникают путем суммирования и накопления этих разностей. По сигналам на выходных . шинах адреса канала можно определить, какой именно канал включен в данный момент. По окончании цикла опроса всех каналов многоканального адаптивного следящего АЦП триггеры 8.1-8.М устанавливаются в единичное состояние (t< ), íà выходе элемента И 9 формируется сигнал уровня логической

"1", устанавливающий в исходное сос1з?0660 тояние триггеры 8,.1 — 8,N и регистр 5 памяти.

В блоке 7 ключи 10.1-10,N служат для отключения от элемента 11 канала с минимальным сигналом по соответствующему управляющему сигналу, а приоритетный шифратор 12 исключает выдачу на выход блока 7 одновременно нескольких,сигналов в случае равенства или близких значений величин входных сигналов блока 7, Формула изобретения

l. Многоканальное адаптивное аналого-цифровое устройство, содержащее

N триггеров (где N — число каналов), выходы которых соединены с соответствующими входами элемента И,цифровой сумматор, регистр памяти,цифро- 20 аналоговый преобразователь, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены аналоговый коммутатор, аналогоцифровой преобразователь, N вычитате- 25 лей и блок определения канала с минимальным сигналом, управляющие входы которого объединены с выходами соответствующих триггеров, I-входы которых объединены с соответствующими 30 выходами блока определения канала с минимальным сигналом и являются шиной адреса канала, Н-входы триггеров объединены с входом установки регистра памяти и подключены к выходу элемента И, а С-входы объединены с тактовым входом регистра памяти и являются тактовой шиной, выходы аналогоцифрового преобразователя соединены с соответствующими первыми входами .. цифрового сумматора, выходы которого подключены к соответствующим входам регистра памяти, а вторые входы объединены с соответствующими входами цифроаналогового преобразователя,подключены к соответствующим выходам регистра памяти и являются выходной информационной шиной, первые входы вычитателей объединены и подключены к выходу цифроаналогового преобразователя, выходы соединены с соответствующими входами аналогового коммутатора, а вторые входы объединены с соответствующими информационными входами блока определения канала с минимальным сигналом и являются соответствующими информационными входными шинами, выход аналогового коммутатора соединен с входом аналого-цифровога преобразователя.

2. устройство по п.l, о т л ич а ю щ е е с я тем, что блок определения канала с минимальным сигналом выполнен на N ключах, приоритетном шифраторе и элементе выбора канала, входы которого подключены к выходам соответствующих ключей, а выходы соединены с соответствующими входами приоритетного шифратора, выходы которого являются выходами блока,информационными входами и входами управления которого являются одноименные входы ключей, Фис 2

1520660

Составитель В.Спиридонов

Техред Л. Сердюкова Корректор Э.Лончакова

Редактор И,Шмакова

Заказ 6769/57 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101

12У

Входы упрабления

Вью f дух.2

Вюх, A