Коммутатор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и технике связи. Его использование в системах приоритетной конференцсвязи с дельта-модуляцией позволяет повысить помехоустойчивость коммутатора, который содержит распределитель 1 импульсов, группу элементов И 2, регистр 4 сдвига, двоичные счетчики 8,9, триггер 10, элементы И 11-13, элемент ИЛИ 17 и дешифраторы 21, 22. Благодаря введению реверсивного счетчика 3, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элементов НЕ 6,7, элементов И 14-16, элементов ИЛИ 18-20, дешифратора 23, цифровых компараторов 24,25 и источников 26,27 постоянного кода в коммутаторе обеспечивается безошибочное и устойчивое занятие канала активным абонентом. 3 ил.

CO)03 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) Г

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 441 6525/24-24 (22) 26.04.88 (46) 07.11 .89.Бюл, М 41 (71) Рижский политехнический институт им.А.Я.Пельше (72) Г,Н.Котович, И.О. Флейшман и И.М,Малашонок (53) 621.395 .34 (088. 8) (56) Авторское свидетельство СССР

N- 1021017, кл. Н 04 М 3/56, 1981.

Авторское свидетельство СССР

11 1297229, кл. Н 03 М 3/02, 1985. (54) КОММУТАТОР (57) Изобретение относится к вычислительной технике и технике связи. Его использование в системах приоритетной (51) 4 Н 03 M 3/02 Н 04 М 3/56

2 конФеренцсвязи с дельта-модуляцией позволяет повысить помехоустойчивость коммутатора, который содержит распределитель 1 импульсов, группу элеме()тов И 2, регистр 4 сдвига, двоичные счетчики 8,9, триггер 10, элементы И 11-13, элемент ИЛИ 17 и дешифраторы 21,22, Благодаря введению реверсивного счетчика 3, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элементов НЕ 6, 7, элементов И 14-16, элементов

ИЛИ 18-20, дешифратора 23, цифровых компараторов 24,25 и источников 26, 27 постоянного кода в коммутаторе обеспечивается безошибочное и устойчивое занятие канала активным абонентом. 3 ил .

1520664

15

Изобретение относится к вычисли— тельной технике и технике связи и может использоваться в системах приоритетной конференцсвязи с дельтамодуляцией (ДМ).

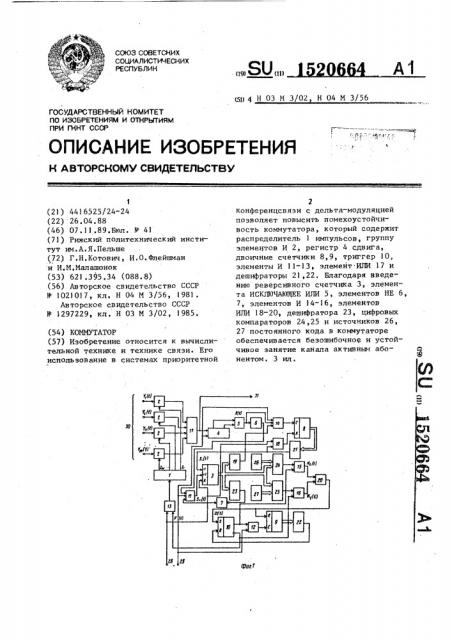

Цель изобретения — повышение помехоустойчивости коммутатора, На фщ, 1 приведена функциональная схема коммутатора; на фиг.2 и 3 — временные диаграммы работы коммутатора.

Коммутатор содержит распределитель 1 импульсов, группу элементов

И 2, реверсивный счетчик 3, регистр

4 сдвига, элемент ИСКЛОЧЙОЩЕЕ ИЛИ 5, первый 6 и второй 7 элементы НЕ, первый 8 и второй 9 двоичные счетчики, триггер 10, первый — шестой элементы И 11-16, первый — четвертый элементы ИЛИ 17-20, первый — третий дешифраторы 21 — 23, первый 24 и второй 25 цифровые компараторы и первый 26 и второй 27 источники постоянного кода, которые могут быть реализованы, например, на ПЗУ. На фиг.l обозначены вход 28 синхронизации, тактовый вход 29, информационные входы 30 и выход 31.

На фиг.2 и 3 обозначены: а — последовательность импульсов с частото f на входе распределителя 1; б — последовательность тактовых импульсов с частотой f на входе 29; в,г — сигналы Х„, Х на выходах распределителя 1; д — ДМ-поаледовательность Y „(t) на выходе 31; е — сиг" нал Я q(t) на выходе первого элемента И 11 (на суммирующем входе счетчика 3);,ж — сигнал S (t) на выходе первого дешифратора 21 (на вы- . читающем входе счетчика 3); з,и " сигналы K„(t) и К (t) на выходах соответственно шестого 16 и пятого

l5 элементов И; к — сигнал D(t) на выходе четвертого элемента ИЛИ 20, (на S-входе триггера 10); л — сиг-нал на инверсном выходе триггера 1.0.

Коммутатор работает следующим образом.

ДМ-сигналы У,(й)-Y (t) с выходов кодеров абонентов поступают на входы 30 и через элементы И 2 по очереди поступают на выход первого элемента ИЛИ 17, а с него — на информационный вход регистра 4, В случае, когда все абоненты пассивны, сигналы У (t)-Y (t) представляют собой последовательность импульсов вида

55...101010..., которые, записавшись в регистр 4, не вызывают изменения сигнала на выходе элемента ИСКЛОЧАЮЩЕЕ ИЛИ 5. Реверсивный счетчик 3 находится в нулевом состоянии, на выходе элемента ИЛИ 19 нулевой потенциал, кото рый зап рещае т работу пе рвого счетчика 8.

В этом режиме триггер 10 находится в нулевом состоянии и единичный логический потенциал F(t) (фиг.2 л) . на его инверсном выходе не препятствует прохождению импульсов с тактового входа 29 через элемент И 13 на вход распределителя 1 импульсов. Импульсы последовательности f,(ôèã.2), поступая на вход распределителя 1, вызывают поочередное появление единичных (разрешающих) сигналов Х; на его выходах в любом установленном порядке по циклу.

При проявлении каким-либо абоненФ том активности в ДМ-последовательности У;(t) (фиг.2 д) появляются двух- и более элементные пачки, что вызывает появление единичных импульсов на выходе первого элемента

НЕ 6.

Эти импульсы поступают на вход элемента И 11, на другой вход которого поступает тактовая последовательность (фиг. 2б). На третий вход элемента И и через второй элемент

НЕ 7 подключен выход дешифратора 23, который выделяет определенную комбинацию на выходе реверсивного счетчика 3. Пока такая комбинация не появилась,,на выходе дешифратора

23 — логический "0", а на третьем входе элемента И 11 — логическая "1".

Таким образом, в моменты появления двух- и более элементных пачек в

ДМ-последовательности Y (t) единичные импульсы S (t) (фиг,2 е) поступают на суммирующий вход реверсивного счетчика 3 и увеличивают его состояние, оуо ое становится отличньпк от нулевого. Это приводит к

1 тому, что на выходе элемента ИЛИ 19 появляется единичный уровень„ который сохраняется, пока состояние реверсивного счетчика 3 отлично от нулевого. Единичный уровень на выходе элемента ИЛИ 19 определяет. единичный уровень на одном из входов элемента И 14, на другой вход которого заведен сигнал R(t) с выхода элемента ИСИПОЧА1ОЩЕЕ ИЛИ 5, где — К

B =

5 15 единичный уровень появляется при отсутствии в ДМ вЂ последовательнос

Y»(t) двух- и более элементных пачек.

В такие моменты времени на вход пер1 ваго счетчика 8 проходят импульсы тактовой последовательности, Счетчик 8 считает до тех пор, пока на выходе первого дешифратора 21 не появится единичный импульс S (t) (фиг.2 ж), который поступает на вычитающий вход реверсивного счетчика 3 и уменьшает его состояние на единицу. Этот же импульс с выхода дешифратора 21 поступает через элемент ИЛИ 18 на установочный вход первого счетчика 8 и сбрасывает его.

Комбинация, выделяемая дешифратором

21, выбрана так, что при активности абонента на нижней границе динамического диапазона количество импульсов, приходящих на суммирующий вход реверсивного счетчика 3, равно количеству импульсов, приходящих на

его вычитающий вход. Среднюю плотность цифрового сигнала R(t) на выходе элемента 5 можно оценить как где К вЂ” число нулевых пачек;

L — число импульсов тактовой последовательности f т

Величина В на практике всегда известна (В = 0,05-0,2) и зависит от структуры используемых в системе дельта-кодеков.

Таким образом, если активность абонента поднимается выше нижней границы динамического диапазона, то количество единичных импульсов S >(t) на суммирующем входе реверсивного счетчика 3 превышает количество единичных импульсов $ (t) на его вычитающем входе и состояние реверсивного счетчика 3 увеличивается. Это состояние сравнивается вторьи цифровым компаратором 25 с числом от источника ,27. Когда состояние реверсивного счетчика 3 превысит это число, на

"выходе второво цифрового компаратора

25 появляется единичный уровень, который устанавливается на входе элемента И 16, на другом входе которого присутствует единичный уровень с инверсного выхода триггера 10. Таким образом, единичный уровень К,(t) (фиг.2з) через элемент ИЛИ 20 проходит на S-вход триггера 10 — сиг20664 6 нал I)(t) (фиг. 2 к) и перебрасывает его в единичное состояние. На инверсном выходе триггера 10 появляется нулевой уровень F(t) (фиг.2л) и прекращает прохождение последовательности f. через элемент И 13 на распределитель 1 импульсов. Таким образом, канал занят.

В то же время единичный уровень на выходе триггера 10 появляется на втором входе элемента И 15. Первый» цифровой компаратор 24 сравнивает состояние реверсивного счетчика 3 с числом, подаваемым с первого источника 26 постоянного кода, причем это число меньше числа» подаваемого с второго источника 27, т.е. единичный уровень на выходе первого циф20 рового компаратора 24 появляется раньше, чем на выходе второго цифрового компаратора 25, При появлении единичного уровня на втором входе элемента И 15 на его выходе также по25 является единичный уровень К { ) (фиг ° 2 и) и через элемент ИЛИ 20 проходят на S-вход триггера 10. Более низкий порог срабатывания первого цифрового компаратора 24 выбран

30 для того, чтобы канал после занятия

его абонентом был устойчивым и обеспечивал некоторый запас устойчивости в паузах речи активного абонента.

При возрастании активности абонента состояние реверсивного счетчика

3 увеличивается до тех пор, пока на

35 выходе дешифратора 23 не появится единичный импульс, который через втО" рой элемент НЕ 7 запрещает прохожде40

О йие единичных импульсов f с входа

29 на суммирующий вход реверсивного счетчика 3. Состояние, выделяемое дешифратором 23, несколько превышает порог срабатывания второго цифрового

5 компаратора 25 ° Таким образом,. пока . абонент активен, состояние реверсивного счетчика 3 колеблется от порога срабатывания первого .цифрового компаратора 24 до состояния, выделяемого дешифратором 23. Благодаря этому исключены ситуации, когда реверсив., ный счетчик 3 переходит из нулевого состояния в единичное на всех выхо.дах или из единичного в нулевое за

55 один такт.

Отпускание канала происходит следующим образом. Если абонент перестает проявлять активность, состояние реверсивного счетчика 3 уменьшается.

1520664

При достижении порога первого цифрового компаратора 24 на его выходе появляется нулевой уровень (фиг.Зк), который поступает на S-вход триггера

10 и на установочный вход второго

5 счетчика 9, Триггер 10 находится в единичном состоянии, и импульсы тактовой последовательности (фиг.Зб) через элемент И 12 проходят на счетный вход второго счетчика 9, который считает до тех пор, пока на выходе дешифратора 22 не появится единичный уровень . Время счета счетчика 9— . это время отпускания канала (около 150 мс). Появление единичного уров ня на выходе дешифратора 22 вьиывает переброс триггера 10 в нулевое состояние и единичный уровень D(t) (фиг,3 л) на инверсном выходе триггера 10 разрешает прохождение последовательности через элемент И 13 на вход распределителя 1 импульсов. Если зафиксированный абонент в течение времени счета импульсов вторым 25 счетчиком 9 продолжает проявлять активность, то на выходе элемента

ИЛИ 20 появляется единичный уровень

D(t), вызывающий переброс триггера IO

10 в единичное состояние, а также 30 сброс второго счетчика 9.

Очевидно„ что при такой структу ре устройства, зафиксированный за активным абонентом канал надежно удерживается до тех пор, пока данный абонент проявляет активность.

Время занятия канала определяется выбранными параметрами элементов схемы: комбинацией, выделяемой первым дешифратором 21, и порогом второго цифрового компаратора 25 .(время занятия выбирается порядка

3-5 мс на нижней границе динамичес кого диапазона кодера) °

При этом каждый импульс последовательности К переводит первый счетчик 8 и реверсивный счетчик 3 в нулевое состояние, таким образом исключается возможность в отличие от изВестного коммутатора занятия канала следующим по порядку сканирования абонентом.

Ф о рм у л а и 3 о б р е т е н и я

1(оммутатор, содержащий группу элементов И первые входы которых

Ф

55 являются соответствующими информационными входами коммутатора, выходы элементов И группы подключены к со— ответствующим входам первого элемента ИЛИ, выход которого соединен с информационным входом регистра сдвига и является выходом коммутатора, тактовый вход регистра сдвига объединен с первыми входами первого и второго элементов И и является тактовым входом коммутатора, пррвый двоичный счетчик, выходы которого подключены к входам первого дешифратора, выход второго элемента И соединен со счетным входом второго двоичного счетчика, выходы которого подключены к входам второго дешифратора, выход которого соединен с

R-входом триггера, прямой и инверсный выходы которого подключены соответственно к второму входу второго элемента И и к первому входу третьего элемента И, второй вход которого является входом синхронизации коммутатора, выход третьего элемента И подключен к входу распределителя имг(ульсов, выходы которого соединены с вторыми входами соответствующих элементов И группы, S-вход триггера объединен с входом обнуления второго двоичного счетчика, о т л и ч а юшийся тем, что, с целью повыше ния помехоустойчивости коммутатора, в него введены реверсивный счетчик, цифровые компараторы, элементы НЕ, элемент ИСЮ00ЧАЮЩЕЕ ИЛИ, третий дешифратор, четвертый — шестой элементы И, второй — четвертый элементы

ИЛИ и первый и второй источники постоянного кода, выхода которых соединены с первыми входами одноименных цифровых компараторов, выходы которых подключены к первым входам соответственно пятого и шестого элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам триггера, выходы пятого и шестого элементов И соединены с входами четвертого элемента

ИЛИ, выход которого подключен к

S-входу триггера, выходы первого и второго разрядов регистра сдвига соединены с входами элемента ИСИПО- .

ЧАМЩЕЕ ИЛИ, выход которого через первый элемент НЕ и непосредственно подключен соответственно к второму входу первого элемента И и к первому входу четвертого элемента И, второй вход которого подключен к тактовому входу коммутатора, выход первого элемента И соединен с суммирующим входом реверсивного счетчи1520664

Фие. г

- ка, вход обнуления которого объединен с первым входом второго элемента . ИЛИ и подключен к входу синхронизации коммутатора, выходы реверсивного

5 счетчика соединены с вторыми входамн цифровых компараторов и с входами третьих дешифратора и элемента ИЛИ, выходы которьгх соответственно череФ второй. элемент НЕ и непосредственно подключены к третьим входам соответственно третьего и четвертого элементов И, выход перного дешифратора соединен с вычитаю- щнм входом реверсивного счетчика и вторым входом второго элемента ИЛИ, выход которого и выход четвертого элемента И подключены соответственно к входу обнуления н счетному входу первого двоичного счетчика.

1520664

Составитель О. Ревинский

Редактор И„Шмякова Техред Л.Сердюкова

Корректор С.черни

Заказ 6769/57 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101