Преобразователь изменения сопротивления в выходной сигнал

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может быть использовано для преобразования в цифровой код сигналов тензои терморезисторов, а также других датчиков, сопротивление которых изменяется под действием входного измеряемого физического параметра. Цель изобретения - повышение точности за счет ограничения саморазогрева рабочего и компенсационного резисторов проходящим через них током и устранения влияния на выходной сигнал переходных процессов в ключах. Это достигается введением одного RS- и трех счетных триггеров 20, 21, 22 и 23, цепи из последовательно соединенных диода 24 и конденсатора 25, шести элементов И 26, 27, 28, 29, 30 и 31, элемента И-НЕ 32, инвертора 33, элемента ИЛИ 34, элемента 35 задержки с двумя выходами, предназначенными для формирования двух разных временных интервалов, двух аналоговых запоминающих устройств 36 и 37, сумматора 38 и аналого-цифрового преобразователя 39, а также выполнением ключей 3, 4, 5 и 6 электронными, вследствие чего из сигнала на выходе первого операционного усилителя 8 вырезаются и запоминаются участки лишь в те интервалы времени, которые не включают в себя переходные процессы на ключах 3, 4, 5 и 6, а большая скважность питающих рабочий и компенсационный резисторы 1 и 2 импульсов переменной полярности снижает среднюю рассеиваемую на этих резисторах мощность. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1522024

А1 цц4 С 01 В 7/16

ВМОЮЗРМ

ВЫПЬ 1ск!ЬЧЗЫЯ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ фтр фие

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЬГГИЙМ

ПРИ ГКНТ СССР

1 (21) 4333700/25-28 (22) 04.09.87 (46) 15.11.89. Бюл. Р 42 (71) Институт технической теплофизики АН УССР (72) В.В.Шейко, А.В.Примак, А.М.Здоровец и В.Ю.,Александров (53) 531.781.2.(088.8) (56) Авторское свидетельство СССР

Р 678271, кл. G 01 В 7/16, 1977.

Авторское свидетельство СССР и 1265465, кл. G 01,B 7/16, 1985. (54) ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ В ВЫХОДНОЙ СИГНАЛ . (57) Изобретение относится к измерительной технике и может быть использовано для преобразования в цифровой код сигналов тензо- и терморезисторов, а также других датчиков, со-. противление которых изменяется.под действием входного измеряемого физического параметра. Цель изобретения повышение точности за счет ограничения саморазогрева рабочего и компенсационного резисторов проходящим через них током и устранения влияния

2 на выходной сигнал переходных процессов в ключах. Это достигается введением RS- и трех счетных триггеров

20, 21, 22 и 23, цепи из последовательно соединенных диода 24 и конденсатора 25, шести элементов И 26, 27, 28, 29, 30 и 3 1, элемента И-НЕ 32, инвертора ЗЗ, элемента ИЛИ 34, элемента 35 задержки с двумя выходами, предназначенными для формирования двух разных временных интервалов, двух аналоговых запоминающих устройств 36 и 37, сумматора 38 и аналого-цифрового преобразователя 39, а также вы. полнением ключей 3, 4, 5 и 6 электронными, вследствие чего из сигнала на выходе первого операционного усилителя 8 вырезаются и запоминаются участки лишь в те интервалы времени, которые не включают в себя переход ные процессы на ключах 3, 4, 5 .и 6, а большая скважность питающих рабочий и компенсационный резисторы 1и 2 импульсов переменной полярности снижает среднюю рассеиваемую на этих резисторах мощность, 2 ил.

1522024

Изобретение относится к измерительной технике и может быть использовано для преобразбвания в цифровой код сигналов тензо- и термо5 резисторов, а также других датчиков, сопротивления которых изменяются под действием входного измеряемого физического параметра.

Цель изобретения — повышение точности путем ограничения саморазогрева рабочего и компенсационного резисторов проходящим через них током и устранения влияния на выходной сигнал переходных процессов в ключах.

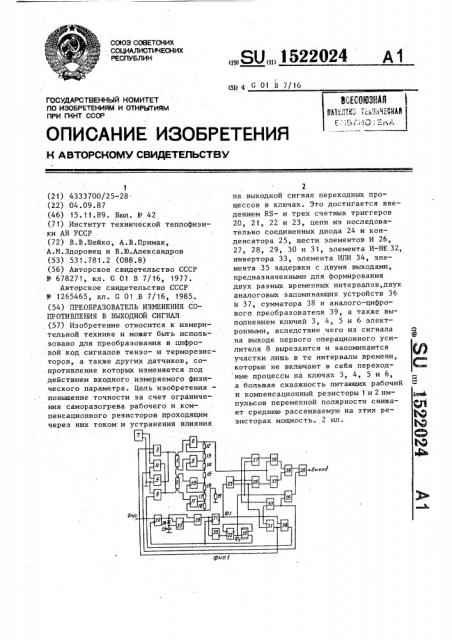

На фиг.1 представлена схема преобразователя; на фиг.2 — .временная диаграмма работы его блоков.

Преобразователь изменения сопротивления в выходной сигнал содержит 20 рабочий и компенсационный резисторы

1 и 2 с питающими и информационными выводами, на обоих концах, четыре ключа 3-6 каждый иэ которых имеет ,основной и управляющий входы и вы- 25 ход, источник 7 стабилизированного тока с двумя шинами, четыре опера.— ционных усилителя 8-11„ цепочку из восьми прецизионных резисторов 12-19, один RS и три счетных триггера 20-23, цепь из последовательно соединенных диода 24 и конденсатора 25, шесть элементов И 26-3 1, один элемент И-НЕ

32, один инвертор 33, один элемент

ИЛИ 34, один элемент 35 задержки с

35 двумя выходами, предназначенными для формирования двух разных временных интервалов,- два аналоговых запоминающих устройства 36 и 37, один сумматор 38 и один аналого-цифровой пре40 обраэователь 39. Ключи 3-6 выполнены электронными. Первые питающие выводы рабочего и компенсационного резисторов 1 и 2 соединены между собой ° Одна из шин источника 7 стабилизированного тока соединена с основными входами первого и второго ключей 3 и 4, а другая — с основными входами третьего и четвертого ключей 5 и 6.

Выходы первого и третьего ключей 3 и 5 соединены с вторым питающим выводом рабочего резистора 1, а выходы второго и четвертого ключей 4 и 6 с вторым питающим выводом компенсационного резистора 2. Первые входы

55 операционных усилителей 8-11 соединены соответственно с информационными выводами рабочего и компенсационного резисторов 1 и 2. Начало и конец цепи из прецизионных резисторов 12

19 соединены соответственно с выходом первого усилителя 8 и общей шиной преобразователя, а общие точки каждых двух последующих прецизионных резисторов соединены соответственно нечетные — со вторым входом соответствующего уснлителя, а четные — с выходом следующего за ним усилителя.

Выход RS-триггера 20 соединен с первыми входами элемента И-НЕ 32 и первого элемента И 26 и свободным выводом диода 24. Общая точка диода 24 и конденсатора 25 соединена с другим входом элемента И-НЕ 32. Выход элемента И-HE 32 соединен с другим входом первого элемента И 26. Выход первого элемента И 26 соединен со счетным входом первого счетного триггера

21 и входом инвертора 33, выход которого соединен со счетным входом второго счетного триггера 22, выходом соединенного с входом элемента 35 задержки и первыми входами элементов

И 27-29. Первый выход элемента 35 задержки соединен с установочным входом второго счетного триггера 22, а второй — с установочными входами

RS-триггера 20 и первого счетного триггера 21. Выход первого счетного триггера 21 соединен со счетным входом третьего счетного триггера 23 и первыми входами элемента ИЛИ 34 и элементов И 30 и 31. Прямой выход третьего счетного триггера 23 соединен с вторыми входами элементов И 28 и 31, à его инверсный выход — с вторыми входами и элементов И 27 и 30.

Ъ

Информационные входы запоминающих устройств 36 и 37 соединены с выходом первого усилителя 8, управляющие входы — с выходами элементов И 27 и 28, а выходы — с входами сумматора 38. Выход элемента И 31 соединен с вторым входом элемента ИЛИ 34 и управляющим входом первого ключа

3. Выход элемента ИЛИ 34 — связан с управляющим входом четвертого ключа 6. Выход пятого элемента И 30 соединен с вторым входом элемента И

29 и управляющими входами ключей 4 и 5. Информационный и управляющий вывходы аналого-цифрового преобразователя 39 соединены соответственно с выходами сумматора 38 и четвертого элемента И 29, а свободный вывод конденсатора 25 соединен с общей шиной преобразователя.

Преобразователь изменения сопротивления в выходной сигнал работает следующим образом.

В момент включения питания вырабатывается сигнал "Сброс", устанавливающий триггеры 20-23 в нулевое состояние. Затем на внешний управляющий вход подаются короткие управляющие импульсы U (ôèã.2) . По каждому управляющему импульсу формируются импульсы Ф1 и Ф2 (фиг.2) . До момента воздействия входного управляющего импульса выход триггера 21 (шина Ф1 на фйг.1) и выход триггера 22 (шина

Ф2 на фиг.1) находятся в состоянии

"0". По переднему фронту (фиг. 2) управляющего импульса срабатывает

RS-триггер 20, а счетный триггер 21 устанавливается в "1", Так формиру- 20 ется передний фройт импульса Ф1. При этом формирователь короткого импульса, собранный на элементах 32 и 26 с подключенной к входам И-НЕ 32 це-. почки из диода 24 и конденсатора 25 25 формирует на выходе элемента И 26 импульс требуемой длительности, которая регулируется с помощью подбора величины емкости конденсатора 25.

Эта дл ятельность обеспечивает .задерж- 30 ку в формировании переднего фронта импульса Ф2.относительно переднего фронта импульса Ф1 и определяется длительностью переходных Процессов в нагрузке источника 7 стабилизированного тока — на резисторах 1 и 2.

По переходу в "0" сигнала на выходе. элемента И 26 триггер 22 устанавли- вается в "1, чем определяется передний фронт импульса Ф2. Длитель- 40 ность импульса Ф2 устанавливается с помощью элемента 35 задержки и определяется временем, необходимым для запоминания полезного сигнала аналоговыми запоминающими устрой- 45 ствами 36 и 37. По истечении требуемого времени задержки первый выход элемента 35 задержки устанавливается в "0", соответственно сбрасывается триггер 22, формируя задний фронт импульса Ф2. С некоторой задержкой устанавливается состояние

"0" и на втором выходе элемента 35 задержки, чем сбрасываются триггеры 20 и 21. С помощью счетного триггера 23 и комбинационной логики, собранной на элементах 27-31 и 34 осуществляется управление аналоговыми ключами 3-6, запоминающими устрой1522024 ствами 36 и 37 и аналого-цифровым преобразователем 39 (фиг. 2) . В паузе сигналов Ф1 ключи 4 и 5 закрыты, т.е. питающий ток по резисторам 1 и 2 не проходит. Скважность определяетл

l ся отношением — где с — длительТ ность фазового импульса Ф1, а Т вЂ” период следования управляющих импульсов, причем i. (сТ.

По переднему фронту импульса Ф1 счетный триггер 23 устанавливается в состояние " 1", открывается ключ 3, а по переднему фронту управляющего сигнала — ключ 6. При этом первая шина источника 7 стабилизированного тока подключается к рабочему резистору 1, а вторая шина через ключ 6 остается подключенной к компенсационному резистору 2. В таком положении подключена указанная нагрузка к источнику тока на временном интервале импульса Ф1. По сигналу записи, формирующемуся на выходе элемента

И 28, аналоговый сигнал с выхода усилителя 8 заносится в аналоговое saпоминающее устройство 28 и запомина ется в нем. Длительность сигнала записи соответствует длительности фазового импульса Ф2. На временном интервале Ф2 аналоговый сигнал U на выходе усилителя .8 соответствует значению 0 skit 2 uvn(Rgt к $2) где Й q и R - сопротивления резисут торов 1 и 2.

По окончании импульса Ф1 ключ 3 закрывается, т.е. нагрузка отключается от источника 7 стабилизированного тока.

Через временной интервал Т на управляющий вход преобразователя поступает следующий управляющий импульс.

С этого .момента начинается второй такт работы преобразователя. При этом ключ 6 закрывается, а ключи 4 и 5 по управляющему сигналу, формирующемуся в течение длительности импульса Ф1 на выходе элемента И 30, открываются и переключают по сравнению с первым тактом направление тока в нагрузке.

На временном интервале импульса Ф2, аналоговый сигнал значения 21„ „/К,—

-В запоминается аналоговым запоминающим устройством 27. По окончании импульса Ф2 на выходе сумматора 38 формируется аналоговый сигнал уровня .41„„,„(R > -R>.). В этот момент на выходе элемента И 29 формируется сиг1522024 нал запуска аналого-цифрового преобразователя 39, с помощью которого аналоговый сигнал 4I„ „(R>,-R><) преобразуется в код, соответствующий информации о величине текущего значения соответствующего физического параметра, например температуры или де=формации.

Преобразователь позволяет при миf0 нимальных аппаратурных затратах и низкой себестоимости комплектующих элементов практически исключить погрешности резистивных датчиков, обусловленные током разогрева резистора .Э н воздействием переходных процессов в результате переключения направления питающего тока.

Формула изобретения

Преобразователь изменения сопротивления в выходной сигнал, .содержащий рабочий и компенсационный резисторы с питающими и информационными выводами на обоих концах, первые питающие выводы. рабочего и компенсационного резисторов соединены между собой, четыре ключа, каждый из которых имеет основной и управляющий входы и выход, выходы первого и третьего ключей соединены с вторым питающим выводом рабочего резистора, а выходы в-.срого и четвертого ключей — с вторым питающим выводом компенсационного резистора, источник стабилизированного тока с двумя шинами, одна из которых соединена с основными входами первого и второго ключей, а другая — с основными входами третьего и четвертого ключей, четыре операционных усилителя, первые входы которых соединены соответственно с информационными выводами рабочего и компенсационного резисторов, цепочку из восьми прецизионных резисторов, начало и конец которой соединены соответственно с выходом первого усилителя и общей шиной преобразователя, а общие точки каждых двух последующих прецизионных резисторов соединены соответственно нечетные — с вторым входом соответствующего усилителя, а четные .с выходом следующего за ним усилителя, отличающийся тем, что, с целью повышения точности за счет ограничения саморазогрева рабочего и компенсационного резисторов проходящим через них током и устранения влияния на выходной сигнал переходных процессов в ключах,. он снабжен RS-триггером и тремя счетными триггерами, цепью из последовательно соединенных диода и конденсатора, шестью элементами И, элементом И-НЕ, инвертором, элементом ИЛИ, элементом задержки с двумя выходами, предназначенными для формирования двух разных временных интервалов, двумя аналоговыми запоминающими устройствами, сумматором и аналого-цифровым преобразователем,ключи выполнены электронными, выход RS-триггера соединен с первыми входами элемента И-НЕ и первого элемента И и свободным выводом диода, общая точка диода и конденсатора соединена с другим входом элемента И-НЕ, выход элемента И-НЕ соединен с другим входом первого элемента И, выход которого соединен со счетным входом первого счетного триггера и с входом инвертора, выход инвертора соединен со счетным входом второго счетного триггера, выход которого соединен с входом элемента задержки и с первыми входами второго, третьего и четвертого элементов И, первый выход элемента задержки соединен с установочным входом второго счетного триггера, а второй — с установочными входами RS-триггера и первого счетного триггера, выход.первого счетного триггера соединен со счетным входом третьего счетного триггера и с первыми входами элемента ИЛИ и пятого и шестого элементов И, пря мой выход третьего счетного триггера соединен с вторыми входами третьего и шестого элементов И, а его инверсный выход — с вторыми входами второго и пятого элементов И, информационные входы запоминающих устройств соединены с выходом первого усилителя, управляющие входы — соответственно с выходами второго и третьего элементов И, а выходы — с входами сумматора, выход шестого элемента И соединен с вторым входом элемента

ИЛИ и с управляющим входом первого ключа, выход элемента ИЛИ вЂ” с управляющим входом четвертого ключа, I выход пятого элемента И соединен с вторым входом четвертого элемента И и управляющими входами второго и третьего ключей, информационный и управляющий входы аналого-цифрового преобразователя соединены соответст1522024

Qynp

Составитель Н.Тимошенко

Редактор Л.Пчолинская Техред М.Ходанич Корректор A. РУ Р

А.Об ча

Заказ 6948/37 Тирах 683 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Óêãîðîä, ул. Гагарина, 101 венно с выходами сумматора и четвертого злемента И, а свободный вывод

1 конденсатора соединен с общей шиной преобразователя.