Устройство для извлечения квадратного корня

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в специализированных и универсальных быстродействующих цифровых вычислительных машинах. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что для вычисления квадратного корня используется формула Герона для двух итераций, в которой начальное приближение выбирается из блока памяти при помощи К старших разрядов аргумента. 1 ил.

СОЮЗ СОВЕтСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

09) 01) (gg 4 G 06 F 7/552

8 ЕСОЕЕа

ПАТГИТИО- TEXRN%

Е::: сэ ;.Иа ТЕК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

Щ

1 х 1 г х

2() 2() rx -1/2(у, + )

У1

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И 01НРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4374101/24-24 (22) 02.02 ° 88 (46) 15 ° 11.89 Бюл.У 42 (71) Институт кибернетики им. В.И..Глушкова (72) В.Д.Троц, Я.Е.Визор, Н.А.Наза-рук и M.Â.Ïèòöûê (53) 681.325(088.8) (56) Авторское свидетельство СССР

9 611208, кл. G 06 F 7/552, 1978.

Авторское свидетельство СССР

У 957209, кл. G 06 F 7/552, 1980.

Изобретение относится к вычислительной технике и может быть использовано в специализированных и универсальных быстродействующих цифровых вычислительных машинах.

Целью изобретения является сокращение аппаратурных затрат..

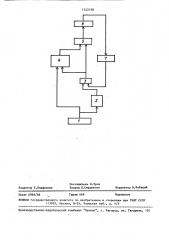

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит регистр 1 подкоренного выражения, блок 2 памяти, коммутатор 3, блок 4 деления, сумматор 5, блок 6 сдвига, регистр

7 результата.

Вычисление значения функции у =

1х производится на основе формулы Герона для двух итераций с начальными условиями у

2 (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ (57) Изобретение относится к вычислительной технике и может быть использовано в специализированных и универсальных быстродействующих цифровых вычислительных машинах. Целью изобре тения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что для вычисления квадратного корня используется формула

Герона для двух итераций, в которой начальное приближение выбирается из блока памяти при помощи К старших разрядов аргумента. 1 ил. дпя нормализованных значений аргумента, лежащих в интервале 1/4 < х а 1, погрешность которого оценивается выражением R < (h x/, причем х +

+ Ьх, где х0 — число, образованное

k старшими разрядами аргумента; gхчисло, образованное и-Е младшими . разрядами аргумента; и - число разрядов для определения представления аргумента х.

Устройство работает следующим образом.

Значение аргумента хранится в .регистре 1 подкоренного выражения. В . первом такте работы значение х с выхо- да регистра 1 подкоренного выражения подается на первый вход блока 4 деления, а k старших разрядов аргумента

1522198 х подаются на адресные входы блока

2 памяти, с которого снимается значение Гх, которое через коммутатор 3 подается на второй вход блока 4 деле5 ния и на второй вход сумматора 5. На выходе делителя получаем первый промежуточный результат

Р ГЗ(°

1О

Во втором такте промежуточный результат на сумматоре 5 складывается со значением õ . Полученная сумма сдвигается в блоке 6 сдвига на один 15 разряд вправо с записью в старший разряд значения "О" при записи в ре-.. гистр 7 результата. На выходе регист» ра результата 7 получается второй про-.межуточный результат 20 р -(х +р ) =-(!х + — -) ! 1 х

2 о 1 2 хо с2 У °

В третьем такте второй промежуточный результат поступает через коммута» тор 3 с регистра 7 результата на второй вход блока 4 деления и на вто рой вход сумматора 5. В это же время иэ регистра 1 подкоренного выражения на первый вход блока деления 4 подается значение аргумента х, на выходе которого получается третий промежуточный результат 35 х х

1 у1 pg.

В четвертом такте результат суммирования рэ + х, nîëó÷åííûé на сумматоре 5, сдвигается вправо на один разряд в блоке 6 сдвига, с записью значения "О" в старший разряд при записи в регистр 7 результата. В результате выполнения перечисленных операций, в регистре 7 результата получится искомое значение х ,Г

1 х х -(y + — ), 2

Формула изобретения

Устройство для извлечения квадрат" ного корня, содержащее регистр результата, блок деления, регистр подкоренного выражения, блок памяти, выход которого соединен с информационным входом коммутатора, а входс выходом регистра подкоренного выражения, выход коммутатора подклю".

"чен к первой группе входов сумматора о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурпых затрат, выход регистра лодкоренного i выражения соединен с первым входом блока деления, второй вход и выход которого подключены соответственно к выходу коммутатора и второй группе входов сумматора, выход которого через блок сдвига соединен с входом регистра результата, выход которого подключен к управляющему входу комму-. татора.

)522198

Составитель В. Троц

Техред Л. Сердюкова

Редактор T,Ïàðôåíoâà

Корректор В.Кабаций

Заказ 6964/46 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101