Устройство для ввода дискретных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в составе ЭВМ, в автоматизированной системе сбора и обработки дискретной информации, работающей в режиме реального времени. Целью изобретения является повышение достоверности вводимой информации. Устройство содержит канальные приемники 1, канальные передатчики 2, канальные приемопередатчики 3, блок 4 управления, селектор 5 адреса, компаратор 6 адресов, программируемый таймер 7, генератор 8 импульсов, регистр 9 состояния, блок 10 гальванической развязки, элемент 2И-НЕ 11, УК-триггер 12, блок 13 прерывания. Регистр 9 состояния содержит первый Д-триггер 14, второй Д-триггер 15, элемент И 16 и элемент ИЛИ 17. Указанная цель достигается за счет введения элемента 2И-НЕ 11, УК-триггер 12 прерывания, блока 13 прерывания, а регистр 9 состояния содержит первый Д-триггер 14, второй Д-триггер 15, элемент И 16 и элемент ИЛИ 17. 4 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК псе С 06 Р 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4397418/24-24 (22) 01.02.88 (46) 15.11.89. Бкл. N 42 (71) Областное производственное объII единение горэлектротранспорта ДонецкII горэлектротранс (72) А.Е. Злачевский (53) 681.327(088,8) (56) Торгов Ю.И. Программируемый таймер KP 5ф0 ВИ 53 и его применение.

Микропроцессорные средства и системы.

1984, N 1, с. 80.

Буров Н.Н., Гаврилов Е.В. Устройство связи с объектом для управления непрерывными процессами, — Приборы и системы управления, 1987, Р 5, с.31, 32. (54) УСТРОЙСТВО ДЛЯ ВВОДА ДИСКРЕТНЫХ

СИГНАЛОВ (57) Изобретение относится к вычислительной технике и может быть использовано в составе ЭВМ, в автоматизиро„„SU„„1522223 A 1

2 ванной системе сбора и обработки дискретной информации, работающей в режиме реального времени. Целью изобретения является повышение достоверности вводимой информации. Устройство содержит канальные приемники 1, канальные передатчики 2, канальные приемопередатчики 3, блок 4 .управления, селектор 5 адреса, компаратор 6 адресов, программируемый таймер 7, генератор 8 импульсов, регистр 9 состояния, блок 10 гальванической развязки, элемент 2И-НЕ 11, 1К-три1 гер 12, блок 13 прерывания. Регистр 9 состояния содержит первый В-триггер 14 второй D-. триггер 15, элемент И 16 и элемент

ИЛИ 17 ° Указанная цель достигается за счет введения элемента 2И-HE 11, IKтриггера 12 прерывания, блока 13 прерывания, а регистр 9 состояния содержит первый D-триггер 14, второй Dтриггер !5, элемент И 16 и элемент

ИЛИ 17. 4 ил.

1522221

Изобретение относится к вычислительной технике и может быть использовано в составе ЭВМ, имеющих канал

МПИ (Электроника-60" ДВК), в автоматизированной системе сбора и обработки дискретной информации, работающей в режиме реального времени.

Цель изобретения — повышение достоверности вводимой информации.

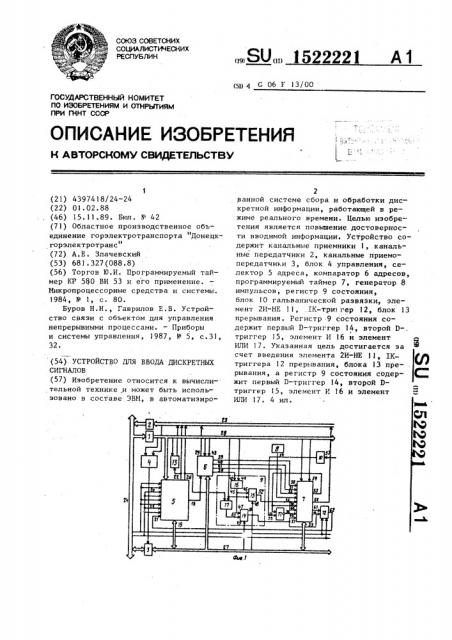

На фиг. 1 представлена схема устройства; на фиг. 2 — формат регистра состояния; на фиг. 3 — организация программируемой двухпороговой селекции по длительности вводимых дискрет- 15 ных сигналов; на фиг. 4 — пример схем1 ной реализации блока прерывания.

Устройство (см. фиг. 1) содержит канальные приемники 1, канальные передатчики 2, канальные приемо-передатчики 3, блок 4 управления, селектор 5 адреса, компаратор 6 адресов, программируемый таймер 7, генератор 8 ! импульсЬв, регистр 9 состояния, блок 10 гальванической развязки, эле- 2 мент 2И-НЕ ll, IK-триггер 12, блок 13 прерывания, первый 0-триггер 14, второй D-триггер 15, элемент И 16 и элемент ИЛИ 17.

На фиг. 1 позициями 18-63 обоэна30 чены позиции входов и выходов блоков, составляющих устройство.

Блок 13 прерывания содержит элемент НЕ 64, триггер 65 и элемент

2И-НЕ 66.

На выходе 18 селектора 5 появляет- 35 ся сигнал сравнения, если в адресной части циклов ВВОД или ВЫВОД на группевходов-выходов 19 таймера 5 будет комбинация сигналов логических нулей и логических единиц, совпадающая с ком- 0 бинацией, установленной на группе входов 30, т.е. если адрес на группе входов-выходов 19 совпадет с адресом, установленным на группе входов 20. Сигнал сравнения на выходе 18 селектора 5 длится до окончания текущего цикла. Селектор 5 осуществляет сравнение не одного адреса, а группы иэ восьми адресов. Адреса внутри этой группы отличаются один от другого значением од-50 ного иэ трех младших разрядов, При поступлении на вход 21 селектора 5 сигнала требования прерывания этот сигнал поступает на линию требования прерывания внутренней шины 23, а от- 55 туда через канальные передатчики 2— на линию требования прерывания канала 24. Процессор ЭВМ (не показан), получив из этои линии сигнал требования прерывания, завершает выполнение текущей команды и проводит цикл ВВОД

АДРЕСА ВЕКТОРА ПРЕРЫВАНИЯ. Адрес вектора, установленный на входах 25 селектора 5, в сопровождении синхроимпульса-ответа, вырабатываемого на выходе 26, поступает на группу входоввыходов 19 адреса-данных, а оттуда по линиям сигналов адреса — данных внутренней шины 27 через канальные приемо-передатчики 3 — на линии сигналов адреса — данных канала 24 ЭВМ.

Канальные приемо-передатчики 3 исходно включены в направлении передачи сигналов из канала 24 во внутреннюю шину 27 устройства. Переключения направления передачи происходят в моменты ввода информации иэ устройства в ЭВМ в циклах ВВОД и ВВОД АДРЕСА

ПРЕРЫВАНИЯ.

Канальные приемники 1 постоянно включены в направлении передачи сиг) налов из канала 24 во внутреннюю шину 28.

Канальные передатчики 2 постоянно включены в направлении передачи сигналов иэ внутренней шины 23 в канал 24.

Блок 4 выполняет функцию переключателя направления передачи канальных приемо-передатчиков 3.

Блок 13 предназначен для выработки запрета на распространение синхроимпульсов предоставления прерывания при выполнении цикла ВВОД АДРЕСА ВЕКТОРА ПРЕРЫВАНИЯ в том случае, если прерывания требовало данное устройство. Во всех остальных случаях запрет не вырабатывается и синхроимпульс предоставления прерывания, поступающий иэ канала 24 через канальные приемники 1 на внутреннюю шину 28 устройства, ретранслируется по внутрен1 ней шине 23 через канальные передатчики 2 в канал 24.

Компаратор 6 адресов в группе восьми адресов, выделенный селектором 5, распознает четыре адреса, относящие" ся к регистрам таймера 7, и один адрес, относящийся к регистру 9 состояния, При обращении ЭВМ к регистрам таймера 7 в циклах ВВОД нли ВЫВОД, а также при обращении ЗВМ к регистру 9 состояния в цикле ВЫВОД, на выходе 29 компаратора 6 адресов вырабатывается синхроимпульс ответа, поступающий по линии синхроимпульса ответа внутрен1522221 ней шины 23 через канальные передатчики 2 в канал 24 ЭВМ.

Регистр 9 состояния имеет доступ только для записи. Формат и назначение разрядов регистра 9 состояния ил- 5 люстрирует фиг. 2. При включении питания ЭВМ и при запуске программы импульсом начальной установки канала 24, поступающим через канаЛьные приемники 1 по внутренней шине 28 на вход регистра 9 состояния, производится начальная установка (сброс) триггеров 14 и 15 регистра 9 состояния, что приводит к запрету счета всех каналов тай- 15 мера 7 и к запрету выработки сигнала требования прерывания на выходе триггера 12.

Таймер 7 содержит три независимых идентичных программируемых 16-разряд- ъ0 ных вычитающих счетчика, работающих в двоичном или двоично-десятичном коде.

Каждый из счетчиков (каналов) программируют независимо друг от друга, записывая управляющее слово и число и, с которого счетчик начинает вычитание. ЭВМ осуществляет запись (инициализацию) счетчиков, обращаясь в цикле

ВЫВОД к регистру управляющего слова и к трем регистрам данных каналов таймера 7. При этом, на входе 30 выбора кристалла таймера 7 должен действовать сигнал разрешения, адресация ре-. гистров таймера 7 осуществляется с помощью сигналов на ее входах 31 и 32, а запись данных в регистры таймера 7 осуществляется по линиям сигналов восьми младших разрядов адреса-данных внутренней шины 27, подключенных к группе входов-выходов 33 таймера 7, во время действия синхроимпульсов вывода на входе записи 34 таймера 7.

После окончания инициализации каждый из трех каналов таймера 7 начинает работать независимо друг от друга, осу45 ществляя уменьшение на единицу своего содержимого по заднему фронту каждого импульса, действующего на частотном входе этого канала, при условии разрешения счета на соответствующем входе 35, 36 или 37. В зависимости от управляющего слова возможен один из шести режимов работы каждого канала таймера 7.

В составе ЭВМ устройство расотает в программном режиме и в режиме пре55 рываний.

В программном режиме производится инициализация всех каналов таймера 7, т. е. программирование каждого канала таймера 7 на определенный режим работы и занесение н каждый канал своего начального числа. В программном режиме ЭВМ также производит обращение в цикле ВЫВОД к регистру 9 состояния, устанавливая или сбрасывая триггеры 14 и 15 этого регистра. Допустим каналы таймера 7 программируются на режим деления частоты, в нулевой канал заносится начальное число п, в первый и второй каналы — и,, причем и и nq — четные числа от 2 до 6553$

Затем ЭВМ обращается к регистру 9 состояния в цикле ВЫВОД. В адресной части этого цикла срабатывает основной компаратор адресов, заключенный внутри селектора 5 H компаратор 6 адресов, на выходе 38 которого активируется строб управления регистром 9 состояния, а сигналы на выходах 39, 40, 41 пассивны. Этот строб поступает ка вход 42 элемента И 16 регистра 9 состояния и остается активнь>м до конца цикла. По окончании адресной части цикла ВЫВОД ЭВМ активирует линию сигнала нулевого разряда адреса-данных канала 25, сопровождая выводимые данные синхроимпульсом вывода. Компаратор 6 адресов, получив на входе 43.синхроимпульс вывода из внутренней шины 28, вырабатывает на выходе 29 синхроимпульс ответа, поступающий по соответствующей линии внутренней шины 23 через канальные передатчики 2 в какал 24. С приходом ка вход 44 элемента И 16 регистра со- стояния синхроимпульса вывода из внутренней шины 28 ка выходе 45 элемекта

И 16 вь1рабатывается строб занесения, поступающий на С-входы 46 и 47 триггеров 15 и 14. Поскольку íà D-входе 48 триггера 15 сигнал нулевого разряда адреса-данных в рассматриваемый момент времени активен, а на D-входе 49 триггера 14 сигнал шестого разряда адреса- данных пассивен, триггер 15 взводится, а триггер 14 остается в состоянии сброса. На выходе 50 тригге- ра 14 и, следовательно, на входе 37 таймера 7 и на P-входе 51 триггера 12 остается условие запрета, а на выходе 52 триггера 15 и, следовательно, на входах 35, 37 таймера 7 устанавливается разрешение (старт) счета. Таким образом, осуществляется старт .г счета нулевого и первого каналов таймера 7. На этом процесс инициализации

1522221 заканчивается. Он проводится один раз

: а все время работы программы ЭВМ.

В режиме прерываний устройство, Во-первых, организует режим реального фремени ЗВМ, а во-вторых, производит фвод дискретных сигналов в ЭВМ, осуществляя двухпороговую селекцию их по лительности. Получив разрешение на ходе 35, нулевой канал таймера 7 на- 10 инает работу как делитель исходной астоты генератора 8 импульсов в п аз. С выхода 53 этого канала импульы скважности, близкой к двум, перида и Т (Т вЂ” . период импульсов на

ыходе 54 генератора 8) поступают на астотный вход 55 первого канала тайI ера 7. Первый канал таймера 7, на ходе 36 которого также действует раэешение, делит эти импульсы в п раз. 20 а выходе 56 первого канала таймера 7 5удут появляться импульсы скважности, лизкой к двум, периода а n T. Эти пульсы по линии радиального прерыания внутренней шины 23 через каналь-25

ые передатчики 2 поступают в каал 24. Получив сигнал по линии ради ального прерывания канала 24, центальный процессор ЗВМ завершает вы1 полнение текущей команды и обращает ся к фиксированной ячейке памяти ЭВМ,, в которой указан начальный адрес подпрограммы обработки радиального пре рывания. Зта подпрограмма осуществляет наращивание на единицу счетчика меток времени, организованного в одной или нескольких ячейках памяти

ЗВМ, по каждому факту радиального прерывания. Таким образом, с помощью импульсов на выходе 56 первого канала таймера 7 организуется режим реального времени ЭВМ.

ЭВМ, работая в этом режиме, в необходимые моменты времени анализирует длительность дискретных сигналов, поступающих от удаленного источника на вход 57 блока 10 гальванической развязки. Допустим, необходимо проанализировать длительность дискретного сигнала за интервал времени (фиг. За), при этом ожидаемая 50 длительность принимаемого дискретного сигнала должна быть не менее 1/2 периода импульсов меток реального времени на выходе 56 таймера 7, т,е. не менее t -t (нижний порог селек- 55 ции по длительности), и не более периода этих импульсов, т.е. не более

1 -С (верхйий порог селекции по длительности). В момент t прихода очередной метки времени ЭВМ, обращаясь к регистру 9 состояния в цикле ВЫВОД, активирует линии сигналов нулевого и шестого разрядов адреса-данных канала 24, сопровождая выводимые данные синхроимпульсом вывода. Происходит взведение триггера 14 и подтверждение взведенного состояния триггера 16

На выходе 50 триггера 14, а также на входе 37 таймера 7 и на Г-входе 51 триггера 12 активируется сигнал разрешения (см. фиг. Зб). Если на вход 57 блока 10 гальванической развязки в это время поступает дискретный сиг-! .нал, на входе 58 элемента 2И-НЕ 11 действует уровень разрешения в течение времени t --t (см . фиг, Зв) и импульсы периода n T со входа 59 элемента 2И-НЕ 11 (т.е. с выхода 53 нулевого канала таймера 7) поступают на частотный вход 60 второго канала таймера 7 (фиг. 3r). Поскольку первый и второй каналы таймера 7 были запрограммированы одинаково, в момент времени на выходе 61 второго канала таймера 7 появляется сигнал, который взводит триггер 12 (фиг, Зд). Сигнал с выхода 62 этого триггера поступает на вход 21 коммутатора 5. Центральный процессор 3ВМ в.течение времени 1 -с (см. фи . Зд), называемого временем ожидания предоставления прерывания, завершает выполнение текущей команды и вводит адрес вектора прерывания, как это было указано выше при описании селектора 5 работы и блока 13 °

Синхроимпульсом ответа с выхода 26 селектора 5, поступающим через элемент ИЛИ 17 íà R-вход 63 триггера 14 разрешения прерывания, последний сбрасывается (момент времени t на фиг.

Зб), что приводит к запрету счета второго канала таймера 7, сбросу триггера 12 и к снятию сигнала требования прерывания на выходе 22 селектора 5. Подпрограмма обслуживания секторного прерывания, начальный адрес которой находится в ячейке памяти

ЭВМ, на которую указывает введенный вектор, по факту векторного прерывания информируется о том, что принят дискретный сигнал длительностью, причем (t -Й, ) (- ).

В случае, если длительность принимаемого сигнала меньше нижнего порога t,-t, что свойственно импульсу помехи в отсутствие дискретного

1522221

10 сигнала, на выходе 62 триггера 12 не возникает. ЭВМ в этом случае заканчивает анализ принимаемого дискретного сигнала в момент времени t по прихо9 5 ду метки времени (радиального прерывания), сбрасывая в цикле ВЫВОД триггер 14 и одновременно подтверждая взведенное состояние триггера 15 (штриховая линия на фиг. Зб). По фак- 1О ту отсутствия векторного прерывания эа отведенный для анализа промежуток времени -t<. ЭВМ делает вывод о том, что дискретный сигнал отсутствует на входе устройства.

Если необходимо проанализировать дискретный сигнал, имеющий длительность, большую, чем период меток времени t --t< то верхний порог селекции пО длительности программа ЭВМ устанавливает кратным этому периоду, а сразу же после окончания ввода адреса вектора прерывания в момент времени t, программа ЗВМ вновь взводит триггер 14, одновременно подтверждая взведенное состояние триггера 15.

Счетчики второго канала таймера 7 начинают счет с начального значения, и .вся процедура повторяется. ЭВМ делает вывод о длительности принятого дискретного сигнала по количеству векторных прерываний за отведенный промежуток времени, определяемый радиальными прерываниями.

Таким образом, применение устрой. ства позволяет производить ввод дискретных сигналов в ЗВМ, работающую в режиме реального времени, по прерываниям. Отключения центрального процессора ЭВМ на обслуживание устрой-. ства заключаются лишь в однократной за все время работы программы инициализации таймера 7, обслуживании радиальных прерываний (меток времени), включении и выключении в необходимые моменты времени триггера 14 регистра 9 состояния и обслуживании векторных прерываний от устройства. Все вышеперечисленные отвлечения центрального процессора ЭВМ оказывают ничтожна малое воздействие на его загрузку. 5ц ,Пропускная способность устройства, таким образом, выше пропускной способности аналогичных устройств, осуществляющих ввод дискретных сигналов в программном режиме. 55

Кроме того, применение двухпороговой селекции по длительности вводимых дискретных сигналов позволяет повысить степень их защиты от помех, следовательно, повышается достоверность вводимой в ЭВМ информации. Особенно эффективна двупороговая селекция по длительности, когда вводимые дискретные сигналы имеют фиксированную длительность, в несколько раз большую длительности помех ° Зто позволяет легко организовать с помощью устройства помехоэащищенный ввод в ЭВИ цифровых кодов от удаленных источников по последовательному каналу связи.

Формула и з о б р е т е н и я

Устройство для ввода дискретных сигналов, содержащее канальные приемники, канальные передатчики, канальные приемопередатчики, блок управления, селектор адреса, компаратор адресов, программируемый таймер, генератор импульсов, регистр состояния и блок гальванической развязки, вход которого является информационным входом устройства, входы канальных приемников являются группой входов управления обменом устройства, выходы канальных передатчиков являются выходами устройства, входы-выходы первой группы канальных приемопередатчиков являются входами-выходами адреса-данных устройства, вход переключения направления передачи канальных приемопередатчиков подключен к выходу блока управления, группа входов-выходов адреса данных селектора адреса соедине- . на с второй группой входов-выходов канальных приемопередатчиков, первая, вторая .группы входов установки адресов сравнения и выход сравнения адресов селектора адреса соединены соответственно с положительным и нулевым потенциалами источника питания и с входом сравнения адресов компаратора адресов, адресные входы компаратора адресов соединены с младшими разрядами второй группы входов-выходов канальных приемопередатчиков, выход синхроимпульса ответа компаратора адресов соединен с соответствующим входом канальных передатчиков, выходы сигнала разрешения, младший и старший адресные выходы компаратора адресов соединены соответственно с входом выбор кристалла, с младшими и старшими адресными входами программируемого таймера, частотный вход нулевого канала которого соединен с выходом

1522221

12 генератора импульсов, вход синхроимпульса чтения и вход синхроимпульса записи программируемого таймера соединены с соответствующими выходами

5 канальных приемников, о т л и ч а ющ е е с я тем, что, с целью повьш ения достоверности вводимой информации в устройство введены элемент 2И-НЕ, IK-триггер, блок прерывания, а регистр состояния содержит первый Dтриггер, второй Р-триггер, элемент И и элемент ИЛИ, .вход синхроимпульса ввода блока управления соединен с соответствующим выходом канальных приемников, вход синхроимпульса1 ответа соединен с соответствующим входом канальных передатчиков, группа входов управления обменом селектора адреса соединена с соответствующими выходами 2О канальных приемников, входы ввода и вывода компаратора адресов соединены с соответствующими выходами канальных приемников, группы входов-выходов данных программируемого таймера соединены25 ,с соответствующими входами-выходами .второй группы младших разрядов канальных приемопередатчиков, выход нулевого канала программируемого таймера соединен с частотным входом первого канала и с первым входом элемента 2ИНЕ,к второму входу которого подключен выход блока гальванической развязки,вы. ход элемента 2И-НЕ соединен с частотным входом второго канала программируеМого таймера, выход радиального преры- 5 вания первого канала которого соединен с соответствующим входом канальных пере. датчиков, прямой выход второго D-триггера соединен с входами разрешения счета нулевого и первого каналов про- "О граммируемого таймера, прямой выход первого D-триггера соединен с входом разрешения счета второго канала программируемого таймера и входом ;.броса

IK-триггера, синхров ",од которого соединен с выходом второго канала программируемого таймера, I- и К-входы

IK-триггера соединены соответственно с положительным и нулевым потенциалами источника питания, первый вход элемента И соединен с выходом строба управления компаратора адресов, второй вход элемента И соединен с выходом синхроимпульса канальных приемников, выход элемента И соединен с синхровходами первого и второго D-триггеров, D-входы которых соединены соответственно с шестым и нулевым разрядами входов-выходов второй группы канальных приемопередатчиков, вход сброса второго D-триггера соединен с первым входом элемента ИЛИ и с выходом начальной установки канальных приемников, второй вход элемента ИЛИ соединен с выходом синхроимпульса ответа селектора адреса, выход, элемента

ИЛИ соединен с входом сброса первого Э-триггера, инверсный выход IKтриггера соединен с входом требования прерывания селектора адреса, первая и вторая группы входов установки адреса вектора прерывания которого соединены соответственно с положительным и нулевым потенциалами источника питания, выход требования прерывания селектора адреса соединен с соответствующим входом канальных передатчиков, и с входом требования прерывания блока прерывания, вход предоставления прерывания и выход предоставления прерывания которого соединены соответственно с соответствующими выхода—

MH канальных приемников и входов KB нальных передатчиков.

1522221

f5 A О 12 11 f0 9 Ю 7 6 5 4 Я 2 1 0

РПр (sn) - п о яаимнО не30стуиные разряды — аз ешение рерь|3ания — крОграиИный доступ &у записи

1522221

C LFHpl7bPQM риекнит5 /

Ий ФРа рнИЕ

Составитель С. Кулиш

Редактор А. Долинич Техред A.Êðàâ÷óê Корректор B. Кабаций

Заказ б965/47 Тираж бб8 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, М6сква, 3(-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r Ужгород, ул. Гагарина, 101