Полиномиальный интерполятор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах измерения и регулирования. Цель изобретения - повышение точности. Полиноминальный интерполятор содержит генератор тактовых импульсов, регистр, преобразователь код напряжение, интеграторы, запоминающие элементы, суммирующие усилители, дополнительные преобразователи код-напряжение, элементы задержки, дополнительные регистры, блок вычисления конечных разностей, сдвигающий регистр. Интерполятор позволяет исключить погрешность от задержки распространения сигнала в интеграторах. 1 ил.

союз совктсних социАлистичксних кспуьлин цИ 1 С 06 G 7/30 госуддрствкнный комитент до изов чтениям и отис цтиям п1 и унт ссс1

1 (21) 44117 } 2/24-24 (22) 18. 04. 88 (46) 15.11.89. Бюл. Р 42 (72) А.Д.Кондаков и !О.П.Петришин (53) 681.3 (088.8) (56) Авторское свидетельство СССР

Р 851425, кл. С 06 G 7/30, 1979.

Авторское свидетельство СССР

Р 663074, кл. Н 03 Н 7/02, 1977. (54) ПОЛИНОИИАЛЬНЫЙ ИНТЕРПОЛЯТОР (57) Изобретение относится к вычислительной технике и может быть ис— пользовано в устройствах измерения и

Изобретение относится к вычислительной технике и может быть использовано в устройствах измерения и ре-гулирования.

Цель изобретения — повышение точности.

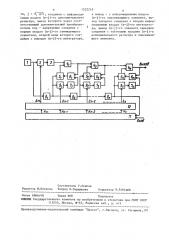

На. чертеже представлена схема предлагаемого интерполятора.

Полиномиальный интерполятор содержит генератор 1 тактовых импульсов, регистр 2, преобразователь 3 код— напряжение, интеграторы 4„-4 „, залов минающие элементы 5„-5» суммирующие усилители 6„-6„, дополнительные преобразователи 7„-7„ код — напряжение, элементы 8,-8 „ задержки, дополнительные регистры 9,-9 » блок 10 вычисления конечных разностей и сдвигающий регистр 11.

Устройство работает следующим образом. регулирования. Цель изобретения — по— вьппенле точности. Полиномиальный интерполятор содержит генератор такто вых импульсов, регистр, преобразователь код — напряжение, интеграторы, запоминающие элементы, -суммирующие усилители, дополнительные преобразователи код — напряжение, элементы задержки, дополнительные регистры, блок вычисления конечных разностей, сдвигающий регистр. Интерполятор позволяет исключить погрешность от задержки распространения сигнала в интеграторах. 1 ил.

Последовательный многоразрядный сдвигающий регистр 11 на каждом такте записывает очередное значение кода сигнала N и хранит его вместе спредыдущими и кодами N„...N „. Из этих (и+1) значений кода сигнала блок 1О конечнйх разностей и-го порядка фор- Р мирует на своих (n+1) выходах коды конечных разностей: от нулевого до вы и-го порядка Д вЂ” Д Яд

Регистры 2 и 9 служат для синхронизации работы преобразователей 3 и

7 код — напряжение. Эти регистры уп— равляются тактовыми импульсами от генератора 1 тактовых импульсов, задержанными на нужную величину элемента в 4 ми 8 задержки. Преобразователи 3 и 7 код — напряжение преобразуют коды конечных разностей в аналоговую форму

U„,..., U . Конечная разность и-ro порядка U, служит для получения

1522245 текущего значения сигнала U(») путем п-кратного интегрирования интеграто-: рами 4. Конечные разности меньших порядкОв П„,..., U используются для установления нужных начальных условий интегрирования на первых тактах работы фильтра, а также для компенсации дрейфа интеграторов в установившемся режиме. Элементы 8 задержки служат для стробирования запоминающих элементов 5. При этом величина запаздывания 7(, в первом элементе задержки выбирается такой, чтобы запоминающий элемент 5 фиксировал значение разнос- 15 ти между установившимся значением на-! пряжения на первом преобразователе 7 и текущим значением напряжения на выходе первого интегратора U „ именно

f в тот момент, когда погрешность от запаздывания сигнала в первом интеграторе становится равной нулю. ОстаI точное значение разности E „, = U „,—

l- П„., обусловленное дрейфом интег! ратора, подается с обратным знаком на 25 вход интегратора в следующем такте ,цля компенсации этого дрейфа. Аналогично осуществляется компенсация зааздывания и дрейфа в остальных интеграторах. Наличие запаздывания в З0 нтеграторах предлагаемого устройст-! ва не приводит к задержке в получении значений конечных разностей П,, !

U„,..., U поэтому компенсация этого, запаздывания становится осуществимой, хотя и приводит к задержке сигнала на

35 выходе фильтра. Напряжение на выходе йнтерполятора с учетом задержек сиг,нала в интеграторах описывается выражением

t+е лб ° ь!

)) 1 и(! к) =V — -I ( кк ккк б л 45 (б! + ... + 1 к

Т. ! n л ))-! ")! "t ! )цб! дабл( к(б!„, + ) и„а(б + б,)) а(б + л

h-! ll л ) )д(» . б )jg(» . л ) бФ! (е!

»о « где лб — величина задержки распрост-! ранени в 1-м ин граторе; 55

Т - период следования кодов;

»0> моменты времени, соответствующие поступлениям кодов

N6, N, Nh соответственно.

В результате интегрирования получается выражение, которое совпадает (с точностью до константы в аргументе) с интерполяционным полиномом Ньютона.

Следовательно, предлагаемый интерполятор позволяет исключить погрешность от задержки распространения сигнала в интеграторах. При этом величина задержки сигнала на его выходе остается такой же, как в прототипе.

Блок 10 имеет пирамидальную пи (и+1) уровневую схему, содержащую — — — —— вычитателей и реализующую вычисление известных из литературы выраженил конечных разностей дискретного входного сигнала, представленного равноот.т стоящими отсчетами.

Формула из обре тения

Полиномиальный интерполятор, содержащий регистр, тактовый вход которого соединен с выходом генератора тактовых импульсов, а выход — с входом преобразователя код — напряжение, и интеграторов, первый информационный вход каждого i-ro интегратора, = 2, п соединен с выходом (i-1)-го интегратора, а выход n-ro интегратора является выходом интерполятора, и запоминающих. элементов и п суммирующих усилителей, отличающийся тем, что, с целью повышения точности, в него введены блок вычисления конечных разностей, сдвигающий регистр, п дополнительных регистров, п дополнительных преобразователей код — напряжение и п элементов задержки, соединенных последовательно, вход первого элемента задержки соедийен с выходом генератора тактовых импульсов, выход преобразователя код — напряжение соединен с первым информационным входом первого интегратора, информационный вход сдвигающего регистра соединен с шиной задания входных кодов, его тактовый вход соединен с выходом n-r.o элемента задержки, а и+1 выходов сдвигающего регистра соединены с соответствующими входами блока вычисления конечных разностей, выход конеч-, ной разности и-го порядка которого соединен с информационным входом регистра, а выход j-ой- конечной разнос1522245

Составитель Г.Осипов

Редактор И.Петрова,Техред Л.Сердюкова

Корректор Н.Кабаций

Заказ 6966/48, Тираж 668 Подписное

ВНКИПй Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 ти, J = О, и 1, соединен с информационным входом (и-j)-ro дополнительного регистра, выход которого через соответствующий дополнительный преобразователь код — напряжение соединен с первым входом (n-j)-го суммирующего усилителя, второй вход которого соединен с выходом (n-j)-го интегратора, а выход — с информационным входом (n-j)-го запоминающего элемента, выход которого соединен с вторым информационным входом (Il ))-го интеграто5 ра, выход (и-J )-го элемента задержки соединен с тактовыми входами (n-j )-х дополнительного регистра и запоминающего элемента.