Формирователь импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки сигналов преимущественно с тахометрических датчиков и предназначено для формирования импульсов из пульсирующего сигнала с дрейфующей постоянной составляющей. Цель изобретения - повышение стабильности и расширение функциональных возможностей - достигается путем обеспечения удвоения частоты входного сигнала и возможности использования дифференциального входа. Формирователь импульсов содержит компараторы 1 и 2, делитель 3 опорных напряжений, RS-триггер 4, логический элемент 5, фильтр 6, интегратор 7 и элемент 8 сложения. Изобретение позволяет расширить область устойчивости работы и повысить быстродействие формирователя. Формирователь может быть реализован в интегральном исполнении на одном кристалле с датчиком, например, с магнитотранзистором. 2 з.п. ф-лы, 5 ил.

СОЮЗ СОНЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1 (192 (112 (512 4 Н 03 К 5/01 е*.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ДВТ0РСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР

1 (21) 4322437/24-21 (22) 23.09.87 (46) 15.11,89. Бюл. 22.42 (71) Ленинградское научно-производственное объединение "Электронмаш" (72) Д.А. Летюхин и Г.С. Брайловский (53) 621.374 (088.81 (56) Хоровиц П. и Хилл У. Искусство схемотехники. М.: Мир, 1984, т.1, с. 421, рис. 7.1.

Там же, т.1 с. 272, рис. 4.23. (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ (57) Изобретение относится к импульсной технике, может быть использовано в устройствах обработки сигналов преимущественно с тахометрических датчиков и .предназначено для формирования импульсов из пульсирующего сиг2 нала с дрейфующей постоянной состав-. ляющей. Цель изобретения — повышение стабильности и расширение функциональных возможностей — достигается путем обеспечения удвоения частоты входного сигнала и возможности использования дифференциального входа. Формирователь импульсов содержит компараторы 1 и 2, делитель 3 опорных напряжений, RS-триггер 4, логический элемент 5, фильтр 6, интегратор 7,и элемент 8 сложения. Изобретение позволяет расширить область устойчивости работы и повысить быстродействие формирователя. Формирователь может быть реализован в интегральном исполнении на одном кристалле с датчиком, например, с магнитотранзистором. 2 з.п. ф-лы, 5 ил.

1522388

Изобретение относится к импульс ой технике и может быть использовано в устройствах обработки сигналов, преигтущественно с тахометрических датчиков, и предназначено для формирования импульсов из пульсирующего сигнала с дрейфующей постоянной сос.— тавляющей.

Цель изобретения — повышение ста,!0 бильности и расширение функциональных возможностей за счет обеспечения удвоения частоты входного:сигнала и возможности использования дифференциального входа.

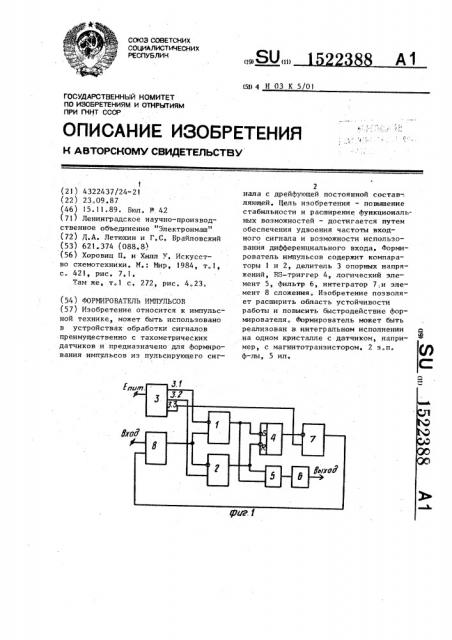

На фиг. 1 представлена функциональная схема формирователя импульсов; на фиг,2 — временная диаграмма„поясняющая его работу; на фиг.З(а,б) примеры реализации элементов сложе20 ния; на фиг.4 — функциональная схема формирователя импульсов с повышенным быстродействием; на фиг.5 — временные диаграммы, поясняющие его работу.

Формирователь импульсов (фиг,1) со-25 держит первый 1 и второй 2 компараторы, делитель 3 опорных напряжений, ВЯтриггер 4, логический элемент 5, фильтр 6, интегратор 7 и элемент 8 сложения, входную и выходную шины, причем первый вход компаратора 1 и второй вход компаратора 2 подключены соответственно к первому и второму выходам делителя З,,второй вход компаратора 2 подключен к первому входу компаратора 2, выходы компаратора 1 и 2 подключены соответственно к входам Б и В триггера 4, и соответственно к первому и второму входам логического элемента 5, выход которого че40 рез фильтр б соединен с выходной глиной, Выход триггера 4 подключен

1 к ттервому входу интегратора 7, второй вход кот6рого соединен с третьим выходом делителя 3 а выход — к перэ

45 вому входу элемента 8 сложения, второй вход которого соединен с входной шиной, а выход подключен ко второму входу компаратора 1.

В формирователе можно испольэовать

50 различные элементы сложения, для организации дифференциат;ьного входа используется элемент сложения (фиг.Зб) который содержит пять резисторов и операционный усилитель . На выходе элемента 8 сложения формируется сиг55 нал, пропорциональный сумме сигналов между вторым и дополнительным входами и первым входом, Коэффициент передачи входного сигнала определяется резисторами R2-R4, для сигнала с выхода интегратора 7 резисторами R 1 и

R 4а

Формирователь импульсов (фиг.4) лополнительно содержит ключ 9, блок

10 управления, причем выход триггера

4 подключен ко входу блока 10 управ. ления, выход которого подключен к управляющему входу ключа 9, выход ключа 9 соединен с третьим входом интегратора 7, первый вход ключа 9 подсоединен к выходу триггера 4 или к

BIHHe питания (пунктир).

Логический элемент 5 выполняет функцию И-НЕ (фиг, 2з) в случае отрицательной логики элемент 5 выполняет функцию ИЛИ-HF..

Устройство работает следующим образом.

В исходном состоянии на выходе всех элементов установлено напряжение 0 (фиг.2), В момент t 1 подается напряжение питания Еггт,,-. На выходе интегратора 7 (фиг.2 в) в этот момент сохраняется напряжение О, а. на выходе схемы сложения 8 (фиг,2 г) реализованной, например, в соответствии с фиг.3 а) устанавливается напряжение, меньшее, чем Е 2, которое формируется на втором выходе делителя опорных напряжений 3, в результате чего на выходах компараторов 1 и 2(фиг.

2 д,е) и триггера 4 соответственно устанавливаются состояния "1 "0", "0", "0" на входе интегратора 7 вызывает линейный рост напряжения на его выходе и на выходе элемента сложения 8 (фиг.2 r), При достижении напряжением уровня

Е 2, компаратор 2 установится в состояние "1". Роста напряжения будет продолжаться до уровня F. 1, который формируется на первом выходе делителя 3. Затем компаратор 1 переключится в "0" и переключит триггер 4 в

"!". Это вызовет линейный спад напря жения на выходе интегратора 7 и элемента сложения 8. Напряжение станет меньше Е! и компаратор 1 установится в состояние логической "1". Таким образом, на выходе компаратора l формируется импульс, длительность "0" которого будет определяться задержками компаратора -1, триггера 4, элемента сложения 8 и быстродействием интегратора 7. Состояние триггера 4 сохранится и спад будет продолжать5

55

5 152 ся до тех пор, пока напряжение не достигнет уровня Е2. Затем компаратор

2 и триггер 4 переключится в состояи ние 0, что вызовет рост напряжения на выходе интегратора 7 и элемента счожения 8. Далее процесс будет периодически повторяться.

Импульсы, формируемые компараторами 1 и 2, объединяются в импульсную последовательность удвоенной частоты логическим элементом 5. Фильтр 6.подавляет короткие импульсы и на выходе автоколебания отсутствуют (фиг.2и)

При подаче на вход формирователя (момент t2 на диаграмме фиг 2) пульсирующего напряжения, амплитуда переменной составляющей которого больше (El-Å2) и частота вьппе частоты ав-. токолебаний. Компаратор 1 переключит— ся в состояние "0" при превьппении сигнапа на выходе элемента сложения

8 уровня El При понижении напряжения ниже уровня Е2 в состояние "О" будет переключаться .компаратор 2. При несимметрии переменной составляющей сигнала на выходе элемента сложения

8 относительно уровня (Е1+Е2)/2 длительности уровней "0" на выходах компараторов 1 и 2 будут неравны, а сигнал на выходе триггера 4 будет отличаться от меандра.Иитегратор 7 будет формировать напряжение, пропорциональное разности между опорным напряжением F, которое формируется на третьем выходе делителя опорных напряжений 3 и равно половине размаха сигнала триггера 4, и постоянной составляющей последовательности импульсов на выходе триггера 4. Напряжение на выходе интегратора 7 .суммируется со входным сигналом элементом сложения 8. В результате на выходе его постоянная составляющая сигнала стре-. мится к уровню (Е1+Е2)/2, При совпадении этих уровней на выходах компа ратора 1 и 2 длительности импульсов становятся равными, а на выходе триг" гера 4 появляется меандр.

Изменяя величину Е> можно регулировать скважность импульсов на выходе триггера 4. Длительность импульсов на выходах компараторов 1 и 2 при воздействии входного сигнала определяется временем, в течение которого сигнал на выходе схемы сложения будет больше (меньше) уровня EI (Е2), Эта длительность много больше длительности импульсов автоколебаний

2388 6

В связи с большой разницей длительностей импульсов антоколебаний и импульсов, сформированных из входного сигнала, фильтр 6 эффективно подавляет автоколебания и полностью пропускает рабочие импульсы, Например, при использовании микросхем серий К521, К561 и К!40 длительность импульсов автоколебаний составила порядка 10 мкс, а длительность импульсов с датчиков не менее 10 мс, что обеспечивает эффективную работу фильтра.

Таким образом, В формирователе достигается автоматическая настройка порога срабатывания на уровень постоянной составляющей входного сигнала, что позволяет компенсировать

20 дрейф и расширить область устойчивой работы по входному сигналу, а также достигнуто удвоение частоты входного сигнала.

Формирователь с повышенным быстро25 действием (фиг.4) работает следующим образом.

При подаче напряжения питания триггер 4 устанавливается в состояние

"О"-(фиг.5). При этом блок управления

30 10 удерживает ключ 9 в открытом состоянии (на фиг.5 в показан ток через ключ 9). Этим достигается быстрый рост напряжения на выходе интегратора 7 (фиг.5 б) при включении пи в . тания и соответственно малое время

35 установления рабочего режима. После включения питания по фронту первого, импульса блок управления 10 (фиг.5 г) изменит свое состояние и закрывает

40 ключ 9.

Интегратор 7 начинает работать с большой постоянной времени. Импульсы следующие после первого, не изменяют состояние блока управления 10.

Для приведения блока управления в исходное состояние необходимо выключить питание.

Возможная реализация блока управления 10 приведена на фиг,4., Логи50 чески она представляет собой схему

ИЛИ, один из входов которой соединен с ее выходом, Она содержит три и-канальных МОП вЂ” транзистора 11 — 13 и два р-канальных МОП - транзистора

14 и 15. Затвор транзистора 11 является входом блока управления, стоки транзисторов 11 и 12, исток транзис— тора 13 и затвор транзистора 14 соединены, истоки транзисторов 11 и 12!

522388

7 соединены с затвором и стоком транзистора 15 и шиной питания. Затвор и сток транзистора 13 соединены с ис-! током транзистора 14 и со второй шиной питания.,. Сток транзистора 14 сое5 динен с истоком транзистора 15 и с выходом блока управления. Затвор. транзистора 12 соединен со стоком транзистора 14.

Предлагаемая схема имеет два устойчивых состояния: транзисторы 11 15 закрыты, через транзисторы 11 — 15 протекает ток.

При -включении и нулевом напряжении на затворе транзистора 11 блок управления 10 всегда установится в первое состояние, Транзистбр ll откроется при подаче на его затвор "1", что вызывает открывание транзистора

14, напряжение на его стоке начнет возрастать и откроет транзистор 12.

Схема перейдет во второе состояние и сохранит его при дальнейших воздействиях на ее входе. 25

Таким образом, .устройство позволяет расширить область устойчивости. работы и функциональные возможности, повысить его быстродействие. Изобретение позволяет также реализовать формирователь в интегральном исполнении на одном кристалле с датчиком . например, с магнитотранзистором), получив таким образом функционально законченный прибор.

Формула изобретения

1. Формирователь импульсов, содержащий первую входную шину, выходную шину, шину питания, два компаратора, делитель опорных напряжений и RS-zpvr rep, прн этом .первый вход первого и второй вход втброго компараторов ! соединены соответственно с первым и вторым выходами делителя опоРных нап- 45 . ряжений, второй вход первого компа1 ратора соединен с первым входом второго компаратора, а выходы компараторов соединены соответственно с Sи Н-входами,RS-триггера, о т л и— ч а ю щ и и с. я тем, что, с целью повышения стабильности и расширения функциональных возможностей; введены логический элемент, фильтр, интегратор, элемент сложения и вторая входная шина, причем выходы первого и второго компараторов соединены соответственно с первым и вторым входами логического элемента, выход которого соединен с входом фильтра, выход которого соединен с выходной шиной,, выход ББ-триггера. соединен с первым входом интегратора, второй вход которого соединен с третьим выходом делителя опорных напряжений, выход интегратора соединен с первым входом элемента сложения, второй вход которого соединен с первой входной шиной, дополнительный вход — с второй входной шиной, а выход - с вторым входом первого компаратора.

2, Формирователь по п.l, о т л ич а ю шийся тем, что элемент сложения содержит первый, второй, третий, четвертый и пятый резисторы и усилитель, причем первые выводы первого, второго и третьего резисторов подключены соответственно к первому, второму и дополнительному входам элемента сложения, первый вход усилителя соединен с вторыми выводами первого и второго резисторов и первым выводом четвертого резистора, второй вывод которого соединен с выходом усилителя, являющимся выходом элемента сложения, второй вход усилителя соединен с вторым выводом третьего резистора и с первым выводом ятого резистора, Второн вывод которого соединен с общей шиной.

3. Формирователь по п,l, о т л ич а ю шийся тем, что с целью повышения быстродействия, в него вве— дены ключ и блок управления, причем выход HS-триггера соединен с входом блока управления, выход которого соединен с управляюшим входом ключа, выход ключа соединен с третьим входом интегратора, а первый вход ключа подключен к выходу триггера или к шине питания.

1 52238(>

inurn

П /х

Ц

f2 фиг.2

&а ис7

gun.

1522388

faut

ФЬг У

Составитель М. Леонова

Техред И.Ходанич

Корректор М. Йароыи

Редактор И.Сегляник

Заказ 6978/55 тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 1О1