Синхронный делитель частоты на пять

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в трактах деления частоты. Цель изобретения - повышение быстродействия при одновременном снижении потребления энергии, за счет исключения паразитной емкости D-входа триггера 2 и исключения вытекающего тока D-входа данного триггера - достигается путем подключения D-входа данного триггера к источнику логической "единицы" и образования новых функциональных связей. 2 ил.

COCOS COBETCHHX

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11) А1 (51) 4 Н 03 K 23/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21 ) 43281 77/24-21 (22) 16.11,87 (46) 15.11.89.Бюл. М 42 (71) Всесоюзный институт по проектированию организации энергетического строительства Оргэнергострой" (72) А. И. Беркут, И,В. Колосов и А,В,Колосов (53) 621.374,4 (088,8) (56) Авторское свидетельство СССР

1(- 778844000077, кл. Н 03 К 23/70, 15.02.79.

Экономический патент ГДР

Ф 214506, кл. Н 03 К 23/02, 10,10.84.

2 (54) СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

НА ПЯТЬ (57) Изобретение относится к импульс— ной технике и может быть использова— но в трактах деления частоты, Цель изобретения — повышение быстродействия при одновременном снижении потребления энергии за счет исключения паразитной емкости D-входа триггера

2 и исключения вытекающего тока

D-входа данного триггера — достигается путем подключения D-входа данного триггера к источнику логической единицы" и образования новых функциональных связей. 2 ил.

1522397

Синхронный делитель частоты на пять, содержащий первый,, второй, тре35 тий D-триггеры, -тактовые входы которых подключены к входной шине, прямой выход второго триггера подключен к

D-входу третьего триггера, о т л ич а ю шийся тем, что, с целью

40 увеличения быстродействия при одно— временном уменьшении потребления энергии, D-вход второго триггера подключен к источнику логической "едитю ницы, а R-вход — к прямому выхо45 ду первого D-триггера K D-входу которого подключен инверсный выход третье ro D- триггера.

Изобретение относится к импульсной технике и может использоваться в трактах деления частоты, например, в вычислительной технике, цифровых синтезаторах частот.

Цель изобретения — повышение быстродействия при одновременном снижении потребления энергии, за счет исключения паразитной емкости 10

D-входа триггера и исключения вытекающего тока D-входа данного триггера путем подключения его к источнику логической "1".

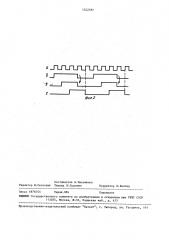

На фиг,1 приведена принципиальная схема синхронного делителя частоты на пять; на фиг,2 временные диаграммы, поясняющие его работу

Синхронный делитель частоты на пять содержит три D-триггера 1 - 3 20 тактовые входы которых подключены к входной шине 4, прямой выход второго триггера 2 подключен к D-входу треть" его триггера 3, à D-вход, второго триггера 2 подключен к источнику логичес- 2g и tt кои 1, а R-вход — к прямому выходу первого триггера I, к -D-входу которого подключен инверсный выход третьего триггера 3.

Синхронный делитель частоты на пять работает следующим образом.

Пусть в начальный момент все триг. геры находились в нулевом состоянии, тогда по фронту первого входного импульса (фиг .2а) триггер 1 устано— вится в состояние "1" (фиг.2б) так как íà его D-входе присутствует уровень логической "1" с инверсного выхода триггера 3, триггер 2 оста-т- . нется в состоянии "0" (фиг.2в), так как на его В-входе к моменту поступления первого входного импуль,са присутствовал уровень логическо—

lro "0" с прямого- выхода триггера 1, триггер 3 также останется в состоя,нии "0",(фиг.2г), так как на его

iD-входе уровень логического "0", по фронту . второго импульса триггер

2 установится в "1" (фиг. 2в ), так как на его D-входе уровень логичес-

tt tl кои 1 с источника, à íà R-входе уровень логической "1" с прямого выхода триггера 1, триггеры 1 и 3 не меняют своего состояния (фиг.2б и г) по фронту третьего входного импульса устанавливается в "1" триггер 3 (фиг.2г), так как на его D-входе уровень логической "1" с прямого выхода триггера 2, триггеры 1 и 2 не меняют своего состояния (фиг ° 26 в), ° уровень логического "0" с инверсного выхода триггера 3 поступает на

D-вход триггера 1 и по фронту четвертого входного импульса триггер I устанавливается в "0" (фиг,2б), одновременно уровень логического

II tt

0 с прямого выхода триггера 1 поступаетт на R-вход триггера 2 и т ригrep 2 устанавливается в "0 " (фиг . 2в ) на D- вход. тригг ера 3 поступает уров ень логического " 0" с прямого выхода т риггера 2 и по фронту пятого входного импульса триггер 3 ус танавлив ается в "0", далее цикл работы пов то ряется .

Формула изобретения

1522397 РО2 Г

Составитель А. Чистякова

Редактор И. Сегляник Техред М. Ходанич

Корректор Л. Бескид

Заказ 6978/55 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035,- Москва, Ж-35, Рауюская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101