Устройство для умножения двух n-разрядных чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия устройства, которая достигается путем реализации способа умножения при помощи параллельно-последовательного суммирования N чисел, для чего в устройство, содержащее регистры 1 сомножителей, группу элементов И 3, матрицу одноразрядных сумматоров 4, вводятся K N- разрядных сумматоров 5, N элементов задержки 6 и K элементов НЕ, что дает возможность пропорционально наращивать разрядность групп перемножаемых чисел. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (su ф 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPbfTHRM

ПРИ ГКНТ СССР (21) 4314204/24-24 (22) 06,08.87 (46) 23.11.89. Вюл. 9 43 (72) В.П.Бевяков и Е.Л.1виршова (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 1203512, кл. G 06 F 7/52, 1984.

Авторское свидетельство СССР

11 - 1067500, кл. G 06 F 7/52, 1981, (54) УСТРОЙСТВО ДЛЯ УЛОЖЕНИЯ ДВУХ

N-РАЗРЯДНЬЖ ЧИСЕЛ (57) Изобретение относится к вычислительной технике. Цель изобретения„„SU„„1524046 А 1

2 повьппение быстродействия устройства, которая достигается путем реалия а ции спос о6 а умножения при помощи параллельно-последовательного суммирования N чисел, для чего в устройство, содержащее регистры 1 сомножителей, группу элементов И 3 матрицу одноразрядных сумматоров 4, вводятся К и-разрядных сумматоров

5, и элементов задержки 6 и К элементов НЕ, что дает воэможность пропорционально наращивать разрядность групп перемножаемых чисел . 3 ип.

1524046

Изобретение относится к вычислительной технике и предназначено для использования в ÂÈ.

Цель изобретения - повышение бы5 стродействия устройства умножения и

N-разрядных чисел (N-2 ).

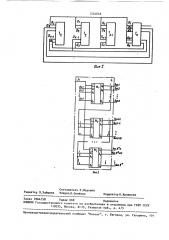

На фиг. изображена функциональная схема устройства для умножения двух И-разрядных чисел; на фиг.2 — 1и схема соединения регистров сомножителей; на фиг. 3 - пример органиэации регистра 1; .

Устройство (фиг. 1) содержит две группы по К N-разрядных регистров

1 множимого и множителя, К элементов и

HE 2, группу элементов И 3, (2 -1)

К одноразрядных сумматоров 4, К ираэрядных сумматоров 5, и элементов

6 задержки. 20

Устройство работает следующим образом.

В начале первого такта одновременно подаются первые К-разрядные группы миожимого и множителя на вхо- 25 ды двух групп регистров l соответственно. По сигналу f, эти группы заносятся в регистры 1. Злементарные произведения разрядов групп формируются на элементах И 3 группы, затем на одноразрядных сумматорах 4 формируются частичные суммы элементарных произведений и переносы, ко" торые поступают в многовходовой сум матор 5, на выходе первого разряда которого формируется сигнал произведения соответствующих разрядов. На входах каждого разряда, начиная со второго, и выходе переноса старшего разряда каждого многоразрядного 4р сумматора 5 формируется сигнал переноса в старшие разряды.

3а второй такт работы аналогично получаются элементарные произведения разрядов следующей группы, которые за-45 тем суммируются вместе с переносом, сформированным в предыдущем такте.

Таким образом, с окончанием подачи часть групп чисел устройство формирует младшую часть их произведения.

За последующие — такта содержимое реК гистра 1 множителя остается беэ изменений, а из регистра множимого последовательно выписываются К-разрядные группы множимого с заполнением освободившихся ячеек этого регистра 1 знаком множимого, отрицательное значение которого представлено обратным кодом, Формула изобретения

Устройство для умножения двух Nразрядных чисел (N-2 ), содержащее

N-разрядные регистры множимого и множителя, группу элементов И и п одноразрядных сумматоров, причем входы множимого и множителя устройства соединены соответственно с информационными входами N-разрядных регистров множимого и множителя, выходы разрядов

Ф

H которых, кроме выходов 2 -х разрядов

N-разрядного регистра множимого, соединены с первыми и вторыми входами соответствующих элементов И группы, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены К элементов НЕ (К— число групгы разрядов перемножаемых чисел), ((2"-1)К-n одноразрядных сумматоров, К и-разрядных сумматоров и и элементов задержки, входы которык соединены с выходами разрядов, начиная с второго, и выходом переноса

K-го и-разрядного сумматора соответственно, выходы 2 -х разрядов Н-рази рядного регистра множимого соединены с выходами соответствующих К элементов НЕ, выходы которых соединены с соответствующими входами элементов

И группы, выходы которых, кроме выходов -x элементов И группы, соединены с соответствующими входами перл вых (2 -К)-х одноразрядных сумматоров, выходы К-х элементов И группы соединены с входами переноса соответствующих К-х разрядных сумматоров, выходы суммы н переноса первых (2 -К)-х одноразрядных сумматоров соединены соответствующими входами последующих одноразрядных сумматоров, выходы суммы и переноса которых соединены с входами разрядов первого слагаемого соответствующих и-разрядных сумматоров, выходы первого разряда которых соединены с выходами соответствующих разрядов произведения устройства, выходы элементов задержки соединены с соответствующими входами второго слагаемого первого и-разрядного сумматора, выходы разрядов, начиная с второго, и выход переноса д-ro n-разрядного сумматора (i l,...,Ê-l) соединены соответственно с входами j-x разрядов второго слагаемого (j l,...,n) (i+1)-ro празрядного сумматора.

)524046

Составитель Е.Мурзина

Редактор JI.Çàéöåâà Техред Л.Олийнык

Корректор О. Кравцова

Заказ 7044/50 Тираж 668 Подписное

ВНИКЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

««

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101