Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при создании микропрограммных автоматов управления устройствами автоматики, в частности в контроллерах внешних устройств ЭВМ и интерфейсных узлах. Цель изобретения - повышение быстродействия устройства путем уменьшения задержки выдачи выходных сигналов при операциях условных переходов. Устройство содержит регистр микрокоманд 1, блок 2 памяти микрокоманд, коммутатор 3 адреса, коммутатор 4 условий, блок 5 местного управления. Цель достигается за счет того, что адрес перехода по наличию условия подготавливается заранее, а в момент смены условия формируется сигнал приема в регистр микрокоманд выходных сигналов с минимально возможной задержкой. 1 з.п. ф-лы, 3 ил.

„„SU„„1524 4

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН у 4 С 06 F 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕтаНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21 ) 4336848/24-24 (22) 08.l0.87 (46) 23. 11,89. Бюл. Ь 43 (7l) Конструкторское бюро "Шторм" при Киевском политехническом институте им. 50-летия Великой Октябрьской социалистической революции (72) В.Г.Галаган, И.И,Дражан и В.Г.Минаев (533 681.32(088.8) (56} Майоров С.А., Новиков Г.И.

Структура ЭВМ. — Л.: Машиностроение, 1979, с. 314, рис. 10.4.

Авторское свидетельство СССР

Р" 1295392, кл. 0 06 F 9/22, 1986. (54) устРойс В0 MHKPOtIPoFPAteeoFO

УПРАВЛЕНИЯ (57) Изобретение относится к автоматике и вычислительной технике и может

2 быть использовано при создании микропрограммных автоматов управления устронстнами автоматики, в частности в контроллерах внешних устройств ЭВМ

"и интерфейсных узлах. Цель изобретения — повышение быстродействия устройства путем уменьшения задержки выдачи выходных сигналов при операциях условных переходов. Устройство содержит регистр микрокоманд 1, блок 2 памяти микрокоманд, коммутатор 3 адреса, коммутатор 4 условий, блок 5 местного управления. Цель достигается за счет того, что адрес перехода по наличию условия подготавливается заранее, а в момент смены условия формируется сигнал приема в регистр микрокоманд выходных сигналов с минимально возможной задержкой. 1 з,п. ф-лы, 3 ил.

1524049

Изобретение относится к автоматике и вычислительной технике и может быть использовано в контроллерах периферийных устройств и в управляющих автоматах.

Цель изобретения — повышение быстродействия устройства путем уменьшения задержки выдачи выходных сигналов при операциях условного перехода.

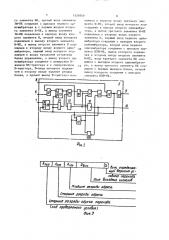

На фиг, 1 изображена функциональная схема устройства микропрограммного управления; на фиг. 2 — функциональная схема блока управления; на фиг, 3 — формат слова микрокоманды.

Устройство микропрограммного управления содержит регистр Микрокоманд, блок 2 памяти микрокоманд, коммутатор 3 адреса, коммутатор 4 условий, блок 5 местного управления, первьп» и второй входы задания режима

6 и 7 блока 5 местного управления, вход 8 его начальной установки, первый и второй выходы 9 и 10 блока 5 25 местного управления, выход II микроопераций устройства.

Блок 5 местного управления содержит (фиг. 2) первый элемент И-HE 12, RS-триггер 13, первый элемент И 14 первый элемент НЕ 15, элемент ИЛИ-НЕ

16, элемент ЗИ- НЕ 17, второй элемент

НЕ 18, первый одновибратор 19, второй элемент И-HE 20, второй элемент

И 21, второй одновибратор 22, D-триггер 23, третий элемент И-НЕ 24, третий элемент НЕ 25, Устройство работает следующим образом.

В исхОДКОм состоянии (по сигналу 40 начальной устайовки) регистр 1 обнулен и по нулевому адресу иэ блока 2 памяти иикрокоманд считывается первая микрокоманда программы. Считываемая микрокоманда может быть как ко- 45 мандой безусловного перехода, так и командой условного перехода.

При реализации команды безусловного перехода адрес. следующей микрокоманды записывается в поле младшей

А и старшей А« частей адреса регистра 1. На коммутатор 4 условий выдается код, которьп» обеспечивает выдачу логической "1" на вход 6 блока 5 местного управления, т.е, отключение внешних условий, а на вход 7 с блока 2 памяти микрокоманд поступает сигнал логической "1", обусловливающий формирование иа выходе 10 сигнала (Лог.0 ) управления коммутатором 3, который подключает на вход старших адресов блока в памяти микрокоманд адрес А . Блок 5 формирует также сигнал синхронизации на выходе

9. Выходные сигналы выдаются с регистра 1 по положительному фронту сигкала синхронизации на выходе 9.

Блок местного управления в случае безусловного перехода работает следующим образом. Сннхроимпульс отрицательной полярности, выработанный на предыдущем такте или по сигналу начальной установки, поступает с выхода одновибратора 22 на R-вход R-Sтриггера !"3 »» элемент И-НЕ 24, обеспечивая логическую "I на их выходах.

Длительность импульса синхронизации выбирается большей, чем задержка в коммутаторе условий 4. По отрицательному фронту этого импульса Р-триггер 23 принимает логическую "1" с входа 7. По этому же фронту запускается одновибратор 19, формируя импульс, запрещающий вьдачу сигнала синхронизации, блокируя элемент ЗИ-HE

17, т.е. удерживая выход последнего в состоянии логической "1", Длительность импульса, вырабатываемого одновибратором 19 с повторнь»ь» запуском, устанавливается большей времени задержки в блоке памяти микрокоманд

Выход управления коммутатором адреса остается в состоянии логического "0", обеспечивая пропускание на вход старших разрядов блока 2 памяти микрокоманд адреса А . По окончании действия сигнала на третьем входе элемента ЗИ-НЕ 17 появля" ется логическая "1", разрешая прохождение сигнала запуска одновибратора

22 и формирование импульса синхронизации на выходе 9, чем завершается такт работы устройства по безусловному переходу.

При реализации команды условного перехода существует два режима: ветвление по условию, ожидание условия.

Тип режима определяется разрядом микропамяти, подклкченнь»м к входу 7. При логической "I" выполняется режим ветвления, а при логическом "0" — режим ожидания условия.

Рассмотрим режим ветвления по условию.

При значении условия, равном 1, реализуется переход по адрес)! А, как и при безусловном переходе. При зна50

5 152404 чении условия, равном О, реализуется переход по адресу A« . Блок 5 местного управления в этом случае работает следующим образом. После снятия

"блокировки" с RS-триггера 13 и элемента И-НЕ 24 на инверсном выходе

R-S-триггера 13 остается логическая

11 11

1, а на выходе элемента И-НЕ 24 устанавливается логический "0", что !р приводит к появлению логической "1" на выходе 10. Передний фронт этого сигнала повторно запускает одновибратор 19, а коммутатор 3 переключается на пропускание адреса A Появление !5 логической "1" на выходе одновибратора 19 по истечении времени tð> (логи11 11 ческая 1 н а втором входе элемента

И-НЕ 2 О) приводит к запуску одно виб ратора 2 2, чем завершается цикл работы 20 по нулевому значению условия в режиме ветвления .

Рассмотрим режим ожидания условия .

При отсутствии усло вия устройство микропрограммного управления по окон- 25 ча нии импульса с одно виб р а то р а 1 9 и ереходит в статическое состояние ан ализ а условия и ожидает появление е г о единичного значения . Реализация перехода в этом режиме зависит о т момен- 30 та времени появления условия и сводится к двум вариантам: условие по я вляется раньше ч ем заканчивается сигнал выдаваемый с одно виб рато ра 1 9 .

Сигнал синхронизации на выходе 9 фо р35 мируется после окончания времени рз условие появляется по истечении вреMeHN

При этом режиме на вход блока 2 памяти микрокоманд пропускается адрес 40 д и к моменту прихода условия информация уже подготовлена на входе регистра 1 и выходных сигналов, Поэтому время реакции предлагаемого устройства на условие всегда одно и 45 то же и исключает время считывания с блока микрокоманд.

Формула изобретения

Устройство микропрограммного управления, содержащее блок местного управления, блок памяти микрокоманд, коммутатор адреса, коммутатор условий и реГистр микрокоманд, причем входы логических условий устройства соединены с информационными входами коммутатора условий, управляющий вход которого соединен с выходом кода логических условий регистра микрокоманд, выход кода логических условий которого соединен с первым информационным входом коммутатора адреса, второй информационный вход которого соединен с выходом поля старших разрядов адреса регистра микрокоманд, информационный вход которого соединен с выходом полей адреса и микроопераций блока памяти микрокоманд, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия путем уменьшения задержки выдачи выходных сигналов при операциях условного перехода, выход коммутатора условий соединен с первым входом задания режима блока управления, первый выход которого соединен с синхровходом регистра микрокоманд, выход поля микроопераций которого является выходом микроопераций устройства, выход поля младших разрядов адреса регистра микрокоманд соединен с входом младших разрядов адреса блока памяти микрокоманд, выход признак- условного перехода которого соединен с вторым входом задания режима блока управления, второй выход которого соединен с управляющим входом коммутатора адреса, выход |-.оторого соединен с входом старших разрядов адреса блока памяти микрокоманд, вход начальной установки устройства соединен с одноименными входами блока управления и регистра микрокоманд.

2. Устройство,по п.1, о т л и ч аю щ е е с я тем, что блок местного управления содержит первый! второй и третий элементы И-НЕ, первый и второй элементы И, первый, второй и третий элементы НЕ, первый и второй одновпбраторы,элемент ИЛИ-НЕ, элемент

ЗИ- IF., RS-триггер, D-триггер, при этом первый вход первого элемента

И-НЕ подключен к первому входу задания режима блока, а выход первого элемента И-HE подключен к инверсному

S-входу RS-триггера, инверсный выход которого подсоединен к первому входу первого элемента И и к входу первого элемента НЕ, выход которого соединен с вторым входом элемента ИЛИ-НЕ и первым входом элемента ЗИ-НЕ, а первый вход элемента ИЛИ-НЕ подключен к выходу первого элемента И, к входу второго элемента HF. и к второму входу первого элемента И-НЕ, второй вход элемента ЗИ-НЕ соединен с выходом второ1524049 го элемента НЕ, третий вход элемента

ЗИ-НЕ соединен с выходам первого адновибратора и с первым входом второго элемента И-НЕ, а выход элемента

ЗИ-НЕ подключен к первому входу второго элемента И, второй вход которого подключен к выходу второго элемента

И-НЕ, а выход второго элемента И подключен к второму входу второго одновибратора, первый вход которого подключен к входу начальной установки блока управления, а выход второго одновибратора соединен с инверсным Rвходом RS òðèããåðà и с синхровхадам

Э-триггера, D-вход которого подключен к второму входу задания режима блока, а прямой выход D-триггера падключен к первому входу третьего элемента И-НЕ, второй вход которого подсоединен к выходу второго одновибратора, а выход третьего элемента И-HE подключен к второму входу первого элемента И, первый вход первого одновибратара соединен с выходом второго одновибратора, второй вход первого аднавибратора соединен с выходом элемента ИЛИ-НЕ, выход которого подключен к второму входу второго элемента

И-НЕ, вход третьего элемента НЕ соединен с вьг одом второго одновибратора, а выход третьего элемента НЕ соединен с первым выходом блока, второй выход которого соединен с выходом элемента ИЛИ-НЕ, I