Устройство для контроля программ

Иллюстрации

Показать всеРеферат

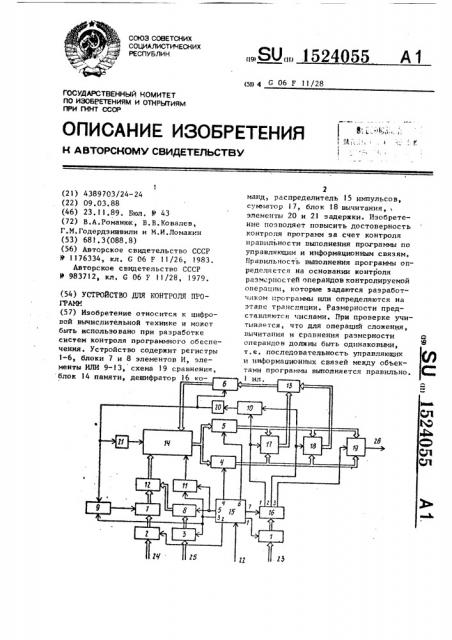

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке систем контроля программного обеспечения. Устройство содержит регистры 1 - 6, блоки 7 и 8 элементов И, элементы ИЛИ 9 - 13, блок 19 сравнения, блок 14 памяти, дешифратор 16 команд, распределитель 15 импульсов, сумматор 17, блок 18 вычитания, элементы 20 и 21 задержки. Изобретение позволяет повысить достоверность контроля программ за счет контроля правильности выполнения программы по управляющим и информационным связям. Правильность выполнения программы определяется на основании контроля "размерностей" операндов контролируемой операции, которые задаются разработчиком программы или определяются на этапе трансляции. "размерности" представляются числами. При проверке учитывается, что для операций сложения, вычитания и сравнения "размерности" операндов должны быть одинаковыми, т.е. последовательность управляющих и информационных связей между объектами программы выполняется правильно. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (gII g G 06 F 11/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ по ИЗОБеетениям и отнРытиям

ПРИ П1НТ СССР

К АBTOPCKOMV СВИДЕТЕЛЬСТВУ

1 (21) 4389703/24-24 (22) 09 ° 03.88 (46) 23.11.89. Бюл. М 43 (72) В.А.Романюк, В.В.Ковалев, Г.М.Годердзишвили и N.È,Ëoìàêêí (53) 681.3(088.8) (56) Авторское свидетельство СССР

9 II76334, кл. С 06 Р ll/26, 1983.

Авторское свидетельство СССР

Р 983712, кл. С 06 Р 11/28, 1979. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРОГРАМК (57) Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке систем контроля программного обеспечения. Устройство содержит регистры

1-6, блоки 7 и 8 элементов И, элементы ИЛИ 9-13, схема 19 сравнения, блок 14 памяти дешифратор 16 ко„„Я0„„1524055 A1

2 манд, распределитель ) 5 импульсов, сумматор 17 блок 18 вычитания, . элементы 20 и 21 задержки. Изобретение позволяет повысить достоверность контроля программ за счет контроля правильности выполнения программы по управляющим и информационным связям.

Правильность выполнения программы определяется на основании контроля разм рпостей операндов контролируемой операции, которые задаются разработчиком программы или определяются на этапе трансляции. Размерности представляются числами. При проверке учитывается, что для операций сложения, вычитания и сравнения размерности операндов должны быть одинаковыми, т.е. последовательность управляющих и информационных связей между объектами программы выполняется правильно.

1524055

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке систем контроля программного обеспечения °

Цель изобретения — повышение достоверности контроля устройства, На чертеже изображено предлагаемое устройство.

Контроль правильности выполнения программы, основанный на проверке правильности ее информационных и управляющих связей между объектами программы в процессе выполнения, поясняется примером.

Пусть выполняется оператор присваивания

P=A 4- С-(Е+Т) /В.

Для корректно написанной программы в контексте данного оператора должны выполняться следующие соотношения между физическими размерностями величин (P, А, С, Е, Т, В): (P)=)A % CJ )A) jCj;

C Pj = ((Е+Т) / В = (Е 1 (В) = (Т) (В)

Х= (Т), где Х) — физическая раэмернас-т объекта Х.

Проверка правильности выполня=мых соотношений по их размерностям и составляет сущность локализации ошибок при выполнении грограммя. Значения размерностей определяютс» разработчиком или на этапе трансляции программы и представляются числамп.

При проверке учитывается, что для операций сложения, вычитания, сравнения размерности операндов должны быть одинаковыми, т,е, последовательность управляющих и информационных связей между объектами программ выполняется правильно. Поэтому, при выполнении этих операций для контроля правильности выполнения программы необходимо сравнивать значения размерностей соответствующих операндов. Если значения размерностей совпадают, то программа выполняется правильно, если не совпадают, то произошло нарушение по упранляющим связям программы (для выполнения вовлечен какой-либо фрагмент программы из другого участка программы) или нарушение по информационным связям программы (для выполнения операции выбран не тот объект программы). В процессе выполнения программы размерности внутренних

?5 объектов программы (переменных) могут изменяться при выполнении операций сложения и деления. Поэтому при умножении и делении размерности операндов складываются и вычитаются соответственно. устройство для контроля хода программ содержит шесть регистров 1-6, первый и второй блоки элементов И 7 и 8, первый — третий элементы ИЛИ

9-11, два блока элементов ИЛИ 12 и г

13, блок 14 памяти, распределитель

15 импульсов, дешифратор 16 команд, сумматор 17, блок 18 вычитания, схемы 19 сравнения, первый и второй элементы задержки 20 и 21 тактовый вход 22, первый, второй, третий информационные входы устройства 23-25, Выход 26 ошибки устройства.

Дешифратор команд 16 имеет три вья:ода. Первый выход соответствует дешифрации команды умножения, второй — це.пения, третий — сложения, вычитания и сравнения.

Устройства работает следующим образом.

Перед началом раба гы устройства в память заносится информация, соответствующая выполняемой программе.

Она представляет собой участок памяти контролируемой программы, в катарам по адресам входных, промежуточных и выходных объектов (переменных) программы занесены соответствующие значения размерностей, остальные ячейки памяти абнулены. Значения размерностей представлены в виде чисел, которые по соответствующим правилам указываются разработчиком программы или определяются автоматически с помощью специального транслятор" При готовности устройства к работе на вход распределителя 15 импульсов начинают поступать сигналы с тактового входа 22 о том, что процессор подготовил к выполнению очередную команду, при зтам на информационные входы устройства 2325 поступают, соответственно код операции, адреса первого и второго операндов. С первого, второго и третьего выходов распределителя 15 импульсов выдаются последовательно управляющие сигналы, разрешающие запись информации с входов 24, 25 и 23 в первый 4, второй 3 и третий 2 регистры соответственно. Одновременно!

524055 6 третий управляющий сигнал распреде- первого элемента 20 задержки, где он лителя 15 имп л у ъсов через первый эле- задержинается на время, необходимое мент ИЛИ 9 аз ешает р решает прохождение ин- для выполнения операции сло ения в формации, соответствующей адресу пер- сумматоре 17. С выхода первого элеменвого операнда, с информационного вы- та 20 задержки управляющий сигнал хода второго регистра 2 через первый разрешает запись результата суммироэлемент И 7 и второй элемент ИЛИ 10 вания в регистр 6. Эта информация пока адресный вход блока 14 памяти. ступает на вход регистра 6 через пяЭтот же третий управляющий сигнал 1О тый элемент ИЛИ !3. В то же время распределителя 15 импульсов через сигнал с выхода первого элемента 20 третий элемент ИЛИ 11 элемент ИЛИ 1! разрешает счи- задержки через второй элемент 21 затывание инфо ма и р ц и из блока 14 памя- держки поступает на управляющий вход ти по адресу, который указан на ад- записи блока !4 памяти и одновременно ресном входе блока 14 памяти д о а 14 паляти, т.е. 15 разрешает прохождение информации об считывание инфо ма ии ф р ции, соответствую- адресе первого операнда с второго рещей значению " азме ности" р р ости", адрес ко- гистра 2 через первый блок элементов торой находится во втором регистре И 7 и второй элемент ИЛИ 10 соответ2. Управляющий сигнал с чет е с тнертого с T ûåíïî на адреcHbIA вход блока памявыхода распределителя 15 имп льс

5 и.1пульсов 20 ти 14. }>лок памяти производит запись разрешает запись считанного нз бло го нз блока кода размерностей, поступающего с

14 памяти крда "разме ностей" в шестого регистра 6 на информационгистр 4. иый вход бло;а !4 памяти по адресу, Аналогично управляющий сигнал с указанному на адресном входе блока пятого выхода распределителя !5 им- 25 14 памяти, т,е, по адресу первого пульсов разрешает считывание кода операнда выполняемой операции. размерностей" соответств ю е

» етству ющ< го ад- Аналоги ьно осуществляется изменересу вто ого опе р операнда, которьпi ио- нне значения размерностей", если

»! ступает из т етьего 3 .а.р .; 1 .истра через увравля"швй сигнал поступает с второвторой элемент И 8 и элемент 11»И 10 80 го выхода дешифратора 16 команд, что

Г на адресный нхо, блока 4 д лока !4 памяти, соотнетству т выполнению операции сигнал считывания поступает через деления. третии элемент ИЛИ !l. Управляющий Если дешифратор 16 команд опредесигнал с шестого ше т го выхода распредели- ляет команду сложения, вычитания или теля импульсов разрешает запись счи- сравнения, то упранляющий сигнал под размерностей в пятый является на третьем выходе, Он порегистр 5. ступает на управляющий вход схемы 19

Таким об а разом, в четвертом и пя- сраннения. Прн этом в схеме 19 сравтом регистрах 4 и 5 находится соот- нения происходит сравнение кодов, поветствующий код нразмерностей" 4п ступающих с регистров 4 и 5. Если первого и второго операндов конт- значепия "размерностей" совпадают

»

Уп ав т.е. коды равны то контролируема правляющий сигнал с седьмого ны- программа выполняется правильно. хода распределителя 15 импульсов по- Если значения "размерностей" не ступает на управляющий вход дешифра- 45 совпадают» -.î обнару..кена ошибка H тора 16 команд, который дешифрует с вьг;;ода схелы сравнения на выход код операции и на его выходе (однол1 устройства 26 поступает сигнал ошибиз трех) появляется управляющий снгки. нал, соответствующий коду операции.

Е сли выполняется операция умножения, gp 9 о p v у л то управляющий сигнал появляется на первом выходе дешифратора 16 команд. Устройство для контроля программ, Этот сигнал поступает на управляющий содержащее шесть регистров, первый вход сумматора 17 и разрешает выпол- и второй блоки элементов И, первый нить операцию сложения значений "раз- >5 и второй элементы ИЛИ, блок памяти, 1! мерностен, находящихся в четвертом схема сраннсния и распределитель им4 и пятом 5 регистрах. Одновременно пульсов, причем первый выход распреэтот управляющий сигнал поступает че- делителя импульсов соединен с входом рез четвертый элемент ИЛИ 12 на вход записи перного регистра, выход кото!

524055

Составитель Сигалов

Редактор Л, Зайцева ТехрелЛ. Олийнык Корректор О, Кравцова

Заказ 7044/50 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям прн ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 рого соединен с первым входом первого элемента И, о т л и ч а ю щ е— е с я тем, что, с целью повьппения достоверности контроля, в устройство введены третий элемент ИЛИ и два блока элементов ИЛИ, дешифратор команд, сумматор, блок вычитания, первый и второй элементы задержки, причем входы адреса первого и второго операндов и кода операции устройства соединены с информационными входами соответственно первого, второго и третьего регистров, вход синхронизации устройства соединен с тактовым входом 15 распределителя импульсов, второй выход которого соединен с входом записи третьего регистра, выход которого соединен с входом дешифратора команд, третий выход распределителя импуль- 20 сов соединен с входом записи второго регистра, с первым входом первого элемента ИЛИ, выход которого соединен с вторым входом первого блока элементов И, выход которого соединен с 25 первым входои первого блока элементов ИЛИ, третий, четвертый, пятый, шестой и седьмой выходы распределителя импульсов соединены соответственно с первым входом второго элемента

ИЛИ, с входом записи четвертого регистра, с вторыи входом второго элемента ИЛИ, с входом записи пятого регистра и с тактовым входом депжфратора команд, первый, второй и третий выходы которого соединены соответственно с первьп входом третьего элемента ИЛИ, с вторым входом третьего элемента ИЛИ и с тактовым входои схемы сравнения, пятый выход распреде- 40 лителя импульсов соединен с управляющим входом второго блока элементов

И, выход которого соединен с вторым входом первого блока элементов ИЛИ, выход которого соединен с адресныи входом блока памяти, выход второго регистра соединен с информационным: входом второго блока элементов И, выход второго элемента ИЛИ соединен с входом чтения блока памяти, информационный выход которого соединен с инг формационными входами четвертого и пя то го ре гис тров, выход третьего элемента ИЛИ соединен через первый элемент задержки с входом записи шестого регистра>с вторым входом первого элемента ИЛИ и через второй элемент задержки с входом записи блока памяти, выход четвертого регистра соединен с входом первого операнда сумматора, с входом первого операнда блока вычитания и с первым входои схемы сравнения, выход которой является выходом ошибки устройства, выход пятого регистра соединен с вторым входои схемы сравнения, с входом второго операнда блока вычитания и с входои второго операнда суыаатора, выход которого соединен с первым входом второго блока элементов ИЛИ, первый и второй выходы дешифратора команд соединены с тактовьач входом сумматора и с тактовым входои блока вычитания, выход которого соединен с вторыи входом второго блока элементов ИЛИ, выход которого соединен с инфориационнмч входои шестого регистра, выход которого соединен с ин4юриационныи входои блока памяти.