Устройство для адресации к памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении систем памяти для микроЭВМ. Целью изобретения является сокращение аппаратных затрат за счет изменения алгоритма функционирования блока 5 контроля обращений. Устройство содержит регистр 1 данных, элементы И 2 и 6, блок 3 постоянной памяти, буферный регистр 4. Аппаратные затраты устройства сокращены за счет уменьшения числа элементов блока 5 контроля обращений. 1 з.п.ф-лы, 2 ил.

СОЮЗ СОВЕТСНИК

СООИАЛИСТИЧЕСНИК

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

10 11 72 13

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4386369/24-24 (22) 02.03.88 (46) 23.11 89. Бюл. М 43 (72) В.А.Грехнев и Ю.А.Морозов (53) 681.325(088.8) (56) Дж.Хилбурн, П.Джулия. МикроЭВМ и микропроцессоры. М., 1979, с. 295, 296.

Авторское свидетельство СССР

У 991427, кл. С 06 F 9/34, 1980. (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ K ПAМЯТИ (57) Изобретение относится к вычислиÄÄSUÄÄ 15240 6 А1 511 4 G 06 F 12/00

2 тельной технике и может быть использовано при построении систем памяти для микроЭВМ. Целью изобретения является сокращение аппаратных затрат за счет изменения алгоритма функционирования блока 5 контроля обращений.

Устройство содержит регистр 1 данных, элементы И 2 и 6, блок 3 постоянной памяти, буферньй регистр 4, Й паратные затраты устройства сокращены за счет уменьшения числа элементов блока 5 контроля обращений. 1 з.п. ф-лы, 2 ил.

1524056

20 с

Изобретение относится к вычислительной технике и может быть использовано при построении систем памяти микроЭВМ.

Цель изобретения — сокращение аппаратных затрат за счет изменения алгоритма функционирования блока контроля обращений.

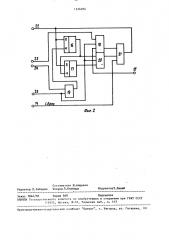

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 функциональная схема блока контроля обращений.

Устройство (фиг ° 1) содержит регистр 1 данных, первый элемент И 2, блок 3 постоянной памяти, буферный регистр 4, блок 5 контроля обращений, второй элемент И 6, информационный вход 7 устройства, тактовый вход 8 устройства, вход 9 синхронизации устройства, информационный выход 10 устройства, входы 11 "Ждать", 12 "Готов" и 13 "Считывание первого байта" устройства, вход 14 сброса устройства, выход 15 управления устройства.

Блок контроля обращений (фиг. 2) содержит первый 16 и второй 17 триггеры, первый 18, BTGpoé 19 и третий

20 элементы И, элемент ИЛИ 21 вьг .од

22 сброса блока, первый 23 и второй

24 информационные входы блока, вход

25 управления блока.

Устройство работает следующим образом.

В момент времени, когда на шину данных микроЭВМ помещается информация о состоянии центрального процессора (ЦП) микроЭВМ, при совпадении тактового сигнала и сигнала синхроннзации элемент И 2 вырабатывает сигнал записи, и регистр 1 данных запоминает информацию о состоянии ЦП и выдает ее на информационный выход устройства. Если на входы поступают сигналы "Готов", "Ждать" и "Считывание первого байта", то результат анализа первого байта команды, поступающий в это время с выхода блока 3 постоянной памяти на буферный регистр

4, записывается при помощи сигнала записи, выработанного вторым элементом И 6. В результате этого в буферном регистре 4 оказывается записанной информация о длине в байтах выполняемой в настоящий момент ЦП микроЭВМ команды.

Если выполняемая команда однобайтовая, то на выходе блока 5 контроля обращений, который является управляющим выходом 15 устройства, сигнал обращения к подсистеме программной памяти не вырабатывается. Если команда двух- или трехбайтовая, то в течение одного или двух машинных циклов ПП микроЭВМ, отсчет которых ведется по тактовому сигналу и сигналу синхронизации, поступающих на блок

5 контроля .обращений, последний вырабатывает сигнал обращения к программной памяти, который выдается на

J управляющий выход устройства. После считывания. последнего байта команды блок 5 контроля обращений вырабатывает сигнал сброса, который, поступая иа буферный регистр 4, cGpacblBa ет его, Таким образом, устройство оказывается готовым к анализу следующей команды. Сброс блока 5 контроля обращений и буферного регистра 4 может осуществляться и с помощью сигнала Сброс", поступающего на вход

14 сброса устройства. Это необходимо, например, при включении устройства, Таким образом, сигнал считывания первого байта команды дополняется сигналом обращения к программной памяти, который вырабатывается при считывании второго и третьего байтов команды. Совокупность этих сигналов позволяет легко выделить подсистему программной памяти, Причем большой ее объем (65 Кбайт) позволяет значительно облегчить программирование °

В момент считывания ЦП с шины данных кода команды на выходах блока

3 постоянной памяти появляются сигналы, соответствующие той команде, код которой находится в это время на шине данных. Блок 5 программируется так, что, если команда однобайтовая, то сигналы отсутствуют на выходах, если команда двухбайтовая, то сигналы появляются и на выходе старшего разряда и на выходе мпадшего разряда, если команда трехбайтовая, то сигиал появляется только на выходе мпадшего разряда. Таким образом, в момент считывания первого байта команды в буферный регистр 4 оказывается записанным код, содержащий информацию о том, будет ли ЦП микроЭВМ считывать второй и третий байть1 команды или нет. Если команда однобайтовая, то синхроимпульсы с, выхода элемента

И 19 не пройдут на тактовый вход первого триггера 16, и схема останется

5 152405 в исходном состоянии. Если команда двух- или трехбайтовая, то после приема информации в регистр 4 происходит установка первого триггера 16 в единичное состояние. При считывании второго байта команды синхросигнал с выхода элемента И 19 снова поступит на тактовый вход первого триггера 16 и перебросит его в нулевое состояние, при этом второй триггер 17 установится в единичное состояние. При считывании третьего байта, если команда двухбайтовая, синхросигнал пройдет через элементы 19 и 21 и сбросит 15 триггеры 6 и 17, а также регистр 4, если команда трехбайтовая, то сброса не произойдет, первый триггер 16 снова установится в единичное состояние, а сброс триггеров произойдет gp через элементы 20 и 21 при поступлении четвертого синхросигнала. Сигнал с выхода второго триггера 17 подается на управляющий выход устройства .и означает, что центральный про- 25 цессор считывает второй и третий байты команды. Сброс всех триггеров может быть произведен также общим сигналом "Сброс" через элемент ИЛИ 21.

Фо р м ул а и з о б р е т е н и я

1, Устройство для адресапии к памяти, содержащее регистр данных, блок постоянной памяти, первый и вто35 рой элементы И, буферный регистр и блок контроля обращений, причем выход первого элемента И соединен с входом записи регистра данных, информационный вход устройства соединен с адрес- 40 ным входом блока постоянной памяти, выход которого соединен с информационным входом буферного регистра, первый и второй информационные выходы которого соединены соответственно с первым и вторым информационными входами блока контроля обращений, выход сброса которого соединен с входом сброса буферного регистра, вход записи которого соединен с выходом второ- 5р го элемента И, первый, второй и тре6 б тий входы которого являются соответственно входами Ждать", "Готов и Считывание первого байта" устройства, информационный вход регистра данных соединен с информационным входом устройства, выход регистра данных соединен с информационным выходом устройства, первый и второй входы первого элемента И являются соответственно тактовым входом и входом синхронизации устройства, вход сброса устройства соединен с входом сброса блока контроля обращений, выход управления которого является выходом управления устройства, о т л и ч аю щ е е с я тем, что, с целью сокращения аппаратных затрат за счет изменения алгоритма функционирования блока контроля обращений, выход первого элемента И соединен с входом управления блока контроля обращений.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок контроля обращений содержит первый и второй триггеры, первый, второй и третий элементы И и элемент ЙЛИ, причем первый и второй информационные входы блока соединены соответственно с первыми входаьы первого и"второго элементов И, выходы первого и третьего элементов И соединены соответственно с первым и вторым входамп элемента ИЛИ, выход которого соединен с входами сброса первого и второго триггеров и с выходом сброса блока, вход сброса блока соединен с третьим входом элемента ИЛИ, выход второго элемента И соединен с входом установки первого триггера, выход первого триггера соединен с входом установки второго триггера и с первым входом третьего элемента И, второй вход которого соединен с вторыми входами первого и второго элемеитов И и с входом управления блока, выход второго триггера соединен с третьими входами первого и третьего элементов И и с выходом управления блока.

1524056

Составитель И.Андреев

Редактор Л.Зайцева Техред Л.Олийнык

КорректорТ.Палий

Заказ 7044/50 Тираж 66В Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101