Устройство для управления динамической памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах микропроцессорных систем. Целью изобретения является упрощение устройства и расширение функциональных возможностей за счет независимости работы от типа системного контроллера. Устройство содержит формирователь, первый и второй счетчики строк регенерации, дешифратор, мультиплексор адресов, регистр данных и формирователь управляющих сигналов, включающий D-триггер, RS-триггер, первый и второй одновибраторы, первый и второй элементы ИЛИ, элемент И и элемент НЕ. Устройство обеспечивает правильный обмен данными между процессором и памятью при любом типе системного контроллера /КР580 ВК38 или КР580 ВК28/ и системном генераторе КР 580ГФ24 и возможность работы памяти с контроллером прямого доступа КР580ВТ57 при "скрытой" регенерации в любом режиме работы процессора и любом стандартном режиме прямого обмена между памятью и устройствами ввода/вывода. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) (111, (51)4 G 11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4351548/24-24 (22) 24.11.87 (46) 23,11.89, Бюл. 11 43 (71) Горьковский политехнический институт (72) IO.Н.Киселев (53) 681,327.6 (088.8) (56) Авторское свидетельство СССР

У 1246135, кл. G 11 С 7/00, 1984.

Еремин Ю,A., Морозов A,Ã, Контроллер динамического ОЗУ для микропроцессорных устройств,. — Микропроцессорные средства и системы, 1986, !(3, с. 47. (54) УСТРО!!СТВО ДЛЯ УПРАВЛЕНИЯ ДИНАМИЧЕСКО!1 ПЛМЧТЬИ (57) Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах микропроцессорных систем. Целью изобретения является упрощение устройства и расширение функциональных возможИзобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах микропроцессорных систем, Целью изобретения является упрощение устройства и расширение функциональных возможностей за счет независимости работы от типа системного контроллера.

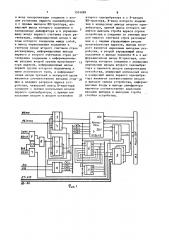

На фиг. 1 представлена схема устройства для управления динамической памятью; на фиг. 2 и 3 — временные диаграммы, поясняющие работу устройства, 2 ностей за счет независимости работы от типа системного контроллера. Устройство содержит формирователь, первый и второй счетчики строк регенерации, дешифратор, мультиплексор адресов, регистр данных и формирователь управляющих сигналов, включающий

D-триггер, RS — триггер, первый и второй одновибраторы, первый и второй элементы ИЛИ, элемент И и элемент НЕ.

Устройство обеспечивает правильный обмен данными между процессором и памятью при любом типе системного контроллера (KP580 ВК38 или КР580 ВК28) и системном генераторе KP 580ГФ24 и возможность работы памяти с контроллером прямого доступа КР580ВТ57 при искрытойи регенерации в любом режиме работы процессора и любом стандартном режиме прямого обмена между памятью и устройствами ввода/вывода, 3 ил.

Устройство содержит D-триггер 1, RS-триггер 2, одновибраторы 3 и 4, регистр 5 данных, элементы ИЛИ 6 и 7, элемент И 8, мультиплексор 9 адресов, первый 10 и второй ll счетчики строк регенерации, дешифратор 12, элемент

НЕ 13. На фиг, 1 показано также подключение устройства к накопителю и шине микроЭВМ.

Элементы 1 — 4, 6 — 8, 13 составляют формирователь управляющих сигналов.

Работа устройства с процессором (фиг. 2).

1524089

В отсутствие сигнала SYNC процес-, сора по отрицательному фронту сигнала ц периодически (в каждом такте)

2 запускается одновибратор 4, формируя паузу между сигналами RAS накопителя, Длительность паузы между сигналами

RAS устанавливается в соответствии с техническими параметрами БИС ЗУ так, чтобы между началом очередного сиг" нала RAS и положительным фронтом ближайшего сигнала lp имелся временной интервал, который требуется по

ТУ между сигналами RAS u CAS.

Триггеры 1 и 2, одновибратор 3 на- 1 ходятся в IIсходном,состоянии, мультиплексор 9 передает на адресные входы накопителя код адреса со счетчиков

10 и 11 строк регенерации, Режим регенерации последовательных строк накопителя продолжается до появления сигнала SYNC (начало цикла) процессора.

Сигнал SYNC, поступая на мультиплексор 9 в первом такте цикла, обес- 25 печивает в паузе между сигналами RAS подключение к адресным входам накопителя адресов AO-A6 образующих адрес строки ячейки памяти, к которой обращается процессор, Кроме того, сигнал

SYNC формирует.ся триггером 1 во втором такте процессорного цикла по положительному фронту q, вызывая блокировку запуска одновибратора 4 во втором такте, Это приводит к увеличению длительности сигнала RAS на

35 время обращения к накопителю со стороны процессора.

Начало сигнала RAS при наличии сигнала SYNC обеспечивает передачу

40 мультиплексором 9 кода адреса столбца Л7-Л13 ячейки памяти. Срабатывание триггера 1 вызывает переключение триггера 2, который формирует сигнал

CAS — сигнал фиксации адреса столбца

45 в накопителе. Поскольку сигнал SYNC процессора заканчивается во втором такте процессорного цикла, триггер 1 вернется в исходное состояние по положительному фронту ц в такте, который следует за вторым тактом (типовой 50 третий такт, либо такт ожидания при отсутствии сигнала READY на входе процессора), и снимает блокировку запуска одновибратора 4 и сигнал усlI tt т ано вки триггера 2 в состояние 1 . 5 5

Таким образом, в следующем такте по отрицательному фронту сигнала запускается одновибратор 4 и триг1 гер 2 возвращается в исходное состояние, т. е. заканчивается формирование сигналов RAS и CAS, Следу1ощий сигнал HAS вызывает уже цикл регенерации накопителя.

Поскольку счетчик регенерации инкрементируется по концу сигнала РАЯ, а в цикле обращения к накопителю строка, код которой был сформирован в счетчике к началу обращения, не была регенерирована, увеличение содержимого счетчиков 10 и 11 блокируется переводом счетчика 10 в режим перезаписи кода по сигналу CAS °

В начале любого обращения к памяти накопитель находится в режиме выдачи данных в регистр 5 по сигналу CAS.

Наличие регистра 5 позволяет ограничиться одним циклом обращения к накопителю по чтению, даже если режим чтения в процессоре продолжается бесконечно долго, Выдача данных из регистра 5 на шину данных микроЭВМ разрешается только .сигналом MENR при отсутствии сигнала БЛК (блокировки обращения в памяти).

Сигнал записи в накопитель формируется одновибратором 3 при наличии сигнала МКМ11. Запуск одновибратора 3 разрешается в течение длительного сиг -:ала CAS в момент возврата триггера 1 в исходное состояние. Длительность сигнала hIE определяется длительностью положительной полуволны сигнала (не менее 200 нс, что соответствует ТУ на БИС динамической памяти серии К565) при условии, что хронирующая цепь одновибратора 3 рассчитана на формирование несколько большей длительности. Окончание сигнала ЫЕ совпадает с концом сигнала CAS, Таким образом при выдаче данных из процессора в память в накопителе вначал» выполняется чтение по требуемому адресу, а затем запись данных процессор» по тому же адресу (использован режим БИС ЗУ вСчитывание — модификация — запись" ).

Поскольку моменты начала формирования сигналов МБМК и IKHti для нормапьной работы узла управления и выполнения правильного обмена данными между процессором и памятью не важны, схема успешно работает при различных стандартных системных контроллерах.

При необходимости организаций банков памяти сигнал CAS, формируемый триггером 2, должен переключаться на

089 6

"скрытая" регенерация памяти н в тактах ожидания.

Таким образом, в предлагаемом устройстве управления идентификация об5 ращения к памяти со стороны процессора сигналом SYNC позволлет использовать это устройство при любом типе системного контроллера КР580ВК38 или КР580ВК28; тактовой последовательностью является системный сигнал, вырабатываемый стандартным системным генератором КР580ГФ24.

Применение запоминающего регистра

15 на выходе накопителя позволяет осуществить правильный обмен данными между памятью и процессором в автоматическом режиме и режиме ожидания,я также между памятью и внешним устройст20 вом в режиме прямого доступа под управ— пением стандартного контроллера ПД типа КР580ВК57, Использование режима Чтение-модификация-запись" в накопителе динамического типа упрощает схему управле5 1524 тот илн иной банк (страницу) накопителя кодом старших разрядов адресной шины.

Роль этого переключателя в схеме (фиг. 2) выполняет дешифратор 12, Блокировка обращения к памяти достигается запретом формирования сигнала на выходе элемента 8 и запретом чтения состояния регистра 5. Сигнал блокировки обращения к памяти должен быть подан не позднее чем за 100 нс до начала сигнала RAS в цикле обращения к памяти.

Предлагаемая схема управления обеспечивает »»скрытую" регенерацию последовательных строк накопителя динамического типа с темпом одна строка за один цикл процессора.

Работа устройства управления в режиме прямого доступа к памяти под управлением стандартного контроллера

ПД типа КР580ВТ57 (фиг. 3).

Переход процессора в режим захвата шин происходит в конце такта ТЗ процессорного цикла, когда обмен данными между процессором и памя» ью или регистром внешнего устройства завершен. Передача управления шинами микроЭВМ контроллеру прямого доступа

КР580ВТ57 вызывает в нем формирование циклов ПД, подобных циклу считывания управления памятью и регистрации ввода — вывода. В предлагаемом устройстве управления идентификация цикла прямого доступа вызывается сигналом ADE.ST. — стробом запоминания старшего байта адреса ячейки памяти, к которой обращается контроллер ПД.

Обращение к ОЗУ происходит также как при взаимодействии с процессором при условии программирования БИС ПД на режим удлиненной записи в память, Невыполнение этого условия (обычная запись) может привести к пропуску сигнала МЕМ1» за счет его значетельного ния, 30 Устрой ст во длл у правлен»»я динам»»ческой памятью, содержащее формирователь управляющих сигналов, мультипликатор адресов, дешшфратор, первый счетчик строк регенерации, о т л и ч а ющ е е с я тем, что, с целью

35 упрощенил устройства и расширения функциональных возможностей за счет обеспечения независимости работы от типа системного контроллера, в устройство введен регистр даш ых, второй счетчик строк регенерации, а формирователь управляющих сигналов содержит

D-триггер, RS-триггер, первый и второй одновибраторы, первый и второ»»

45 элементы HlPi элемент И и элемент HE причем входы первого элемента ИЛИ являются входами синхронизации и строба адреса устройства, а выход соединен с первым входом элемента И, второй вход которого подключен к выходу элемента

НЕ, вход которого является входом блокировки устройства и соединен с первым входом второго элемента ИЛИ, второй вход которого является входом

55 чтения устройства, а выход подключен к входу выборки регистра данных, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства, запаздывания по отношению к моменту анализа этого сигнала в узле управления (по ТУ БИС КР 580ВТ57 задержка сигнала 1»1ЕМ1» относительно начала такта S3 может составлять 250 нс) °

В циклах ПД по чтению ОЗУ режим удлиненной записи в контроллере ПД может не использоваться. На фиг. 3 показано взаимодействие устройства управления и контроллера прямого доступа в режимах чтения памяти и записи в память ° Также как при работе с процессором в режиме ПД выполняется

Ф о р м у л а и з о б р е т е н и я

1524089 а вход синхронизации соединен с входом установки первого одновибратора и с прямым выходом RS-триггера, инверсный выход которого подключен к

5 синхровходу дешифратора и к управляющему входу первого счетчика строк регенерации, информационные входы и выходы которого соединены между собой, а выход переполнения подключен к счетному входу второго счетчика строк регенерации, информационные выходы первого и второго счетчиков строк регенерации соединены с информационными входами второй группы мультиплексора адресов, информационные входы первой группы которого подключены к шине логического нуля, а информационные входы третьей и четвертой групп являются соответственно входами стар- 20 ших и младших разрядов адреса устройства, инверсный выход 0-триггера соединен с прямым импульсным входом первого одновибратора, с прямым импульсным входом и входом установки 25 второго одновибратора и e S-входом

RS-триггера, R-вход которого подключен к инверсному выходу второго одновибратора, прямой выход которого является выходом строба адреса строки устройства и соединен со счетным входом первого счетчика строк регенерации и с первым управляющим входом мультиплексора адресов, выходы которого являются адресными выходами устройства, а второй управляющий вход подключен к выходу элемента И и к информационному входу D-триггера, синхровход которого соединен с инверсным импульсным входом второго одновибратора и является входом синхронизации устройства, инверсный импульсный вход и инверсный зыход первого одновибратора являются соответственно входом и выходом записи устройства, информационные входы и выходы дешифратора являются соответственно адресными входами выборки и выходами строба столбца устройства, )524089

1524089

Ч

1 ф ь ф

Составитель О,Исаев

Техред A.Kðàí÷óê

Корректор Т,Иалец

Редактор A. Шандор

Заказ 7048j52 Тираж 558 Под пи сно е

ВНИИПИ 1 осударственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, 11осква, 11(-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент, г. Ужгород, ул. Гагарина, 101