Сумматор n-разрядного единичного кода

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и автоматике. Его использование в системах обработки информации, работающих с единичным кодом, позволяет упростить сумматор и повысить его быстродействие. Сумматор содержит преобразователи 1,2 кодов и логические ячейки 3. Логическая ячейка содержит элемент ИЛИ и элемент И. 6 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (59 4 H 03 M 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ДО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4399466/24-24 (22) 29,03.88 (46) 23.11.89. Бюл, У 43 (72) А,С.Серков, Б.М.Солодухин, С.М.Федоров и Л.Н.Ким (53) 68).32 (088,8) (56) Авторское свидетельство СССР

У l34I723, кл. H 03 M 7/00, 06.02.86. (54) СУИИАТОР N-РАЗРЯДНОГО ЕДИНИЧНОГО

КОДА

„.80„„1524183 А 1

2 (57) Изобретение относится к вычислительной технике и автоматике. Его использование в системах обработки информации, работакщих с единичным кодом, позволяет упростить сумматор и повысить его быстродействие. Сумматор содержит преобразователи 1, 2. кодов и логические ячейки 3. Логическая ячейка содержит элемент ИЛИ и элемент И.,б ил.

1524)83

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации, работающих с единичным кодом.

Цель изобретения — повышение быстродействия и упрощение сумматора.

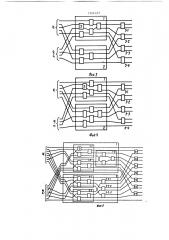

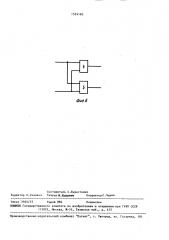

На фиг,1 и 2 представлены функциональные схемы сумматоров для случаев нечетного и четного числа разрядов входных кодов соответственно; на фиг.3 — 5 функциональные схемы сумматоров для различных вариантов входных кодов; на фиг.б — функциональная схема логической ячейки.

Сумматор (фиг.1) содержит преобразователи 1 и 2 кодов и логические ячейки 3.

Логическая ячейка (фиг.Ь) содержит 20 элемент ИЛИ 4 и элемент И 5.

Преобразователи кодов идентичны известным пирамидальным блокам, Сумматор работает следующим образом. 25

На группы иэ m и и-m входных шин подаются коды из логических единиц и нулей, причем логические "1" сгруппированы без пропусков на первых шинах а логические "0II — на послед1 30 них шинах.

При наличии на входах ячейки 3 двух логических "0" или двух логических "1" на обоих выходах этой ячейки присутствуют одинаковые соответствующие сигналы (нули или единицы) .

Если на одном из входов ячейки 3 присутствует логическая 1", а на другом входе этой же ячейки логичес- 40 кий "0", то на первом выходе логиII II ческая 1, а на втором логический

"0", т.е. логические "1", проходя через ячейку 3, смещаются в сторону ее первого выхода. Аналогично при прохождении через преобразователи 1 и 2 кодов логические "1" группируются на их первых выходах. В результате на выходных шинах преобразователя кодов формируется код, в котором число логических "1" равно сумме логических

"1" на его группах из m и и-m входных шин, и размещены все логические 1 на первых выходных шинах. ьормула и эоб ретения

Сумматор N-разрядного единичного кода, содержащий первый и второй преобразователи кодов, входы которых являются соответствующими входами сумматора, первый выход первого пре" образователя кодов является первым выходом сумматора, о т л и ч а ю— шийся тем, что, с целью повышения быстродействия и упрощения суми матора, в него введены (- — 1) при и-1 eTHoì и (— ---) при нечетном и

2 (п l, N) логических ячеек, первые входы которых подключены к соответствующим выходам первого преобразователя кодов, начиная с второго, вторые входы логических ячеек подключены к соответствующим выходам второго преобразователя кодов, кроме последнего, для четного и а для нечетного ив к последнему выходу второго преобразователя кодов, выходы логических ячеек являются вторыми выходами сум-. матора.

1524133 и

1524183

Составитель С.Берестевич

Редактор О. Головач Техред К.Ходанич Корректор С.Черни

Заказ 7055/57 Тирах 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям прн ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101