Устройство детектирования амплитудно-модулированных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение помехозащищенности по отношению к узкополосным помехам. Устройство содержит блок детектирования 1 сигнала верхней боковой полосы, состоящей из синхронного детектора 3 и сумматора 11, амплитудный детектор 2, блок регенерации 5 несущей, блок детектирования 6 сигнала нижней боковой полосы, состоящий из синхронного детектора 4, фазовращателя 10 на 90° и вычитателя 12, блок выбора 7 полосы, коммутатор 8 и фазовый расщепитель 9. Если помехой поражена верхняя (нижняя) боковая полоса принимаемого сигнала, то блоком выбора 7 на выход устройства через коммутатор 8 коммутируется напряжение сигнала нижней (верхней) боковой полосы. Если помеха отсутствует , то на выход устройства через коммутатор 8 подается суммарный сигнал обеих боковых полос, получаемый на выходе детектора 2. Устройство по п. 2 ф-лы отличается выполнением блока выбора 7. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (11) А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ С8ИДЕТЕЛЬСТВУ

2 из синхронного детектора 3 и сумматора 11, амплитудный детектор 2, блок регенерации 5 несущей, блок детектирования 6 сигнала нижней боковой полосы, состоящий из синхронного

О детектора 4, фазовращателя 1О на 90 и вычитателя 12, блок выбора 7 полосы, коммутатор 8 и фазовый расщепитель 9. Если помехой поражена верхняя (нижняя) боковая полоса принимаемого сигнала, то блоком выбора 7 на выход устройства через коммутатор 8 коммутируется напряжение сигнала нижней (верхней) боковой полосы. Если помеха отсутствует, то на выход устройства через коммутатор 8 подается суммарный сигнал обеих боковых полос, получаемый на выходе детектора 2. Устройство по п. 2 ф-лы отличается выполнением блока выбора 7. 1 з.п. ф-лы, 2 ил.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР! (21) 4362097/24-09 . (22) 11.01,88 (46) 30.11.89. Вюл. )) 44 (72) К.К,Венскаускас, Е.М.Николаев, И.А.Осокин и Т,И.Иульц (53) 621.396(088.8) (56) Fumeno I., Inone М. А Sideband

Selective receiver., In "Proceeaiп8а of the 6 " NHK Technical Symposium, Tokyo, April 1962, р. 46-5 1.

Заявка Великобритании

1 1593834, кл. Н 04 В 1/10, 1981. (54) УСТРОЙСТВО ДЕТЕКТИРОВАНИ)!

АМПЛИТУДНО-МОДУЛИРОВАННЫХ СИГНАЛОВ (57) Изобретение относится к радио— технике. Цель изобретения — повышение помехозащищенности по отношению к узкополосным помехам. Устройство содержит блок детектирования 1 сигнала верхней боковой полосы, состоящий

151) 4 Н 03 D 1 04 Н 04 В 1 10

1525862 (8) Изобретение относится к радиотехнике и может быть использовано в составе приеиников амплитудно-модулированных сигналов.

Цель изобретения — повышение поиехозащищенкости по отношению к узкополосным поиехаи.

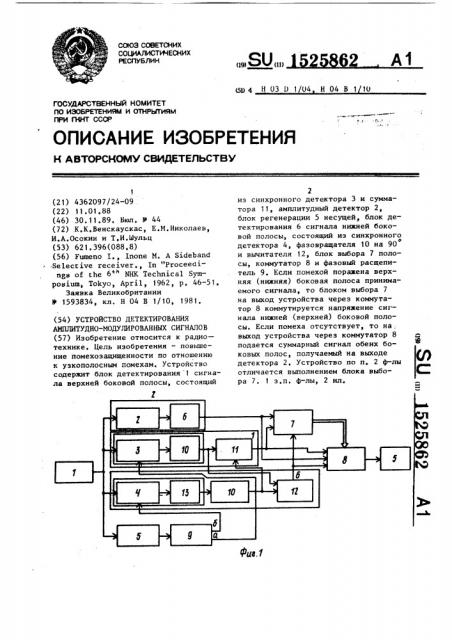

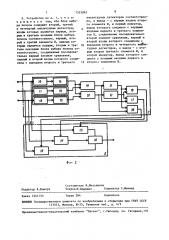

На фиг. 1 представлена структурная электрическая схема устройства 10 детектирования амплитудно"модулированных сигналов; на фиг. 2 — структурные электрические схемы блока выбора полосы и коммутатора.

Устройство детектирования амплитудно-модулированных сигналов содержит блок 1 детектирования сигнала верхней боковой полосы, первый аиплитудный детектор 2, первый синхрон.MblA sTe To 3, sTo o cHHxpoHHHA детектор 4, блок 5 регенерации несущей, блок 6 детектирования сигналов нижней боковой полосы, блок 7 выбора полосы, коммутатор 8, фазоый расщепитель 9, фазовращатель на 25

О 10, сумматор 11, вычитатель 12.

Блок 7 выбора полосы содержит второй, третий и четвертый амплитудные детекторы 13, 14 и 15, первьй, второй и третий элемечты И 16, 17, 18,30 первый и второй элементы 19 и 20 сравнения, первый и второй инверторы 21 и 22.

Коьекутатор 8 содержит первый, второй и третий ключи 23, 24 и 25 и второй сумиатор 26.

Устройство работает следующим образом, При отсутствии помех напряжение сигнала нв входе устройства которое 40 иокно представить в виде

m °

U = U cos t + -+ U cos(+

+ak. )t + - U cos(w, +ьЛ.„И, (1) поступает на детектор 2, первый и второй синхронные детекторы 3 и 4 и на блок 5. В выражении (1) приняты следующие обозначения: U — вмплиту,па несущей частоты на выходе устрой. ства, ы, — несущая частота (круговая); mn и ш„ — коэффициенты модуляции соответственно верхней и нижней боковых полос (обычно m = ш„);

-55 а Л и п Л. „— полосы низкочастотных модулирующих частот, соответственно верхней и нижней боковых полос (обычно 4 .п А - ц ) °

Блок 5 из суммарного принятого колебания (1) выделяет первое слагае-;. мое и на основе его регенерирует напряжение вида

Н = U cos(м, +М)t (2) где Ч вЂ” некоторый фазовый сдвиг. Это колебание поступает на вход фазового расщепителя 9 и на его синфазном и квадратурном выходах получим напряжения

Va = UaCOSS1,t1 (3) и U ssinn Ät которые поступают на.первый и второй синхронные детекторы 3 и 4.

На выходе первого синхронного детектора 3 получим

U = — UUcosaët+ — VU x ш шм

2 ь 4 х cosn „t . (4) На выходе второго синхронного детектора 4 имеем

= -- V u sinn t + -> u U x шв ш

4 1 2 4 х sinn Л.„t. (5)

Далее ° напряжение (5) подается на фазовращатель 10 на 90, выходное напрякение которого можно записать в виде

V„ — - U U соььй t ЧЗ,U х

lB Ш к соsал-„ t (6) Напряжения (4) и (6) подаются на входы вычитателя 12 и сумматора 11.

Напряжение на выходе сумивтора 11 можно записать в виде

U, U + U = - U U cosa@ t (7) ш и ъ 10 2 1 1 4 а нв выходе вычитвтеля 12 е

U U U U U4cosЛЗС ш и 3 to 2 У а

Как видно из выражения (7) и (8), на выходе сумматора 11 блока 1 мы получаем только верхнюю боковую полосу принимаемого сигнала, а на выходе вычитателя 12 блока р только нижнюю боковую полосу принимаемого сигнала.

Таким образом, если помехой поражена верхняя боковая полоса принимаемого сигнала, блоком 7 на выход устройства через коимутвтор 8 коммутируется напряжение сигнала нижней боковой полосы. Если поражена нижняя боковая полоса, то коммутируется нап

5 1 ряжение сигнала верхней боковой полосы. В случае, если помеха отсутствует, то на выход устройства через коммутатор 8 подается суммарный сигнал обеих боковых полос, получаемый на выходе детектора 2.

Для выбора полосы напряжения с выхода детектора 2, сумматора 11 и вычитателя 12 подаются на детекторы

13, 14 и 15, где выделяется огибающая двухполосного сигнала и огибающие сигналов верхней, нижней полос.

Напряжения с выходов детекторов 13, 14 и 15 подаются на входы элементов

19 и 20, на выходе которых получаем "0" или "1" в зависимости от наличия или отсутствия помех.

Если сосредоточенная помеха отсутствует, то напряжения на выходах всех детекторов 13, 14 и 15 одинаковы и эти одинаковые по уровню напряжения подаются на инвертирующие и неинвертирующие входы элементов

19 и 20. В этом случае напряжение на выходах элементов 19 и 20 равно напряжению на неинвертирующем входе за вычетом напряжения на инвертирующем входе, В рассматриваемом случае, при одинаковых входных напряжениях на выходах элементов 19 и 20 получаем нули, которые инверторами 2 1 и 22 инвертируются в единицы, подаются на входы элемента И 16 и образуют единицу на его выходе, которая замыкает ключ 23 и напряжение сигнала с первого входа коммутатора

8 подается через сумматор 26 на выход устройства.

Если сосредоточенная помеха имеется на выходе сумматора 11, то она

l образует на выходе элемента 19 единицу, которая способствует образованию единицы на выходе элемента И

17. Единичное напряжение с выхода элемента И 17 подается на ключ 24, который коммутирует напряжение с выхода вычитателя 12, через ключ

24, сумматор 26 на выход устройства.,Если сосредоточенная помеха имеется на выходе вычитателя 12, то она образует единицу на выходе элемента сравнения 20 и соответственно единицу на выходе элемента И 18, которая с помощью ключа 25 коммутирует напряжение с выхода сумматора 11 через сумматор 26 на выход устройства.

525862 6

Формула изобретения

1. Устройство детектирования амп5 литудно-модулированных сигналов

У с оде ржаще е бл ок де те к тиров ания сиг-! нала верхней боковой полосы блок

t ,детектирования сигнала нижней боковой полосы и блок регенерации несущей, входы которых являются входом устройства, блок выбора полосы, первый и второй входы которого соединены с выходами блоков детектирования сигналов верхней и нижней боковых полос соответственно, коммутатор, управлякиций вход которого соединен с выходом блока выбора полосы, выход является выходом устройства, а первый и второй входы соединены с вы20 ходами блоков детектирования сигналов верхней и нижней боковых полос соответственно, блоки детектирования сигналов нижней и верхней боковых полос содержат первый и второй

25 синхронные детекторы соответственно, о т л и ч а ю щ е е с я тем, что, с целью повьппения помехоэащищенности по отношению к узкополосньпч помехам, в него введены первый амплитудный детектор, вход которого соединен с входом устройства, а выход - с третьими входами коммутатора и блока выбора полосы, фазовый расщепитель, первый и второй выходы которого соеди35 нены с опорными входами первого и второго синхронных детекторов соответственно, а вход соединен с выходом блока регенерации несущей, блок детектирования сигнала верхней боковой полосы содержит сумматор, первый вход которого соединен с выходом первого синхронного детектора, а выход является выходом блока детектирования сигнала верхней боковой полосы, блок детектирования сигнала нижней боковой полосы содеркит соединенные последовательно фаэовращатель на о

90, вход которого соединен с выходом второго синхронного детектора, а вы50 ход — с вторым входом сумматора, и вычитатель, другой вход которого соединен с выходом первого синхронного детектора, а выход является выходом блока детектирования сигнала нижней боковой полосы, сигнальные входы первого и второго синхронных детекторов являются входами блоков детектирования сигналов верхней и нижней боковых полос соответственно, .1525862

Фи, Е

Составитель Н.Мельников

Техред M.Õîäàíè÷ . Корректор С.Шекмар

Редактор В.Ковтун

Заказ 7241/53

Тираж 884

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óêroðîä, ул. Гагарина, 101

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок выбора полосы содержит второй, третий и четвертый амплитудные детекторы, входы которых являются первым, вторым и третьим входами блока выбора полосы соответственно, первьй, второй и третий элементы И, выходы которых являются первым, вторым и тре- 10 тьим выходами блока выбора полосы соответственно, соединенные последовательно первый элемент сравнения, первый и второй входы которого соединены с выходами второго и третьего 15 амплитудных детекторов соответственно, а выход — с первым входом второго элемента И, и первый инвертор, выход которого соединен с первыми входами первого и третьего элементов И, соединенные последовательно второй элемент сравнения, первый и второй входы которого соединены с выходами второго и четвертого ам36титудных детекторов, а выход - с вторым входом третьего элемента И, и второй инвертор, выход которого соединен с вторыми входами первого и второго элементов И.