Схема контроля на четность и @ л-типа

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике, предназначено для построения систем сбора и обработки информации в больших интегральных схемах на основе инжекционной логики. Целью изобретения является увеличение быстродействия. Схема контроля на четность И<SP POS="POST">2</SP>Л-типа содержит двенадцать многоколлекторных и двенадцать одноколлекторных транзисторов типа п-р-п и многоколлекторный инжектирующий транзистор типа р-п-р. Введение одноколлекторных транзисторов типа п-р-п, выполняющих функцию пороговых элементов и инверторов, позволило реализовать новую форму представления логической функции контроля на четность, приведенную в описании изобретения. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU 152590 д11 4 Н 03 К 19/091

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4434536/24-21 (22) 31.05.88 (46) 30.11.89. Бюл. N 44 (71) Таганрогский радиотехнический институт им. В.П.Калмыкова (72) Ю.И.Рогозов, Н.И.Чернов, А.Г.Оробенко и С.П.Тяжкун (53) 621.374 (088.8) (56) шагурин И.И, и др. Руководство по схемотехническому проектированию цифровых БИС и сверх-БИС на базе интегральной инжекционной логики:

Отчет по НИР, инв. М 6801544, номер гос. регистрации 75026815, М., 1979, с. 66, рис.42.

Авторское свидетельство СССР

1269253, кл. H 03 K 19/091, 1985. (54) СХЕМА КОНТРОЛЯ НА ЧЕТНОСТЬ И2ЛТИПА

Изобретение относится к импульсной технике, предназначено для построения систем сбора и обработки информации в БИС на основе инжекционной логики.

Целью изобретения является увеличение быстродействия схемы контроля на четность И2Л-типа.

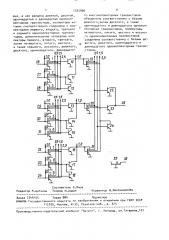

На чертеже гредставлена схема н контроля на четность И2Л-типа.

Схема контроля на четность И2Лтипа содержит девять многоколлекторных транзисторов 1 - 9 типа п-р-п, девять одноколлекторных транзисторов

10-18 типа п-р-п, десятый, одиннадцатый и двенадцатый многоколлекторные транзисторы 19,20,21 типа п-р-п, десятый, одиннадцатый и двенадцатый одноколлекторные транзисторы 22, 23, (57) Изобретение относится к импульсной технике, предназначено для построения систем сбора и обработки информации в больших интегральных схемах на основе инжекционной логики.

Целью изобретения является увеличение быстродействия. Схема контроля на четность И2Л-типа содержит двенадцать многоколлекторных и двенадцать одноколлекторных транзисторов типа п-р-и и многоколлекторный инжектирующий транзистор типа р-и-р. Введение одноколлекторных транзисторов типа п-р-п, выполняющих функцию пороговых элементов и инверторов, позволило реализовать новую форму представления логической функции контроля на четность, приведенную в описании изобретения.

1 ил.

24 типа п-р-п, многоколлекторный инжектирующий транзистор 25 типа р-п-р, певять вхолов 26-34 соединены соответственно с базами и первыми коллекторными транзисторов 1-9, вторые коллекторы транзисторов 1-3 соединены с базой транзистора 10, коллектор которого соединен с базой и первым коллектором транзистора 19, а также коллектором транзистора 11, база последнего соединена с четвертыми коллекторами транзисторов 1-9 и коллектором транзистора 12, база которого соединена с третьими коллекторами транзисторов

1-3, вторые коллекторы транзисторов

4-5 соединены с базой транзистора 13, коллектор последнего соединен с базой и первым коллектором транзистора 20, 1525906

5 !

О !

Г = Р, (F,+! +Г 1) Р (Г<+F +F, 2) Р (F, +F +F, 3), где F, =P (А,+Л,+Аз 1) P (А,+A +A) 2) Р„(А, +Лг+Лз 3) 1

& г =Р7 (Л4+Л +Л ь 1 ) Р8 (A +A +Ль 2 )

; - „(,, ) „(. . — ) Г, 1 а та кже коллектором транзистора 14, база которого соединена с четвертыми коллекторами транзисторов 4-6 и коллектором транзистора 15, база последнего соединена с третьими l

7-9, вторые коллекторы транзисторов

19-21 объединены с базой транзистора где + - арифметическая операция суммирования; операция сравнения;

А, -А — сигналы на входах 26-33;

— сигнал на входе 34.

В этом соотношении P<,Р, Р, Р,опороговые функции арифметической суммы аргументов A; no порогу единицы;

Р,Р,Р,P,(— пороговые функции арифметической суммы аргументов А; по поРогУ два; Рз,Рs Р,Ргг пороговые функции арифметической суммы аргументов А по порогу три.

В инжекционной логике в качестве элементов, выполняющих арифметическую операцию суммирования, используются токовые повторители (транзисторы 1-9, 19-21 в предлагаемой схеме). В качестве пороговых элементов используются 4> инверторы (в рассматриваемой схеме функцию пороговых элементов выполняют транзисторы 10-18, 22-24). Весовые коэффициенты или требуемое соотношение между входными точками транзисторов задается путем изменения геомет50 рических размеров между базовыми Pобластями и-р-п транзисторов и эмиттерными P-областями инжектирующего транзистора. В предлагаемой схеме, чтобы не загромождать чертеж и облег- 5 чить понимание принципа работы схемы, связь между коллекторами инжектирующего транзистора 25 с элементами схе22, коллектор которого соединен с выходом 35 и коллектором транзистора 12, база которого объединена с четвертыми коллекторами транзисторов 19-21, а также коллектором транзистора 24, база которого соединена с третьими коллекторами транзисторов 19-21, эмиттеры транзисторов 1-24 соединены с шиной нулевого потенциала и базой транзистора 25, эмиттер которого соединен с шиной питания 36, а коллекторы соединены соответственно с базами транзисторов 1-24.

Устройство реализовано в гибридном (арифметико-логическом) базисе, для которого выходная функция F определена следующим образом: мы показана условно стрелками с указанием значения тока, инжектируемого в данный транзистор, согласно выражению (1). Транзисторы 9-12 совмещают в себе две функции: выполняют операцию сравнения с порогом 3 единицы и функцию инверсии, в базах укаэанных транзисторов реализуются соответственно функции Р, Р Р, Р ) Рц, Р, Р, Рз, Рг Р

Схема контроля на четность реализует функцию четности в зависимости от значения контрольного разряда следующим образом: При B=I F I при четном числе "1"; .F=O при нечетном числе

"1". При В=О реализуется функция нечетности 1 =1 при нечетном числе "1".

В дальнейшем будем рассматривать принцип работы схемы при В=I.

Предположим, что на входы 26-33 устройства подается следующая комбинация входных сигналов (нечетное число единиц):

A =A а=1, А =0, А =А =Аб=1, A, — Ав — О.

В этом случае коллекторные токи транзисторов 1,2,4,5,6,9 равны входHblM токам (единице), так как токовые повторители имеют коэффициенты передачи, равные единице по всем коллекторам, а транзисторы 3,7,8 закрыты, так как их входные токи открываются

Формула

15 входными шинами. Следовательно, коллекторами транзисторов 1-9 с баз пороговых транзисторов 10,11,12 отбираются два дискрета тока, с баз транзисторов 13,14,15 - три дискрета тока, а с баз транзисторов 16,17,18 один дискрет тока (транзистором 9).

Поэтому транзисторы 10, 12 закрыты, транзистор 11 насыщен, т.е. на выходе транзистора 19 формируется сигнал нулевого уровня, который закрывает транзистор 19. Транзисторы 13,14,15 закрыты, поэтому токовый повторитель

20 открыт (на его входе формируется сигнал высокого логического уровня).

Транзистор 16 закрыт, транзистор 18 открыт, т.е. с его базы отбирается лишь один дискрет тока. Открытый транзистор 18 отбирает оставшиеся

1,5 дискрета тока (один дискрет тока с базы транзистора 17 отбирает транзистор 9) с базы транзистора 17, поэтому он закрыт, следовательно, на базе транзистора 21 формируется сиг нал высокого логического уровня, а транзистор 21 открыт. Так как транзистор 19 закрыт, а транзисторы 20, 21 открыты, то с баз транзисторов 22, 23, 24 отбираются транзисторами 20 и 21 два дискрета тока. В результате этого транзисторы 22 и 24 закрыты, т.к. токи, инжектируемые в их базы, меньше токов, отЬираемых транзисторами 20, 21. Транзистор 23 открыт, что приводит к формированию на выходе 35 нулевого логического уровня Г=О.

Если на входы 26-31 устройства подается четное число единиц, напри=А =А =Я =А,=А =О; Ат=Ав 1, то при такой комбинации транзистор 10 открыт, транзистор 12 открыт, последний своим коллектором закрывает транзистор 11, поэтому на входе транзистора 19 формируется низкий логический уровень. Транзистор 13 открыт, поэтому транзистор 20 закрывается. Так как с баз транзисторов 16,17,18 отбираются открытыми транзисторами 7,8,9 три дискрета тока, то транзисторы 16,17, 18 закрыты, а на входе транзистора 21 имеется высокий логический уровень.

Следовательно, транзисторы 19, 20 за" закрыты, а транзистор 21 отбирает с баз транзисторов 22,23,24 по одному дискрету тока. Поэтому транзистор 22 закрывается, транзистор 24 насыщен и своим коллектором закрывает транзистор 23. На выходе 35 устройства бу2590ь

6 дет сформирован сигнал высокого логического уровня Г=1.

Таким образом, предлагаемое уст5 ройство реализует требуемую функцию контроля на четность.

Реализация нового представления логической функции контроля на четность путем введения четырех одноколлекторных транзисторов и организации новых связей позволило не менее чем в 1,5 раза увеличить быстродействие схемы за счет использования только транзисторов п-р-п. изоЬретения

Схема контроля на четность И Лтипа, содержащая двенадцать многокол20 лекторных, восемь одноколлектЬрных транзисторов типа и-р-п и многоколлекторный инжектирующий транзистор типа р-п-р, эмиттер которого соединен с шиной питания, а коллекторы и ба25 за — соответственно с базами и эмиттерами многоколлекторных и одноколлекторных транзисторов и общей шиной, базы и первые коллекторы девяти многоколлекторных транзисторов соединены

30 с соответствующими девятью входами, вторые коллекторы первого, второго, третьего, затеи четвертого, пятого, шестого, а также седьмого, восьмого, девятого многоколлекторных транзисто35 ров соединенысоотве1ственнос базами первого, затем второго, а также третьего одноколлекторных транзисторов, третьи коллекторы первого, второго, третьего, затем четвертого, пятого, 40 шестого, а также седьмого, восьмого, девятого многоколлекторных транзисто" ров соединены соответственно с базами четвертого, затем пятого, а также шестого одноколлекторных транзисторов, 4 вторые и соответственно третьи коллекторы десятого, одиннадцатого и двенадцатого многоколлекторных транзисторов соединены с базами седьмого и соответственно восьмого одноколлекторных транзисторов, коллекторы первого, второго и третьего одноколлекторных транзисторов соответственно соединены с базами и первыми коллекторами десятого, одиннадцатого и двенадцатого многоколлекторных транзисторов, коллектор седьмого одноколлекторного транзистора соединен с выходом, отличающаяся тем, что, с целью увеличения быстродейст1525906

О,5 7,5

Составитель А. Янов

Редактор М.Циткина Техред М.Дидык Корректор М.Максимишинец

Заказ 7244/55 Тираж 884 Подписное

8НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ C(;CP

113035, Москва, И-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина,101 вия, в нее введены девятый, десятый, одиннадцатый и двенадцатый одноколлекторные транзисторы, коллекторы которых соответственно соединены с кол5 лекторами первого, второго, третьего и седьмого одноколлекторных транзисторов, дополнительные четвертые коллекторы первого, второго, третьего, затем четвертого, пятого, шестого, а также седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцато051,5 го многоколлекторных транзисторов объединены соответственно с базами девятого, затем десятого, а также одиннадцатого и двенадцатого одноколлекторных транзисторов, коллекторы четвертого, пятого, шестого и восьмого одноколлекторных транзисторов соединены соответственно с базами девятого, десятого, одиннадцатого и двенадцатого одноколлекторных транзисторов.