Устройство для вычисления сумм произведений

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для построения специализированных вычислительных средств. Цель изобретения - сокращение аппаратных затрат. Для достижения поставленной цели устройство содержит соединенные последовательно блоки вычисления итераций и вычисления коррекций. Уменьшение аппаратных затрат достигается за счет многосекционного построения блока вычисления коррекции, осуществляющего итерационную операцию деления путем последовательных приближений. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (д11 4 С 06 F 7/49

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ПСНТ СССР (21) 4353253/24-24 (22) 30, 11. 87 (46) 07,12,89, Бюл. И 45 (71) Киевский институт инженеров гражданской авиации им. 60-летия

СССР (72) Л,Я. Нагорный, И,А. Жуков, Д. Сингх и И.К, Жига (53) 681.3(088,8) (56) Andreus М. et al. А pipelined

computer architecture for unified

elementary function evalnation computer.-Elect. Eng., 1978, ч. 5, р. 194.

Авторское свидетельство СССР

Ф 1432512, кл, G 06 F 7/49, 06.04.87.

Изобретение относится к вычисли" тельной технике и предназначено для построения специализированных вычислительных с редс тв .

Цель изобретения — уменьшение аппаратных затрат.

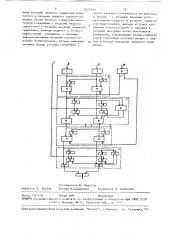

На чертеже представлена структур ная схема устройства, Устройство содержит первый 1 и второй 2 регистры, блоки вычисления итераций 3 и коррекций 4, сумматорнакопитель 5, блок 6 постоянной памяти, общую шину 7, входы множимого 8 и множителя 9, входы 10 значений угла поворота. Число блоков 3 и 4 определяется необходимым числом итераций для получения заданной точности вычислений °

„„SU„„1527629 А 1

2 (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУИ11

ПРОИЗВЕДЕНИЙ (57) Изобретение относится к вычислительной технике и предназначено для построения специализированных вычислительных средств, Цель изобретения — сокращение аппаратных затрат.

Для достижения поставленной цели устройство содержит соединенные последовательно блоки вычисления итераций и вычисления коррекций. Уменьшение аппаратных затрат достигается эа счет многосекционного построения блока вычисления коррекции, осуществляющего итерационную операцию деления путем последовательных приближений.

1 ил.

Блок вычисления итераций содержит сумматоры-вычитатели 11 и 12 и сдвигатели 13 и 14, Блок вычисления коррекции содержит сумматоры-вычитатели 15 и 16, сдвигатели 17 и 18, коммутаторы 19 и

20 и элемент 21 сравнения, Устройство работает следующим образом, В регистры 1 и 2 заносятся числа, соответствующие модулям перемножаемых векторов.

Операция осуществляется в соответствии с алгоритмом Волдера.

Для умножения вектора с координатами (а,, Ь,) на вектор с координатами (а, b ) в начале определяется

1527629 угол 0 =arctg(a вектора х=(а,, Ь ).

Значения тангенса угла поворота вычисляются заранее и подаются на вход блока 6 постоянной памяти. В регистры 1 и 2 записываются значения модулей (длин) векторов х и у, При этом каждый блок вычисления итераций осуществляет над входными данными операцию

< — I х, =х, -Я; у, 2 у, =у +с,x; 2 где E, - . 1, à i=O, 1..., и-1 — номер блока, соответствующий номеру итерации.

Коэффициенты, являются значениями функции, указывающей угол поворота вектора, вычисляются заранее и хранятся н блоке 6 постоянной памяти, 0

Блоки 4 вычисления коррекций осуществляют коррекцию изменения длины вектора результата, происходящую при вычислении согласно укаэанному итерационному алгоритму, Блоки вычисления 25 коррекций осуществляют операцию деления в итерационной форме.

Каждый блок 4 выполи> ет операцию

I I > х, +, х;-G;x 2

30 где х,и у, — значения данных на входе блока

0 при х с у;, ! >з !

1 при х)у., На первые входы сумматоров-вычитателей 11 и 12 поступают коды чисел из

35 регистров 1 и 2, а на вторые входы сумматоров-вычитателей через сдвигатели 14 и 13 — коды чисел с выходов регистров i и 2, сдвинутые на один разряд вправо, Нас тройка сумматоров-в ычита теле и

11, 1 2 на проведение операций суммирования или вычитания осуществляется сигналами с выхода блока 6 пос- 45 тоянной памяти ° Значение управляющего сигнала определяется кодом значения угла поворота, поступающим на адресные вх цы блока 6 по шине 10, Остальные блоки вычисЛения итераций функционируют аналогично, В каждом блоке вычи<. леиия итераций 3 осущест— вляется в соотве1ствии с принеденным алгори тмс>м одна и гера ция поворот» вектора. бранные с выходов сумматоров55 вычитателей 11 и 12 поступают н1 вь1 ходы блока 3 и на входы перво1 о блока 4 коррекции, в котором нроиэнод11тся анулирова ние деф< рм 31 осуществляющих сдвиг на один разряд влево (умножение на 2 ). На первые входы коммутаторов 19 и 20 поступают величины х 2 и у 2, на вторые входынулевой потенциал с шины 7. Управление коммутаторами 19 и 20 осуществляется по значению сигнала G=O или

1 на выходе блока 21 сравнения, выр»батываемого при сравнении величин

< < х, и у.

I 1

Результаты с выхода последнего блока вычисления Коррекций суммируются в сумматоре-накопителе 5.

Формула изобретения

Устройство для вычисления сумм произв еде ний, содержащее сумматорнакопитель, блоки вычисления итераций, блоки вычислений коррекций, блок постоянной памяти, первый и второй регистры, информационные входы которых соединены соответственно с входами множимого и множителя устройства> выходы регистров соединены с соответствующими входами первого блока вычисления итераций, выходы к»ждого блока вычисления итераций соединены с входами соответствующего блока вычисления коррекций, выходы последнего блока вычисления коррекций соединены с входами сумматора-накопителя, выходы каждого блока вычисления коррекций соединены с входами последующего блока вычисления итераций, управляющие входы которых соединены с выходами блока постоянной памяти, входы которого соединены с входами значений угла поворота устройства, каждый блок вычисления коррекций содержит первый и второй сумматоры-вычитатели, первые входы которых соединены с соответствующими выходами соответствующего блока вычисления итераций, о т л и ч а ю щ е е с я тем, что, с целью уменьшения аппаратных затрат, каждый блок вычис ения коррекций содержит первый и в<орой сдвигатели, первый и второй к<ммутаторы, элемент сравнения, перВ11Е НХОЛЫ КитОРОГО СОЕДИНЕНЫ С Г<ЕРСоставитель Ю, Фирстов

Техред Л.Сердюкова Корректор О. Кравцова

Редактор И. Дербак

3 ах аз 7 5! 1/ 53 Тираж ЬЬВ Подписное

ВНИИПИ Государственного комитета по иэобретениям и открытиям при ГКНТ СССР

11ЗП3 5, Москва, Ж-35, Раушская наб., д. ч /

Проиэводственно-издате: ьский комбинат "Патент", г.ужгоро,<, ул. Гагарина,101

5 15276 выми входами первого сумматора-вычитателя и входами первого сдвигателя, первые входы BTQpoI сумматора-вычитателя соединены с входами второго

5 сдвигателя и вторыми входами элемента сравнения, выходы первого и второго сдвигателей соединены с первыми информационными входами соответствующих коммутаторов, вторые информа- 1ð ционные входы которых соединены с шиной нулевого потенциала устройства, а выходы — с вторыми входами сооТ в етс твенпо ii ер но го и второго с умматоров-вычитателей, выходы которых соединены соответственно с первыми и вторыми выходами блока вычисления коррекций, управляющие входы коммутаторов соединены соответственно с первым и втс рым pûõîäàìè элемента сравнения °