Комбинационный сумматор

Иллюстрации

Показать всеРеферат

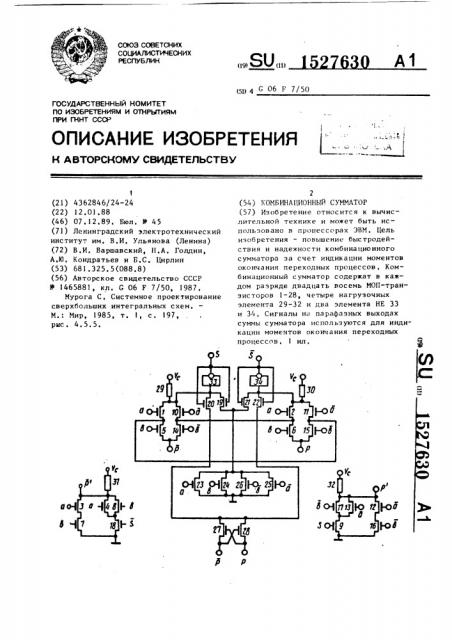

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения - повышение быстродействия и надежности комбинационного сумматора за счет индикации моментов окончания переходных процессов. Комбинационный сумматор содержит в каждом разряде двадцать восемь МОП-транзисторов 1 - 28, четыре нагрузочных элемента 29 - 32 и два элемента НЕ 33, 34. Сигналы на парафазных выходах суммы сумматора используются для индикации моментов окончания переходных процессов. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (!1) (51) 4 G 06 F 7/50

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ П.(НТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4362846/24-24 (22) 12.01,88 (46) 07.12.89. Бюл. В 45 (71) Ленинградский электротехнический институт им. В,И. Ульянова (Ленина) (72) В,И. Варшавский, Н.А, Голдин, А.Ю, Кондратьев и Б.С. Цирлин (53) 681 325,5(088,8) (56) Авторское свидетельство СССР

В 1465881, кл. G 06 F 7/50, 1987.

Мурога С ° Системное проектирование сверхбольших интегральных схем.

M. Мир, 1985, т. 1, с, 197, рис. 4.5.5.

2 (54) КОМБИНАЦИОННЬ1Й СУММАТОР (57) Изобретение относитс я к вычислительной технике и может быть ис— пользонано в процессорах ЭВМ. Цель изобретения — повышение быстродейстния и надежности комбинационного сумматора за счет индикации моментов окончания переходных процессов. Комбинационный сумматор содержат в каждом ра з ряде дн адца ть нос емь МОИ-транзисторон l 28, четыре нагрузочных элемента 29-32 и дна элемента НЕ 33 и 34. Сигналы на парафазных выходах суммы сумматора используются для индикации момечтон окончания переходных процессов. 1 ил, ОПИСАНИЕ ИЗОБРЕТЕНИЯ с

H()» состояние

11 )р т" HHe "T»<)CHTC?I к 13t,iaHcJIHT<3J1hH()p Т(XH?tti H )ж(T быТь HC11()JIb э овл н(7 в процес со рах цифровых ЭВ)1. !

,åJtl- и. n<)() -,гн «Я вЂ” .Ii)?«k,tttteHHC ()»tc Tроде".с с) ия lt »лцеж»с)с TH комбиилциои—

»Ого с, мм" тора )л сечет индикации M<) ме»тов окоичл?«??я иереx(., ных процес— ! Ов

1!л чертежг прелсталлс»л схема одIt(гI) р-.. ряда комбинационного суммаТОР 3.

Клжд . и рл эрс«д комб«гилц?<Ои?«ого с умм.-<т ра с пеp:«(ttò (1(3(1-транзисторы 1-28, HJI руэс ч!И«е э.<ементы 29-3.", элементы

НЕ >З вЂ” 34, входы;«р «мь«х и инверсных эилче»с>й иеp?«cl л „л и нто«-Огo Ь, c ","1 I лем>.- и переноса иэ иредыдуще. О рл Jp? J(à р... выхо;1«н прямых и инверс— иых знлчен« с, ?мы да»ного разряда з, †..:. 1;ереиосл в.следующий разряд ! --!

Р l t)

,уммл7 )р pаботлет следующим обик< 7(е .->ломе««тл НЕ 34 сохраняется эна1 I !1 чеи?«с О до тех 11(>pl пока все входы с умь.л то рл ие возв рлщлк>тс я в инертное со(тояиие.

I .ñc.ïH иа входы рл .ряда сумматора

»сд!«ется рабочий набор сигналов, в к )тором значение "1" появляется на одн>м прямом и двух инверсных входах (Например, а=Ь=р=1 и а=Ь=р=О), то на

1«кодс элемента НЕ 33 устанавливается эил<«е««ие 0", а на его 1311«ходе я — значение 1, 13 результате чего от bl влются транзисторы 19, 20 и 9 и на ! вь ходе р уcтанлвливае Iся значение

"О", Тлк как один иэ транзисторов 27 и "8 открыт и два из транзисторов

23 — 2б также открызы> значение "О"

?1(1 входе элемента НЕ 33 сохраняется до тех иор, пока все входы сумматора не возвращаются в инертРЛ ЗОМ, В интервапь« времени между двумя при ко r()pо.i иа входы каждогс разряда ио -,:! < (. p след, - <,ля комбинл i,ия вход-иых сi:.гна 1>г.; л=л=Ь=Ь=0, p=p= l . IIpH

: гс.м трли.«1«стерн; « -26 закрыты и нл

Ell.TX ПЛ",: !((73Ы; -.I ) >«аВЛИ?«;«Ю7 С Я ИУ??с—

?3btt= эил пс ния 5 s=O, а нл <зь ходах перси !сл — -.дин«ч»ые р =р

/ — /

ЕОНH I:i нх ды р73рягл сумматора подл ется ед 1»ичный раб очии набор сигиэлоп а=Ъ=р=-(и а=Ь=р=О, то транэ и<-7!>(>ь« 1-8 открьв аютс н и ил вьгходе р и нк —.де леме rта НЕ 33 у(TaHHEIJ и— в;<ет< «аче .«.". 11<. .1 синие,«л, cooTEJBT— ! -,1!

СТВу (>1?1«РС .Г!ОГИЧСС/(ОМу V а Нс« ВЬ«ХО

11! l1 це s 3!«ля ение . НГ>и эт(>м от кр.-,«в-«1 .сн ?рлнэис торы 19 и 20. и, П.) С" ) "TEK > 7 (!с! 1«ЭИ ТО(71 | — 3, 24 И

2" тл<-.же . гк()ьi. I, »,1 вход- 3>ti мента 1!ll

НЕ 33 с< X;>. †;.Няет(?я значение u до

ТЕ): ПО P T.<) I<;I Е«Г сР В " .С)ДЫ (>MMO Ã(7(;а 1<1

РОЗ .1 (. !1, Щ!Ло>ТС В HHI! (>ТИОС . С ()C ТО Н k«HE .

Еcit;T

»1: х ды (. . «,)я, 7 суммлтn(!л иул н!!и рлбоч t;1 набор сигb=p= 0 и а=-Ь=(7= 1, ro > тк pi tâ р.<иэи. о,>ы 1 . — 1(и HI! выход, Jtt It(. l« л НЕ 3<7 ?????????????? l (.>«

1I . 11 д, а нл вых . д е s — 3 Hлч <..—

IIpH этс м открывлн тся I рлн2! и 22 и поскольку траиэи<—

2б !! 28 1 «кже >гк()ы111 Hä

1<ОДЛ Е f C Я

»алов а=ваютсл ! р и вх<. 3 И Л Ч (i H H i ние 1 зис торы торы 25, T t(7cJi(до нательными с умм««ров; ниями с умМс17 ОP !Ji«);ÎÄÈ I C Ч В ИНЕ с) I НОМ СОСТОЯНИИ, Если нл входы разряда сумматора подается рабочий набор сигналов, в к(>тором значение "1" появляется на двух прямых и одном инверсном входе (например, л=Ь р=1 и а=Ь=р=О), то на входе элемента НЕ 34 появляется зна30

1 l I l чение О, а на его выходе s — значение "1", в результате чего открываются транзисторы 21, ?2 и 18 и на ! вь1ходе р устаиавливается значение

"0" Тлк как один из транзисторов 27 и 28 открыт и два из транзисторов 2326 -.лкже открыты, значение "О" на входе элемента НЕ 34 сохраняется до тех пор, пока все входы сумматора не воэврэн,лются в инертное состояние.

40 !

Таким образом, рабочее состояние в>,ходов s H в каждого разряда сумматора устанавливается только после то4 г<, клк все его входы гереходят из

1«и<"ртного состояния в рабочее. При . том рабочее сoc тояние выходов пере(— / ио. л в следующий разряд р и р провернется в следующем разряде. Переход

50 пыхс )ов s H s кажлого разряда из рабочего со..тояния в инертное Нрс>Нсхо дит после того, как на всех его входах устанав пиваетс я инертное состояние. !Iоэтому в предлагаемом сумматоре и»дикация моментов окончания переход)J иых процессов ос ущес твляетс я по с0стoi«t«1«þ прямых и инверсных выходов

<; ммы всех разрндов и переноса из старшего рс«эряда

5 ! 527б и э о б р е т е н и я

Ф < р м у л

Комбинационный сумматор, соде ржащий н каждом разряде восемнадцать

M0I!-транзисторов и четыре на груз оч5 ных элемента, причем затворы первого, второго, третьего и четвертого транзисторов объединены и подключены к прямому входу первого слагаемого данного разряда сумматора, а затворы пятого, шестого, седьмого и восьмого транзисторов — к прямому входу второго слагаемого данного разряда сумматора, затвор девятого транзистора l5 соединен с прямым выходом суммы данного разряда сумматора,: затворы десятого, одиннадцатого, двенадцатого и тринадцатого транзисторов объеди— иены и подключены к инверсному вхо- 20 ду первого слагаемого данного разряда сумматора, а затворы четырнадцатого, пятнадцатого, шестнадцатого и семнадцатого транзисторов — к инверсному входу второго слагаемого 25 данного разряда сумматора, затвор восемнадцатого транэис тора со единен с инверсным выходом суммы данно—

ro разряда сумматора, первый вывод первого нагруэочного элемента сое- Зо динен с истоками первого и десятого транзисторов, первый вывод второго нагрузочного элемента соединен с истоками второго и одиннадцатого транзисторов, первый вывод третьего нагруэочного элемента соединен с истоками третьего, четвертого, восьмого транзисторов и с инверсным выходом переноса в следующий разряд сумматора, первый вывод четвертого нагруэочного элемента соединен с истоками двенадцатого, тринадцатого, семнадцатого транзисторов и с прямым выходом переноса в следующий разряд сумматора, стоки первого и одиннадцато- 45 го транзисторов соединены между собой

v с истоками пятого и пятнадцатого транзисторов, стоки второго и десятого транзисторов соединены между собой и с истоками шестого и четырнадцатого транзисторов, сток третьего транзистора соединен с истоком седьмого

35 мого транзистора соединен с истоком двадцать восьмого транзистора и с прямым входом переноса из предьщущего разряда с умматора, затвор двадцать восьмого транзистора соединен с истоком двадцать седьмого транзистора и с инверсным входом переноса из предыдущего разряда сумматора, транзистора, исток восемнадцатого транзистора соединен со стоками четвертого и вос ьмого транзисторов, сток двенадцатого транзистора соединен с истоком шестнадцатого транзистора, исток девятого транзистора соединен со стоками тринадцаг; го и семнадца30 того тpclH истор в, стоки IIRToI и четырныдцат го трын гисторон объедииены и полк JIH ч Hbl к иннерсн му входу переноса из предыдущего разряды сум1 ма rupa, а стоки шестс го и пятнадцатого трынзисторон — к прямому входу переноса из предыдущего разряда сумматора, стоки седьмого, девятого, шестнадцатого и восемнадцатого тран—

"исторов объединены и подключены к обще и шине сумматора, шина питания которого подключена к вторым выводам всех нагрузочных элементов, о т л и ч а ю шийся тем, что, с целью повышения быстродействия и надежности комбинационного сумматора эа сче г индик ации моментов окончания переходных процессов, в каждый ра э ряд сумматора введены два элемента llr и десять МОПтрзнзисторов, причем исток первого транзистора соединен с истоками девя Tíïäöàтого, двапца Toго транзисторoB и с входом первого элемента НЕ, выход которого соединен с прямым выхо— дом суммы данного разряда сумматора и с затворами девятнадцатого и двадцатого транзисторов, исток второго транзистора соединен с истоками двадцать первого и двадцать второго транзисторов и с входом второго элемента

HL, выход которого соединен с инверсным выходом суммы данного разряда сумматора и с затворами двадцать первого и двадцать второго транзисторов, стоки девятнадцатого и двадцать первого транзисторов соединены между собой и с истоками двадцать третьего, двадцать четвертого, двадцать пятого и двадцать шестого транзисторов, стоки которых объединены и подключены к общей шине сумматора, а их затворы соединены и подключены соответственно к прямым и инверсным пходам пер-. вого и второго слагаемых данного разряда сумматора, стоки двадцатого и двадцать второго транзисторов соединены между собой и с истоками двадцать седьмого и двадцать восьмого транзисторов, затвор двадцать седь