Устройство для преобразования количества единиц двоичного кода в код по модулю к

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Использование его в системах передачи и обработки дискретной информации позволяет повысить надежность устройства, которое содержит блок 2 весового суммирования, сумматор 3 и пороговый блок 5. Благодаря введению многоканального преобразователя 1 параллельного кода в последовательности импульсов, сумматора 4, блока 6 формирования вычетов и запоминающего блока 7 исключается блок свертки числа разрядов прототипа и упрощается блок весового суммирования. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

14 А1 (19) (11) (1) 4 Н 03 М 7/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4363832/24-24 (22) 08. 12. 87 (46) 07.12.89. Бюл.У 45 (72) О.Н.Муэыченко (53) 681.325(088.8) (56) 1,Авторское свидетельство СССР

М 1357960, кл, G 06 F 11/10, 1983.

2. Вопросы радиоэлектроники. Сер, „

Общие вопросы радиоэлектроники, 1984, N 12, с. 120-128.

3.Авторское свидетельство СССР

1(1476614, кл. Н 03 М 7/20, 1987. (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

КОЛИЧЕСТВА ЕДИНИЦ ДВОИЧНОГО КОДА

В КОД ПО МОДУЛЮ К

2 (57) Изобретение относится к автоматике и вычислительной технике. Использование его в системах передачи и обработки дискретной информации позволяет повысить надежность устройства ко горое содержит блок 2 весового суммирования, сумматор 3 и пороговый блок 5. Благодаря введению многоканального преобразователя 1 параллельного кода в последовательности импульсов, сумматора 4, блока 6 формирования вычетов и запоминающего блока 7 исключается блок свертки числа разрядов прототипа и упрощается блок весовоro суммирования. 2 ил.

1527714

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи и обработки дискретной информации.

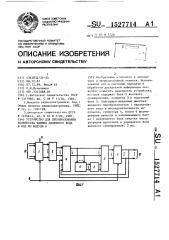

Цель изобретения — повышение надежности устройства, На фиг.! изображена блок-схема устройства; на фиг.2 — вариант вы- 1р полнения порогового блока и блока формирования вычетов для случая К = 13, Устройство содержит многоканальный преобразователь параллельного кода в последовательности импульсов, 15 блок 2 весового суммирования, первый и второй сумматоры 3 и 4, пороговый блок 5, блок 6 формирования вычетов и запоминающий блок 7. На фиг.1 обозначены информационные входы 8, так- 2р товый вход 9, информационные выходы

10 и выход 11 конца работы.

Многоканальный преобразователь 1 служит для преобразования параллельного кода на каждой из групп входов 25

8 н последовательности импульсов на соответствующем выходе и может быть выполнен, как в (1), либо в вице распределителя импульсон, выходы которого соединены с первыми входами 3р р групп элементов И (р - число каналов преобразователя 1), вторые входы элементов И каждой группы являются входами соответствующей группы преобразователя (соответствующего канала преобразователя 1), а выходы i:îåäèíåíû с нходами элемента

ИЛИ, выход которого является соответствующим выходом многоканального преобразователя (выходом соответствующего канала преобразователя 1).

Многоканальный преобразователь 1 параллельного кода в последовательности импульсов может быть выполнен в виде р регистров сдвига, соединен- 45 ных информационными входами с информационными входами преобразователя, тактовыми входами — с его тактовым входом, а выходами переноса — с выходами преобразователя (выходами каналов преобразователя), инверсные выходы каждого регистра сдвига соединены с входами своего элемента И, а выходы последних — с входами элемента И выход которого является выходом

55 останона преобразователя, входы раз-,, решения записи регистрон сдвига соединены с входом записи преобразователя °

Блок 2 весового суммирования может быть выполнен, как н !2) и

f э

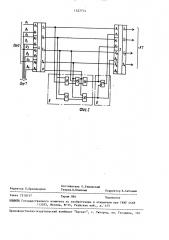

p). !!ороговый блок 5 может быть выполнен, как в (3>. В общем случае он представляет собой многопороговый элемент с весами входов 2 и порогами выходов A = К, 2К, ..., 1К, где

12 -21

1 = ----,— — —, m — разрядность сумматоров 3 и 4. Для К = 13 пороговый блок 5 выполнен на элементах

ИЛИ 12 — 14 или И 15 и 16 (фиг.2).

Блок 6 формирования вычетов н общем случае может быть выполнен в виде группы из (1-1) элементов И, причем j -й элемент И соединен прямым входом с выходом порогового блока 5 с порогом А = jK а инверсным входомс выходом блока 5 с порогом А (j + 1) К, выходы элементов И соединены с входами группы элементов

ИЛИ, i-й выход блока формирования вычета соединяется с входом i-ro раз— ряда сумматора 3. Блок 6 формирования вычетов при наличии единичных сигналов на выходах порогового блока

5 е порогами А c rK формирует на выходах двоичный код числа P

2 (1 + Sqn(r-2)) — rK. Для этого

3-и . ыход блока 5 соединяется с tm выходом многопорогового блока, если в j-м разряде двоичного представления всех чисел „при r + t имеется

О, а при r = t ..., 1 имеется единица, j-й выход блока 6 соединяется с выходом -го элемента И бпока 6, если единица имеется в 1-м разряде двоичного представления только одного числа P g -й выход блока 6 соединяется с выходом элемента ИЛИ, если единица имеется н j-м разряде. двоичных представлений чисел „ при г прм этом с нходами данногр элемента ИЛИ соединены выходы,, (z, °... (-го элементов. И блока 6, в частном случае т = (! ..., t ..., 1, с входом элемента ИЛИ соединяется непосредс:— венно выход порогового блока 5 с порогом А = t К. Для случая К = 13 блок 6 содержит элемент ЗАПРЕТ 17.

Запоминающий блок 7 служит для организации режима накопления и может быть выполнен, например, на двух реги3О

5 15277 страх памяти, причем информационные входы блока 7 соединены с информационными входами первого регистра памяти, информационные выходы которого соединены с информационными входами второго регистра памяти, выходами которого являются выходы блока 7, вход разрешения записи первого регистра памяти, являющийся тактовым входом блока, соединен с входом инвертора, выход которого соединен с входом разрешения записи второго регистра памяти. Блок 7 может быть выполнен и на одном регистре памяти, информаци-15 онные входы которого являются входами блока 7, а выходы являются выходами блока 7. Вход разрешения записи регистра через элемент задержки соединен с тактовым входом блока 7, 20 при этом вход разрешения записи регистра памяти выполнен импульсным.

Устройство работает следующим .образом.

В исходном состоянии многоканальный преобразователь 1 параллельного кода в последовательности импульсов и запоминающий блок 7 сброшены.

Входной код подан на входы 8, Если многоканальный преобразователь 1 выполнен на регистрах сдвига, то входной код записан в них.

На тактовый вход 9 устройства подаются тактовые импульсы. При этом многоканальный преобразователь

1 преобразует количество единичных

35 сигналов на информационных входах 8 i в соответствующее число импульсов на

i-м выходе (выходе i-го канала преобразователя 1). Импульсы с выходов многоканального преобразователя 1 на каждом такте (синхронно с тактовыми импульсами) поступают на входы блока

2, который формирует на своих выходах двоичный код их числа (по модулю К), поступающий на входы сумматора 4, к содержимому которого при этом прибавляется значение остатка по модулю К кода на выходах блока 2 ° Блоки 5 и 6 и сумматор 3 служат для полной свертки кода по модулю К. Работа продолжается таким образом до окончания преобразования входного кода преобразователем

1, при этом он самоблокируется и далее импульсов на своих информационных

55 выходах не формирует, на его выходе останова появляется единичный сигнал, Я

14

6 поступающий на выход 11 конца работы устройства, свидетельствуя об оконча— нин цикла работы. Результат снимается с выходов 10.

В устроистве оптимизации разрядности кода на выходах блока подсчета единиц осуществляется выбором канальнасти преобразователя параллельного кода в последовательности импульсов, что позволяет исключить полностью блок свертки числа разрядов кода и упростить блок весового суммирования, Ф о р м у л а и з о б р е т е н и я

Устройство для преобразования ко .«чества единиц двоичного кода в код по модулю К, содержащее блок весового суммирования, пороговый блок, входы которого объединены с соответствующими первыми входами первого сумматора, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, него введены второй сумматор, блок формирования вычетов, запоминающий блок и многоканальный преобразователь параллельного кода в последовательности импульсов, информационные входы которого являются одноименными входами устройства, а тактовый вход объединен с тактовым входом ззпоминающего блока и является тактовым входом устройства, информационные выходы многоканального преобразователя параллельного кода в последовательности импульсов соединены с соответствующими входами блока весового суммирования, выходы которого подключены к первым входам второго сумматора, выходы которого соединены с соответствующими входами порогового блока, выходы которого подключены к соответствующим входам блока формирования вычетов, выходы которого соецинены с соответствующими вторыми входами первого сумматора, выходы первого сумматора поцключены к информационным входам запоминающего блока, выходы которого соединены с соответствующими вторыми входами второго сумматора и являются информационными выходами устройства, выход окончания работы многоканального преобразователя параллельного кода в последовательности импульсов является выходом конца работы устройства.

1527714

Составитель О, Ревинский

Техред Л. Олийнык Корректор В.Кабаций

Редактор О.Юрковецкая

Заказ 7518/57

Тираж 884

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Om2

Е7