Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в многоканальных информационно-измерительных системах. Целью изобретения является повышение надежности устройства. Устройство для ввода информации содержит компараторы 1, мультиплексор 3, блок 4 памяти, цифроаналоговый преобразователь 6, счетчики 2 и 7, блок 5 управления, ключи первой и второй групп 8 и 9. Устройство работает в двух режимах, при которых в первом цикле устройства входная информация фиксируется в блоке 4 памяти, во втором цикле, который по длительности меньше первого цикла, происходит считывание данных из блока 4 памяти. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН дд 4 G 06 F 3/05

l

ГОСУДАРСТВЕННЫЙ НОЧИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТ!.!РЬТИЯМ

ПРИ ГННТ ССЛ влееаиааиикквииаядвиаавг юмаавпюва

{21) 4286869! о4 ?4 (22) 20.07.87 (46) 15.12.89 Бюл, ¹ 46 (71) Инстигу; кибернетики им. В. М. Глушкова АН УО(.Р (??) Я. Н. Николайчук и Б.."l. 1Певчук (53) 681.327.8 (088.8) (56) АвToрско" свидетельство С(л .Р № 964625 кл. Сз 06 ? 3, 05, i 98 .

Авторское свидетельство СОСP № !! 51946, кл. С 06 1= 3, 05, 1983. (54) УСТРО?"1 {. ВО Д. 1Я ВВОДА И НФОРМАЦИИ (57) Изобретение (i носится и вычислительной технике и может быть испо,-.ьзовано

ÄÄSUÄÄ 1529211 Д 1 в многоканальных информационно-измерительных системах. Целью изобретения является по вы шение падеж ности устройства.

Устройство для ввода информации содержит компараторы 1, мультиплексор 3, блок 4 памяти, цифроаналоговый преобразователь 6, счетчики 2 и 7, блок 5 управления, ключи первой и второй групп 8 и 9. Устройство работает в двух режимах, при которых в первом цикле работы устройства входная информация фиксируется в блоке 4 памяти, во втором цикле, который по длительности меньше первого цикла, происходит считывание данных из блока 4 памяти. 1 з.п. ф-лы, 2 ил.

1529211

Фор.)<(<ли (!.)<)<)()етеки..

Изобретение относится к вычислительной технике и может быть использовано как совместно, при построении высокопроизводительных систем сбора и обработки аналоговых данных с использованием 3ВМ, так и отдельно, при построении многоканальных информационно-измерительных систем.

Целью изобретения является повып<ение надежности устройства.

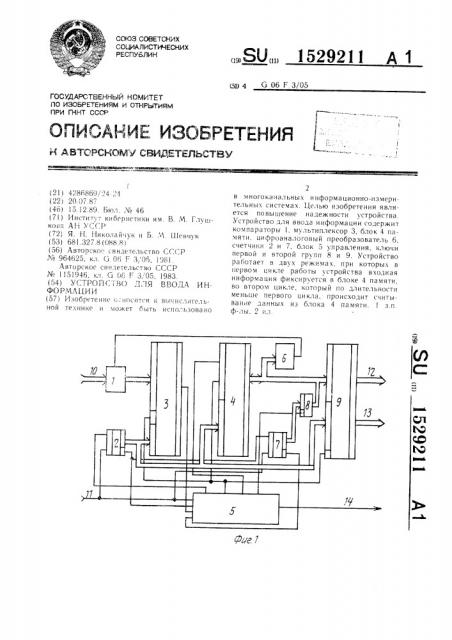

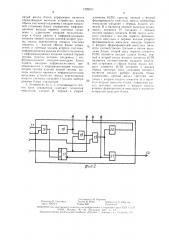

На фиг. 1 представлена структурная схема устройства лля ввода информации; на фиг. 2 — структурная схема блока управления.

Устройство содержит компараторы 1, первый счетчик 2, мультиплексор 3, блок 4 па мяти, блок 5 упра вления, („ ифроаг<алоговый преобразователь 6, второй счетчик 7, ключи первой и второй груlll! 8 и 9. вхолы и выходы устройства 10-- 14.

Блок 5 управления (фиг 21 содержит второй элемент ИЛИ !5, генератор 16 импульсов, TpHtlер 17, элеме((т И 18, первый элемент ИЛИ !9, первый H второй формп рователи 20 и 2! импульса.

Устройство для ввода информации рабо тает сле;<ующим образом.

Входные аналоговые сигналы поступак)т

H3 RXO. hl » (TpOH(. TB3 10. На Е3 ХОДЫ Ком Пс!раторов 1 пода« Гс5! I3blxo, (нОЙ си! на.! цифроапа Ioi îâог<) преобразовател5l 6. . 1.)я приВС l(пия хстроист(33 Б исхолно(0(. (Оя нпе п012(тся си (Hdë на » пра В,1 яю(ци и вход 11. При этом первый и второй с Еетчики <Пот(3«т«твенно 2 и 7, триггер 17 о inK;I

;) упр;(Бления сбрасываются в нулевое о«таяние. В этом состоянии сигналом с перв< го ()ыхода триггера 17 разрешается pat)oT2 мУльтиплексоРа 3, блок 4 па vtttT по

Б: оду запись-«читыванис переволиг«я Б режим записи, запрещает H пабота ключей

9 второй группы. <:пгнdлом с второго f!I,(хола Iрипера 17 (четвс ртого выхода блока 5 управ«(ени5!) разрс пается раоота ключей 8 первой груltl(i I

11oc,I(cнятия cHI H3.iЕ2 «х llр;Е(3.)яlotllег0 f3xo. 3 !! у«! рой«тва устройс гво продолжае-, p;- бс) Гу под дей!«т()иех! генераторе! 16 импульсов.

При этом первыи и второй с н)тчики соответственно 2 и 7 работают B прямом счете 1альнейц)ая работа устройстB3 осуществляется на протяжении двух циклов.

В первом цикле при нулевом ко (е на Bhtxo;13x второго счетчика 7 и последовательном наращивания двоичного кода первого c«cr«I ка 2 происходит синхронное изменение àлресов блока 4 памяти устройства и каналов ком м ута ции мультиплексора 3. В ка ждо.

Ка НаЛЕ, В КОТОРОМ (ilx (j >vol > с(дЛ фОР М Ируется сигнал «Bыхода мультиплексора

3, который поступает на вход блока 5 управления. При этом формирователь 20 им пульса обеспечивает форми рова ние и мпульсного сигнала, который с третьего выхода блока 5 управления поступает на

Вход управления блока 4 памяти.

Таким образо>t, в процессе наращивания двоичного коЛ2 Бо втором счетчике 7 происхолегг IIOc Ееловаг«: ьная запись кодов измpре нных зн а чен H Й Б соотвст«тВуK) шие адреса блока 4 памяти. Второй цикл работы устройства насту! ает B xI,)3!CíT переполнения Бropoto с ICTHHK2 7, на выходе переноса которого формирустся импуль«, KQTopb(H пеРеоРасывает тРиггеР 17 блока vllPBBления Б B.IHHH»<нос СОСT05(HH(11ри BTÎ)ОБ T()иГI Pг)2 17 соответственно заире thd ют работу М3 л ьтиП.Е(. КСО Pi! <>, f10 Б» О (За IIÈ ".Ь- ГЧИ ТЫ Б3!I И Р переключают б.юк 4 памят в режим «Еитывания, разре(е(ают р,)боi" к1к)чеЙ 9 Второй гру ппы и запрешан)1 работу ключей

8 первой гру(llli>i. В дальнейшем «читыБание .!àítlhlx происходи1 «о Bcех Bëðpcoê

0.)ока 4 lta÷tITH пол действием генераторы

16 импульсов блока 5 х прав.)с ния до иерепол и(> ни я ll(>pBo I «че "i <1 кс! 2 Вы хо,i H3 H ие!формация данные и адреса(пс редаются

Hd Бнс IIIHH< ) «! ройства «Вы.,олов ключей

9 Второй группы «и

BT0J)0Г0 фоf)XIH j)ОB2 Cе.)H .). H») f1 »,::i d б). )Kа 5 управления .. выхода пере н)лнения первого счетчика

2 «игнал перс полнения через ьто.)AH эле;ент

15 И,.1И .Io« tx паст II2 Второй вхол триггера

17 и переВО.цнт (."ÃO Б н ..)Бвo(. c0(òOÿi! H(110«.1(:: эт<)! О тстрОЙстВО Опять пе()еходит В режим аналого-цифрового RpP05)j)330BiIIIH5(и

«е! и:t«H и н<()о()

1. > с тj)ОистБО для ВВо L3 и нф" р ма ци и, <Од(Ржс(песе ко vlf13PdTÎPhl, пеРВ(>(Й и е)тОРОЙ

« И (

ПOДКГЕЮЧСН К»> П!)3ВЛЯК)(ЦИМ ВХОДБXI К<)МП3—

PiiT0P0 l3, Е)ХО (bl KOTO Phi X H B. ЯК)ТСЯ I If<()ОРМБЦИО НЫX! It ВХОДБМИ Х «ТЭОЙ«тва, BX<),1 Н3:! ИЛ!>ПОИ у«1lxo;I, блока управления с)>е.синсii «О счетным Bxo;lîм первого «ЕС1 <ика, 0(ли«afo e(.<я тем, что, с целью новы:пения

H3«

Составитель И. Карпова

Редактор О. Спесивых Техред И. Верес Корректор Л. Обр нап

Заказ 7642, 44 Тираж 668 Поди испо<

ВНИИГ1И Государственного комитета по изобретениям н открытия;. при ГКНТ СССР

113035, Москва, Ж вЂ” -35, Раугнская наб, д. 4 5

Производственно-издательский комбинат «Патент», t Ужгород, уп 1агарина, 1О! пятый выход блока управления является управляющим выходом устройства, входы сброса счетчиков соединены с входом начальной установки блока управления, информационные выходы первого счетчика соединены с адресными входами мультиплексора и блока гамяти и информационными входами первой группы ключей второй группы, выход переполнения первого счетчика соединен с входом сброса блока управления и счетным входом второго счетчика. информационные выходы которого соединены с информационными входами ключей первой группы, выходы которых соединены с информационными входами-выходами блока памяти, входами цифроаналогового преобразовагеля и информационными входами второй группы ключей второй группы, выходы которого являются информационными выходами устройства, выход переполнения второго счетчика соединен с входом выбора режима олока управления.

2. Устройство по и. 1, отличающееся тем, что блок управления содержит генератор импульсов, элемент И, первый и второй элементы ИЛИ, триггер, первый и второй формирователи импульса, выход генератора импульсов соединен с первым входом элемента И и является первым выходом блока, выход элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом первого формирователя импульса и первым входом второго формирователя импульса, выходы гервого

1О и второго формирователей импульса являются соответственно третьим и пятым выходами блока, второй вход первого элемеHT6

ИЛИ является входом записи блока, первый и второй входы второго элемента ИЛИ являются соответственно входами началь15 ной установки и сброса блока, выход второго элемента ИЛИ соединен с входом сброса триггера, вход установки которого является входом выбора режима блока управления, прямой выход триггера соединен с вторым входov. элемента И I> является вторым выходом блока, инверсный выход триггера соединен с вторым входом второго формирователя импульса и является четвертым выходом блока.