Многоканальный сигнатурный анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может использоваться в контрольно-испытательной аппаратуре. Целью изобретения является повышение достоверности контроля. Многоканальный сигнатурный анализатор содержит блок 1 приема информации, формирователь 2 сигнатур, блок 3 сравнения, блок 4 оперативной памяти, блок 5 управления, блоки 6,7 постоянной памяти, счетчик 8. Точность и достоверность контроля можно повысить путем согласования длительности цикла анализа с характером и типом контролируемых данных. Длительность цикла анализа может быть установлена индивидуально для каждого проверяемого устройства. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Ю4! G06F 1100

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4219!53/24-24 (22) 03.04.87 (46) 15.12.89. Бюл. № 46 (72) В. П. Карасев, В. А. Шаньгин и М. Г. Швец (53) 681.326.7 (088.8) (56) Электроника, 1977, № 5, с, 23-33.

Авторское свидетельство СССР № 1246098, кл, G 06 F 11/16, 1983. (54) МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР (57) Изобретение относится к вычислительной технике и может использоваться в контрольно-испытательной аппаратуре.

„„SU„„1529221 A 1

Целью изобретения является повышение достоверности контроля. Многоканальный сигнатурный анализатор содержит блок 1 приема информации, формирователь 2 сигнатур, блок 3 сравнения, блок 4 оперативной памяти, блок 5 управления, блоки 6, 7 постоянной памяти, счетчик 8. Точность и достоверность контроля можно повысить путем согласования длительности цикла анализа с характером и типом контролируемых данных. Длительность цикла анализа может быть установлена индивидуально для каждого проверяемого устройства. 1 з.п. ф-лы, 3 ил.

1529221

Изобретение относится к области вычисительной техники и может испоьзоваться в контрольно-испытательной аппаратуре.

Целью изобретения является повышение ,достоверности контроля. 5

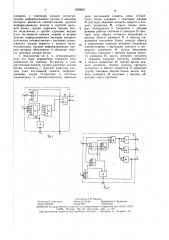

На фиг. 1 показана схема многоканального сигнатурного анализатора; на фиг. 2 — схема блока приема информации; на фиг. 3 — схема блока управленияия.

Многоканальный сигнатур ный анализатор (фиг. 1) содержит блок 1 приема информации, формирователь 2 сигнатур, блок 3 сравнения, блок 4 оперативной памяти (ОЗУ), блок 5 управления, первый блок постоянной памяти (ПЗУ) 6, 15 второй блок постоянной памяти (ПЗУ) 7 и счетчик 8.

Блок приема информации (фиг. 2) содержит регистр 9, первый 10 н второй 11 мультиплексоры, элемент 12 И и узел 13 постоянной памяти (ПЗУ).

Блок 6 управления содержит элемент И 14, счетчик 15, элементы И 16 — 19 узел 20 постоянной памяти (ПЗУ) и D-триггер 21.

Формирователь 2 сигнатур выполнен по параллельной схеме на 16 разрядов. 25

Сигнатурный анализатор работает следующим образом.

В исходном состоянии все регистры и счетчики установлены в состояние «О».

Группа информационных входов анализатора подключена к многоразрядной магистрали, к которой подключены контролируемые устройства. На вход «Старт/

/стоп» анализатора поступает сигнал «Цикл анализа», который определяет интервал контроля. На группу тактовых входов поступает серия тактовых импульсов (например Т1 — T4), которой синхронизирована работа контролируемых устройств и цепей управления анализатора.

Перед началом работы в счетчик 8 внешним устройством заносится код, оп- 4р ! ределяющий начальный адрес программы Al, При записи адреса Al в счетчик 8 на выходе ПЗУ 6 установится код эталон ной сигнатуры, которая должна получиться . на выходе формирвателя 2 сигнатур при правильной работе контролируемого уст- 46 ройства. На выходе ПЗУ 7 установится, код адреса первого проверяемого устройства. Устройство, получив этот код, подключится к магистрали контроля, и информация будет поступать на группу информационных входов. Работа анализатора начинается по сигналу «Цикл анализа», поступающему на вход «Старт/стоп» (низкий уровень). По этому сигналу блок 1 начинает. прием информации с магистрали, причем информация фиксируется на регистре одним из тактов Т l — T4. Затем информация поступает на информационный вход параллельного формирователя 2. С задержкой, необходимой для прохождения информации через комбинационный блок параллельного формирователя 2, блок 1 вырабатывает синхросигнал для формирователя. Н а регистре формирователя фиксируется текущее значение сигнатуры. Следующее значение кода, которое поступит на вход анализатора, будет суммироваться с предыдущим значением сигнатуры, и результат будет вновь записан в регистр анализатора и т. д. до тех пор, пока последнее слово контролируемой информации не поступит на вход анализатора. Этот момент наступает, когда сигнал «Цикл анализа», поступающий на вход «Старт/

/стоп», установится в состояние «1». При этом запись информации в формирователь 2 и выработка синхросигналов для формирователя 2 блокируются. Блок управления определяет число циклов анализа для данного устройства. Если для данного устройства необходимо выработать сигнатуру за два цикла анализа, то блок 5 не вырабатывает сигналов на своих выходах. При установлении сигнала «Цикл анализа» в состояние «О» начинается второй цикл работы анализатора. По окончании его в анализаторе сформируется значение сигнатуры, определенное за два цикла анализа. Блок управления зафиксирует в ОЗУ 4 значение кода сигнатуры и значение результата сравнения с выхода блока 3. Происходит обнуление внутреннего регистра параллельного анализатора, В счетчик 8 добавится «+ 1» и в нем установится адрес (Al +

+ 1). Начнется определение сигнатуры и сравнение ее с эталоном для следующего устройства. Так будет продолжаться, пока в счетчике 8 не установится последний адрес программы (А1+К), после выполнения которого блок 5 блокирует выработку синхросигнвлов. Для запуска анализатора необходимо в счетчик занести начальный адрес новой программы.

Блок 1 приема информации работает следующим образом. Группа информационных входов анализатора подключена к D-входу 16-разрядного регистра 9. На вход Ч поступает один из тактов Tl — Т4, Конкретное значение такта определяется кодом

ПЗУ, соответствующим адресу подключенного к магистрали устройства. Код с выхода регистра 9 поступает на информационный вход анализатора. Синхросигнал для анализатора формируется на мультиплексоре 11 с задержкой, время которой определяется быстродействием комбинационной части сигнатурного анализатора (для примера взято два такта), На время, пока значение сигнала «Цикл анализа» соответствует высокому уровню, запись информации в регистр 9 и выдача синхросигнала в анализатор бл окиру ются.

Блок 5 управления (фиг. 3) работает следующим образом. В исходном состоянии счетчик 15 и D-триггер 21 находятся

152922I

t0

Формула изобретения в состоянии «О». Кроме того, по адресу ПЗУ (A=O) записан код «0...0», поэтому при поступлении сигнала «Цикл анализа» (по высокому уровню) продублируется установка D-триггера 21 в состояние «О» (так как на вход D) подан сигнал «О» с выхода ПЗУ 20).

При установке в счетчике 8 кода начального адреса программы на первом выходе ПЗУ 20 установится код, который . определяет, сколько циклов анализа будет подключено к магистрали данное устройство. На втором выходе ПЗУ 20 установится код «1». По отрицательному перепаду сигнала «Цикл анализа» D-триггер 21 установится в состояние «1», а в счетчик 15 занесется код с выхода ПЗУ 20, соответствующий числу циклов анализа.

Кроме того, высокий уровень с выхода

D-триггера 21 поступит на входы элементов 14 и 16. В течение цикла анализа сигнал «Цикл анализа> представляет собой «О», и на выходе элементов 14 и 16 сигнал тоже соответствует состоянию

«О». По окончании цикла анализа на входе «Старт/стоп» установится уровень «1».

При этом по такту Тl на вход «-1» счетчика 15 поступит сигнал, по которому его состояние уменьшится на единицу. Формирование синхросигналов для блока ОЗУ 4 и счетчика 8 блокировано, пока содержимое счетчика не будет равно нулю и на выходе «-О» не появится высокий уровень.

Это произойдет, когда выполнится установленное число циклов анализа. По такту ТЗ на выходе элемента 18 появится сигнал, по которому произойдет запись в блок

ОЗУ 4. По такту Т4 на выходе элемента 19 появится сигнал, которым содержимое счетчика 8 увеличивается на единицу, и D триггер 21 устанавливается в состояние «О». Конец программы определяется содержимым кодом ПЗУ 7, ПЗУ 13 и ПЗУ 20 при считывании по последнему адресу программы. В эти ячейки должны быть записаны коды, соответствующие состоянию «О». При этом к магистрали не будет подключено ни одно устройство. В блоке 1 все входы мультиплексоров 10 и 11 будут отключены. В блоке 5 с выхода ПЗУ 20 на вход D

D-триггера поступит сигнал, соответствующий состоянию «О». Схема будет находиться в состоянии ожидания записи следующего начального адреса программы.

Результаты анализа проверяемых устройств будут храниться в блоке ОЗУ, которое позволяет повысить точность контроля за счет анализа результата по совокупности сигнатур.

Применение в блоке приема программируемого выбора такта фиксации информации на магистрали позволяет повысить точность и достоверность контроля за счет

36

55 выбора момента фиксации независимо для каждого контролируемого устройства.

Точность и достоверность контроля можно повысить путем согласования длительности цикла анализа с характером и типом контролируемых данных. В предлагаемом устройстве длительность цикла анализа может быть установлена индивидуально для каждого проверяемого устройства.

1. Многоканальный сигнатурный анализатор, содержащий формирователь сигнатур, блок сравнения, блок управления, два блока постоянной памяти, счетчик, группа разрядных выходов которого соединена с группами адресных входов блока управления, первого и второго блоков постоянной памяти, группа выходов второго блока постоянной памяти образует первую группу информационных выходов анализатора, группа выходов первого блока постоянной памяти соединена с первой группой входов блока сравнения, вторая группа входов которого соединена с группой выходов формирователя сигнатур, вход сброса которого соединен с первым выходом блока управления, второй выход которого соединен со счетным входом счетчика, отличающийся тем, что, с целью увеличения достоверности контроля, анализатор содержит блок приема информации и блок оперативной памяти, группа выходов которого образует вторую группу информационных выходов анализатора, группа выходов формирователя сигнатур и выход блока сравнения соединены с соответствующими информационными входами блока оперативной памяти, группа адресных входов которого соединена с группой адресных входов блока приема информации и подключена к группе разрядных выходов счетчика, вход записи блока оперативной памяти подключен к третьему выходу блока управления, группа информационных входов анализатора соединена с группой информационных входов блока приема информации, группа выходов которого соединена с группой информационных входов формирователя сигнатур, тактовый вход которого соединен с выходом блока приема информации, группа тактовых входов анализатора соединена с одноименными группами входов блока приема информации и блока управления, входы «Старт-стоп» которых объединены и образуют одноименный вход анализатора, причем блок приема информаци содержит регистр, два мультиплексора, узел постоянной памяти и элемент И, выход которого является выходом блока, вход «Старт-стоп» блока соединен со входом сброса регистра и инверсным входом элемента И, прямой вход которого соединен с выходом второго мультиплексора, вход первого мультиплексора

1529221 iO

Фиг 1

Составитель М. Иванов

Редактор О. Спесивых Техред И. Верес Корректор О. Кравцова

3а каз 7642/44 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж вЂ” 35, Раушская на 6., д. 4/5

Производственно-издательский комбинат «Патент», r. Ужгород, ул. Гагарина, 10! соединен . с тактовым входом регистра, группы информационных входов и выходов которого являются соответственно группой информационных входов и группой выходов блока, группа адресных входов блока подключена к группе адресных входов узла постоянной памяти, первая и .вторая группы информационных выходов которого соединены соответственно с группами управляющих входов первого и второго мультиплексоров, группы информационных входов которых объединены и образуют группу тактовых входов блока.

2. Анализатор по п. 1, отличаюший ся тем, что, блок управления содержит пять элементов И, счетчик, D-триггер и узел постоянной памяти, группа адресных входов блока соединена с группой адресных входов узла постоянной памяти, информационные входы D-триггера и счетчика подключены к соответствующим выхода м узла постоянной памяти, вход «Стартстоп» блока соединен с тактовым входом

D-триггера, первыми входами первого и второго элементов И, вторые входы которых. объединены и соединены с входом режима работы счетчика и выходом D-триггера, вход сброса которого подключен к выходу пятого элемента И и выходу управления счетчиком блока, выходы сброса и управления записью которого соединены соответственно с выходами третьего и четвертого элементов И, выход обнуления счетчика соединен с третьим входом второго элемента И, выход которого соединен с первыми входами третьего, четвертого и пятого элементов И, третий выход первого элемента, вторые выходы третьего, четвертого и пятого элементов И образуют группу тактовых входов блока, выход первого элемента И соединен с входом обратного счета счетчика.