Статический d - триггер с парафазным управлением

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации счетчиков, регистров и других технических средств этой области. Цель изобретения - повышение быстродействия при сохранении помехозащищенности. Для этого в Д-триггер введены элементы ИЛИ-НЕ 3,4, объединенные выходы 5,6 "Монтажное ИЛИ" и шина 8 инверсного синхросигнала. Устройство также содержит элементы И-ИЛИ-НЕ 1,2, шину 7 прямого синхросигнала, шины 9,10 прямого и инверсного информационных сигналов, прямой и инверсный выходы 11,12. В предлагаемом Д-триггере сокращено время переходных процессов на выходах до одной элементарной задержки логического элемента. 1 ил.

СООЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4,Н О К 3/037

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

Фиг.!

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

rlO ИЭОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4434029/24-21 (22) 22,04.88 (46) 15.12.89. Бюл. Ю 46 (71) Московский институт электронной техники (72) В.И.Старосельский, В.И.Суэтинов, В.П.Тимошенков, Л.Н.Кравченко и А.Н.Сапельников (53) 621.374.3 (088.8) (56) Букреев И.Н, и др. Микроэлектронные схемы цифровых устройств. - М.:

Сов.радио, 1975, с. 59, рис.2.4(в).

Алексеенко А.Г. и др. Микросхемотехника. — М.: Рад. и связь, 1982, с. 176, рис.4.15r (прототип). (54) СТАТИЧЕСКИЙ 0-ТРИГГЕР С ПАРАФРЗНЫМ УПРАВЛЕНИЕМ (57) Изобретение относится к автоматиI

„„Я0„„1529418 А1

2 ке и вычислительной Технике и может быть использовано для реализации счетчиков, регистров и других технических средств этой области. Цель. изобретения - повышение быстродействия при сохранении помехоэащищенности.

Для этого в Р-триггер введены элементы ИЛИ-НЕ 3, 4, объединенные выходы

5 и 6 МОНТАЖНОЕ ИЛИ и шина 8 инверсного синхросигнала . D-триггер также содержит элементы И-ИЛИ-НЕ 1,2, шину

7 прямого синхросигнала, шины 9, 10 прямого и инверсного информационных сигналов, прямой и инверсный выходы

11, 12. В предлагаемом D-триггере сокращено время переходных процессов на выходах до одной элементарной задержки логического элемента. 1 ил.

1529418

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации счетчиков, регистров и других технических средств этой области.

Цель изобретения — повышение быстродействия при сохранении помехозащищенности.

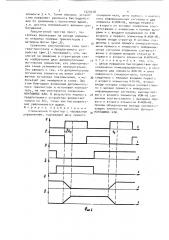

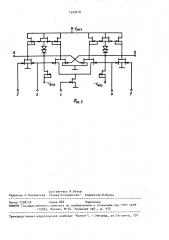

На фиг.1 приведена структурная логическая схема статического D-триггера с парафазным управлением; на фиг.2 — временные диаграммы его работы; на фиг.3 — электрическая схема

D-триггера на полевых транзисторах с затвором Шотки на основе арсенида галлия.

Предлагаемый триггер содержит первый 1, второй 2 элементы И-ИЛИ-НЕ, первый 3 и второй 4 элементы ИЛИ-НЕ

3 и 4,. объединенные выходы 5 и 6, МОНТАЖНОЕ ИЛИ, шины 7 и 8 прямого и инверсного синхросигнала, шины 9 и 10 прямого и инверсного информационных сигналов, а также прямой 11 и инверс- д ный 12 выходы.

На фиг.1 выходы элементов И-ИЛИ-НЕ

1 и 2 соединены соответственно с инверсным выходом 12 (a), с прямым вы" ходом 11 (g) и с входами расширения по ИЛИ элементов И-ИЛИ-НЕ 2 и 1, первые входы структур И которых соединены с шиной 7 прямого синхросигнала (С), шина 9 прямого информационного сигнала (D) и шина 10 инверсного информационного сигнала (Б) соединены соответственно с вторыми входами структур И элементов И-ИЛИ-НЕ 1 и 2.

Шина 8 инверсного синхросигнала (C) соединена с первыми входами элементов 40

ИЛИ-НЕ 3 и 4, вторые входы которых соединены соответственно с шинами

10 прямого и инверсного информационных сигналов, выходы элементов ИЛИ-НЕ

3 и 4 соединены соответственно с вы-. 4 ходами элементов И-ИЛИ-НЕ 1 и 2.

Объединенные выходы 5 элементов ИЛИНЕ 3 и И-ИЛИ-НЕ 1 выполняют функцию

МОНТАЖНОЕ ИЛИ, объединенные выходы 6 элементов ИЛИ-HE 4 и И-ИЛИ-НЕ 2 также

50 выполняют функцию МОНТАЖНОЕ ИЛИ.

Предлагаемый D-триггер относится к классу синхронизируемых уровнем триггеров.

Устройство работает следующим образом.

В режиме хранения прямой синхросигнал С на шине 7 и на входах элементов 1 и 2 равен 0", инверсный

С вЂ” на шине 8 и на входах элементов

3 и 4 — " 1" (фиг.2). В этом состоянии на выходах элементов 3 и 4 сохраняются "0". Информационные сигналы D u D заЬлокированы логическим нулем синхросигнала С в структурах И элементов

1 и 2, а на выходах 11 и 12 триггера сохраняются сигналы, записанные ранее, например, на выходе 12 — "0", а на выходе 11 - 1 . При изменении парафазных сигналов на шинах 7 и 8 и переходе в режим записи на входе С (шина 7) устанавливается " 1", а на входе С (шина 8) "0". Если на информационные входы D u D (шины 9 и 10) поданы в этот момент соответственно

"0 и "1, то изменяется состояние триггера на противоположное. При этом

"1 появляется на инверсном выходе 12 через время t> Ьлагодаря прохождению сигнала через элемент 3 и соединение

МОНТАЖНОЕ ИЛИ. Переход прямого выхода триггера из 1 в "0" происходит также через t, поскольку сигнал проходит через элемент 2 и соединение МОНТАЖНОЕ ИЛИ.

Таким образом, в отличие от прототипа "0" и "1" устанавливаются на выходах триггера через время t (МОНТАЖНОЕ ИЛИ задержки не вносит). Уменьшение задержки появления 1 до времени переключения одного логического инвентора достигается за счет включения логических элементов ИЛИ-НЕ 3 и 4 между входами и выходами триггерапрототипа. Сохранение помехозащищенности в предлагаемом ус.. ройстве оЬусловлено отсутствием состязаний в процессе переключения триггера, так как режим хранения в данном триггере имеет место только в том случае, когда прямой сигнал синхронизации равен "0", а инверсный — "1". Если в процессе переключения возникают другие сочетания синхросигналов, то реализуется режим записи. При этом быстрая. запись происходит, если прямой синхросигнал равен 1, а инверсный — "0, как и при описании случая, когда oba синхросигнала равны "1", запись осуществляется только по входу элемента 1 или 2, как в триггере-прототипе, поскольку прохождение сигнала через элементы 3 и 4 блокировано "1" инверсного синхросигнала. При равенстве оЬоих синхросигналов 0, происходит запись в триггере после прохождения

"!" на один из выходов триггера через

5 1529418 элементы 3 и 4. Таким образом, устройство позволяет увеличить Ьыстродействие по сравнению с прототипом вдвое, т.е. достичь минимального времени срабатывания.

Предлагаемый триггер прост, поскольку реализован на основе нормально открытых полевых транзисторов с затвором Шотки (фиг.3) ° !

О

Сравнение электрических схем триггера-прототипа и предлагаемого устройства (фиг.3) показывает, что, несмо1ря на введение в структурную схему изоЬретения двух дополнительных логических элементов, его электрическая схема усложняется незначительно.

Это связано с тем, что дополнительные логические элементы не имеют собственных истоковых повторителей, а ис- 2О пользуют уже имеющиеся в схеме. При этом Ьлагодаря включению дополнительного транзистора в истоковый повторитель, на нем реализуется соединение

МОНТАЖНОЕ ИЛИ. В результате мощность 25 предлагаемого устройства возрастает только на 204, тогда как быстродействие увеличивается вдвое. формула и з о б р е т е н и я

Статический D-триггер с парафазным управлением, содержащий шину прямого синхросигнала, шины прямого и инверс1 ного информационных сигналов и два элемента И-ИЛИ-НЕ, выходы первого и второго из которых соединены соо;ветственно с инверсным и прямым в ходами и с входами расширения по ИЛИ второго и первого элементов И-ИЛИ-НЕ, первые входы структур И которых сосдинены с шиной прямого синхросигнала, шины прямого и инверсного информационных сигналов соединены соответственно с вторыми входами структур И первого и второго элементов И-ИЛИ,-НЕ, отличающийся тем, что, с целью повышения Ьыстродействия при сохранении помехозащищенности, в него введены два элемента ИЛИ-НЕ и шина инверсного синхросигнала, которая соединена с первыми входами первого и второго элементов И.ЧИ-НЕ, вторые входы которых соединены соответственно с шинами прямого и инверсногс информационных сигналов, выходы пеового и второго элементов ИЛИ-HE cоединены соответственно с выходами первого и второго элементов И-ИЛИ-НЕ, причем объединенные выходы сооТВрТОТ вующих элементов выполняют функц:ю

МОНТАЖНОЕ ИЛИ.

1529418

Составитель А.Ранов

Редактор 11.Пчолинская Техред Л.Сердюкова Корректор И.Муска

Заказ 7758/54 Тираж 884 Подписное

8НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãoðîä, ул.Гагарина, 101