Устройство для сжатия цифровых телевизионных сигналов цветного изображения

Иллюстрации

Показать всеРеферат

Изобретение относится к технике телевидения. Цель изобретения - увеличение коэффициента сжатия. Устройство содержит АЦП 1, блок установки 2 опорного уровня, регистры 3, 4 и 12, блоки задержки 5 и 13, блоки сравнения 6 и 15, счетчики 7, 10 и 11, эл-т ИЛИ 8, эл-т И 9, коммутатор 14, блоки памяти 16 и 17, блок эл-тов ИЛИ 18, формирователь 19 кода синхронизации, преобразователь 20 кода и блок управления (БУ) 21. В устройстве информация о кадре изображения записывается в виде последовательности кодированных инструкций, каждая из которых содержит информацию о цветности J<SB POS="POST">I</SB> и длине D<SB POS="POST">I</SB> полосы. Цель достигается за счет использования построчно-весового кодирования. Для реализации процесса построчно-весового кодирования в устройстве код цветности текущего эл-та отображения сравнивается с кодом цветности предыдущего. В случае их совпадения значение кода длины полосы D<SB POS="POST">I</SB> увеличивается на единицу, а в случае несовпадения или превышения длиной полосы заданной величины 2<SP POS="POST">N</SP> (где 6≤N≤8) записывается новая инструкция (J<SB POS="POST">I</SB>, D<SB POS="POST">I</SB>). Устройство по п. 2 ф-лы отличается выполнением БУ 21. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU „„) 529471

А1 (504Н 04 N 7 ) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К А8ТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4374219/24-09 (22) 02.02.88 (46) 15.12.89. Бкл. М- 46 (72) H ..Ф. Сидоренко, А.В . Королев, Б.В. Остроумов, А.П. Антоненко, В.А. Петухов и А.Л. Огарок (53) 621.397.3(088.8) 2 (56) Авторское свидетельство ГСС1

Ф 1136325, кл. Н 04 N 7/18, 1982. (54) УСТРОЙСТВО ДЛЯ СЖАТИЯ ЦИФРОВЫХ

ТЕЛЕВИЗИОННЫХ СИГНАЛОВ ЦВЕТНОГО

ИЗОБРАЖЕНИЯ (57) Изобретение относится к технике телевидения. Цель изобретения — уве1529471

15 личение коэффициента сжатия. Устр-во содержит АЦП I блок установкй 2 опорного уровня, регистры 3, 4 и 12, блок задержки 5 и 13, блоки сравнения 6 и 15,,счетчики 7,,10 и 11, эл-т

ИЛИ 8, эл-т И 9, коммутатор; 14, блоки памяти 16 и 17, блок эл-тов ИЛИ 18, формирователь 19 кода синхронизации, преобразователь 20 кода и блок управления (БУ) 21. В устр-ве информация о кадре изображения записывается в виде последовательности кодированных инструкций, каждая из которых содержит информацию о цветности 3; и длине D; полосы, Цель

Изобретение относится к технике передачи и хранения цветных изображений в системах с применением телевизионных дисплеев и видеотерминалов, может быть использовано в автоматизированных системах отображения, об- 25 работки данных и управления.

Целью изобретения является увеличение коэффициента сжатия.

Сущность иэображения состоит в том, чо увеличение коэффициента 30 сжатия достигнуто благодаря применению построчно- весового кодирования

Кадр изображения в направлении сканирования разбивается на участки (полосы), в состав которых входят

35 элементы отображения одной цветности.

Информация о кадре изображения записывается в виде последовательности кодированных инструкций, каждая из которых содержит информацию о цветности (7,)и длине (D,) полосы. Разрядность кода j. (m) вь<бирается исходя из требован»й, предъявленных к системе. Так, при m = 8, число отображенных оттенков составит 2 = 256.

Разрядность кода D, (n) фиксированана и лежит в пределах. 1 сп ь llop

64 и более 937, — 256. Таким образом, целесообразно выбирать п в пределах

6 п с8.

Голосы длиной 6олее чем 2 разбиваются на части, длины которых не ч 55 превышают 2 и информация о них записывается в в»де нескольких инструкций, имеюп<»х одинаковые коды цветности (7,) . достигается за счет использования построчно-весового кодирования.Для реализации процесса построчно-весового кодирования в устр-ве код цветности текущего эл-та отображения сравнивается с кодом цветности предыдущего. В случае их совпадения значение кода длины полосы D. Уве< личивается на единицу, а в случае несовпадения или превьппения длиной и полосы заданной величины 2 (где

6 ь и 8)записывается новая инструкция (7., Dr) . Устро-во по и. 2 ф-лы

1 отличается выполнением БУ 21, 1 з,п. ф-лы, 2 ил.

В общем случае число инстгчкций (7;, D ) для каждого кадра и ображений различно и зависит от сложности (детальности) изображения

Для реализации процесса построчновесового кодирования необходимо код цвет»ости текущего элемента отображения сравнить с кодом цветности предыдущего. В случае их совпадения значение кода длины полосы D; увеличивается на единицу, в случае несовпадения <<ли превышения длиной по<< лосы величины 2 записывается новая

<инструкция (7., D. ).

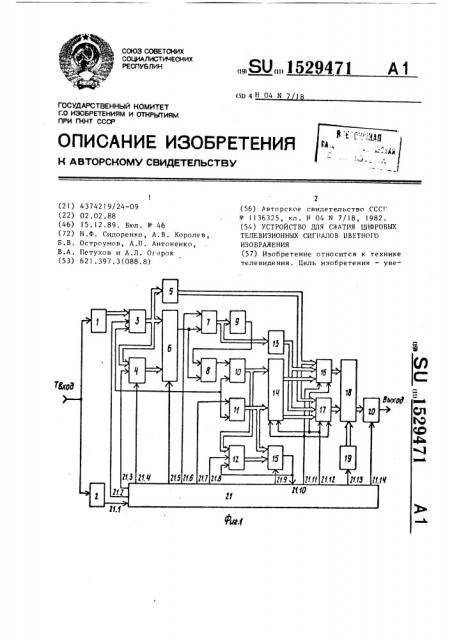

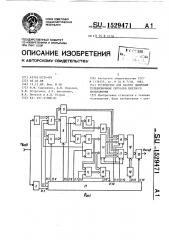

На фиг.1 г редстивлена структурная электрически схема устройства для сжатия цифровых телевизионных сигналов цветного изображения, на фиг.2 функциональная электрическая схема блока управления.

Устройство для сжатия цифровых телевизионных сигналов цветного изображения содержит аналого-цифровой преобразователь 1 (А1г11) блок 2 установки опорного уровня, первый регистр 3, второй регистр 4, первый блок 5 задержки, первый блок 6 сравнения, первый счетчик 7, элемент

ИЛИ 8, эпемент И 9, второй счетч»к

10, третий счетчик 11, третий регистр

12, второй блок 13 задержки, коммутатор 14, втор< и блск )5 сравнения, первый блок 16 «имяти, второй блок

17 памяти, блок 18 элементов И<Г, формирователь 19 к<,дв с»»хр< низа-ции, пресбризс ватель ?О кола, 6пок

21 упраг лс н»г<, Блок 21 упр,»

15 импульсов, второй триггер 26, первый счетчик-делитель 27, первый элемент И 28, второй элемент И 29, первый блок 30 задержки, второй счетчик-делитель 31, третий счетчик-делитель 32, третий триггер 33, второй блок 34 задержки, третий блок 35 задержки.

АЦП 1 преобразует аналоговый телевизионный сигнал в цифровой, где каждому элементу отображения соответствует m-разрядный код цветности.

Вход аналого-цифрового преобразователя 1 объединен с входом блока 2 установки опорного уровня и является входом устройства.

Блок 2 установки опорного уровня предназначен для формирования импульсов, соответствующих кадровым и строчным синхроимпульсам аналогового телевизионного сигнала.

Первый регистр 3 предназначен для записи, хранения и выдачи кода цветности текушего элемента отображения.

Второй регистр 4 предназначен для записи, хранения и выдачи кода цветности предыдущего элемента отображения.

Первый блок 5 задержки предназначен для задержки кода цнетности, поступающего на входы блоков памяти (16, 17), на время, требуемое для переключения второго счетчика 10.

Первый блок 6 сравнения предназначен для поразрядного сравнения ш- разрядных кодов цветности текущего и предыдущего элементон отображения и формирования на своем выходе единичного импульса в случае их несовпадения. Первый блок 6 сравнения содержит m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых подключены к входам элемента ИЛИ, ныход которого подключен к первому входу элемента И, второй вход которого является третьим входом первого блока 6 сравнения, первым входом которого служат первые входы элементов ИСКЛ10ЧАЮШЕЕ ИЛИ, вторые входы которых образуют второй вход блока 6 сравнения, выходом которого служит выход элемента И.

Первый счетчик 7 предназначен для формирования и- разрядно го кода длины полосы (D;), причем численно код

D ныражет количество элементов отоб1 ражения, цветность которых совпадает

29471

5

35 с цнетностью предшествующего каждому из них элемента отображения °

Элемент ИЛИ 8 предназначен для объединения ныхо. вЂ,он первого блока 6 сравнения и элеме: та И 9.

Элемент И 9 предназначен для формирования импульса переполнения первого счетчика 7.

Второй счетчик 10 предназначен для формирования кода адреса обращения к блоку памяти (16 или 17), работающему н режиме записи-н данном цикле обработки информации.

Третий счетчик 11 предназначен для формирования кода адреса обращения к блоку памяти (16 или 17), работающему в данном цикле обработки н режиме считывания.

Третий регистр 12 предназначен для записи, хранения и выдачи на второй групповой вход второго блока

15 сравнения кода максимального адреса (то есть адреса ячейки памяти блока 16 или 17 памяти в кото1 рую записана инструкция о последней полосе предыдущего кадра). Этот код необходим для формирования сигнала окончания считывания инструкций на выход устройства.

Второй блок 13 задержки предназ— начен для задержки кода длины полосы, поступающего одновременно на соответствующие групгонь1е входы первого и второго блоков (16 и 17) памяти, на время, требуемое для переключения второго счетчика 10.

Коммутатор 14 предназначен для поочередного подключения выходов второго, третьего счетчиков 1О, 11 и соответствуюшим групповым вхопам первого и второго блоков 16 и 17 памяти. Выбор блока памяти (16 или

17), к которому осуществляется подключение выхода того ипи иного счетчика (10 или 11), определяется комбинацией сигналов, поступающих на первый, второй входы (входы управления) коммутатора 14. Коммутатор 14 содержит четыре блока элементов И, два блока элементов ИЛИ, выходы которых являются групповыми выходами коммутатора 14, первый групповой вход которого образован первыми входами первого и второго блоков элементов И.

Второй групповой вход коммутатора 14 образован первыми входами третьего и четвертого блоков элементов И.

1529471

15

Второй блок 15 сравнения предназначен для сравнения кода максимального адреса и кода текущего адреса (т.е. адреса ячейки памяти, из которой осуществляется считывание инструкций), а также для формирования единичного импульса при совпадении этих кодов, Первый блрк 16 памяти предназначен для записи, хранения и выдачи инструкций (3,,D ) о коде изображения .

Назначение второго блока 17 памяти аналогично назначению первого блока

16 памяти.

Блок 18 элементов ИЛИ.предназначен для объединения выходов первого блока 16 памяти, второго блока 17 памяти, формирователя 19 кода синхронизации.

Формирователь 19 кода синхронизации предназначен для хранения и выдачи синхронизируюшей кодовой комбинаци перед началом считывания инструкций (3., D,) o кадре изображения.

Преобразователь 20 кода предназначен для преобразования считываемых в параллельном коде инструкций (3., D ) в последовательный код.

Преобразователь 20 кода содержит счетчик и мультиплексор, выход которого является выходом преобразователя 20 кода, первый вход которого подключен к информационным входам мультиплексора, адресные входы которого подключены к выходам счетчика, счетный вход которого является входом управления преобразователя

20 кода.

Блок 21 управления предназначен для обеспечения согласованной работы блоков устройства путем формирования и выдачи управляющих сигналов и тактовых импульсов на соответствующие входы блоков устройства.

Одновибратор 22 (фиг. 2) предназначен для формирования импульса заданной длительности при поступлении на его вход единичного импульса.

Первый триггер 23 предназначен для управления прохождением тактовых импульсов через второй элемент

И 29.

Инвертор 24 предназначен для формирования сигнала, запрещающего на время поступления на вход устройства кадровых и строчных синхроим20

55 пульсов формирование и выдачу тактовых импульсов на выходы, подключенные к входам блоков устройства, которые обеспечивают обработку поступающей информации.

Генератор 25 тактовых импульсов предназначен для формирования тактовых импульсов с частотой в (тп+и) раз большей, чем частотаобработки информации АЦП 1. Такая частота необходима для обеспечения считывания информации о кадре за время, не превьппающее время поступления кадра на вход устройства. В самом неблагоприятном случае (для изображения, в котором цветность каждого последующего элемента отображения отличается от цветности предыдущего) для описания одного элемента отображения требуется (m+n) бит, поэтому требуемая скорость считывания информации должна быть минимум в (m+n) раэ вьппе скорости обработки информации АЦП 1.

Второй триггер 26 предназначен для управления прохождением тактовых импульсов через первый элемент И 28.

Первый счетчик-делитель 27 имеет коэффициент деления, равный (m+n), и предназначен для формирования импульсов с частотой, равной частоте обработки информации АПП.

Первый элемент И 28 предназначен для управления выдачей тактовых импульсов на вход первого счетчика-делителя 27.

Второй элемент И 29 предназначен для управления выдачей тактовых импульсов одновременно на выход 1 блока

21 управления и вход третьего счетчика-делителя 32.

Второй блок 34 задержки предназначен для задержки импульсов, поступающих Hà его вход, на некоторое время ри1 I.„ i " (д " » л ьз — время задержки импульса соответственно на первом, втором, третьем выходах второго блока 34 задержки).

Второй счетчик-делитель 31 имеет коэффициент деления, равный числу элементов иэображения в кадре (М),и предназначен для формирования импульса, свидетельствующего о завершении обработки кадра.

Третий счетчик-делитель 32 имеет коэффициент деления, равный (m+n), и предназначен для формирования импульсон, каждый иэ которых формируется

50

1 i? 34 по окончании считывания (ш+п)-разрядной инструкпии па выход устройства.

Третий триг ер 33 имеет счетный вход (Т-триггер) и предназначен для формирования управляющих сигналов (по5 тенциалов) .

Первый блок 30 задержки предназначен дпя задержки импульсов, поступающих на его вход, ва различное время причем С > . (где г1

2 2 — время задержки соответственно на лервом, втором, третьем вьгходах первого блока 30 задержки).

Третий блок 35 задержки предназначен для разнесения во времени импульсов, поступающих на соответствукшие выходы блока 21 управления.

Устройство работает следующим образом. 20

Поступающий на вход устройства TBсигнал преобразуе.тся АПП ) в форму, где каждому элементу отображения соответствует m-разрядный код цветности, и подвергается построчно-весо- 25 вому кодированию. В результате кодирования информация о кадре представляется списком кодированных инструкций (J., D ), который записывается в первьй или второй блок (16, 17) 30 памяти. Выбор блока памяти осуществляется сигналами с выходов блока 21 управления. При этом, если информация î j Tñì кадре была записана в первый блок 16 памяти, то информапия

35 о (j+1) м кадре запишется во второй блок ) 7 памяти. Одновременно с про— цессом записи сжатой информации о (j+1)-кадре во второй блок 17 памяти иэ первого блока 16 памяти будет г0 осуществляться считывание инструкций о j òîì кадре на выход устройства. Информация о следующем (j+2) -м кадре запишется в освободившийся первый блок 16 памяти. Таким образом, 4 запись информации о каждом новом кадре будет осуществляться в освободившийся блок памяти.

Работу устройства рассмотрим по структурной схеме (фиг.)).

В исходном состоянии первый регистр 3, второй регистр 4, второй счетчик 10, третий счетчик 11 обнулены. В третий регистр )2 записан код максимального адреса предыдущего 55 кадра или, если на вход устройства поступает первый кадр, — нулевая комбинация. В один из блоков памяти ()6 или 17) записаны кодированные инструкции (Л., D. ) о пр .- IIIyII v« кадре (в случае, I.BI да па вх л устройства пс ступает первый ка I!>, < ба блока памяти обггулпы) . Для улг ботва рассмотрения р;боты допустим, что сжатая информация о иредыдушем кадре записана во второй блок 17 памяти.

С поступлением на вход устройства аналогового ТВ-сигнала блок 2 установки опорного уровня формирует импульс, соответствующий кадровому синхроимпульсу, и выдает его на вхогг 2 блока 21 управления, разрешая цикл работы. АЦП 1 преобразует аналоговый сигнал I III--ðëçðÿäный код цветности, который поступает на групповой вход первого регистра 3. Этот код соответствует текущему элементу ото— бражения С приходом тактовг го импульса с блока 21 угравления на первый вход первого регистра 3 код записывается в регистр. По приходу тактового импульса с блока 21 управления на первый вход второго регистра 4 в этот регистр записывается код, поступаюгций с группового выхода первого регистра 3. 3а счет того, что импульс на выходе 4 блока 21 управления опережает импульс на выходе 3, во второй регистр 4 запишется код цветности предыдущего элемента отображения (или, если начггнается сбработка нового кадра, — нулевой комбинации). Коды цветности текущего и предыдущего элементов отображения, поступающие с групповых выходов соответственно первого, второго регистров 3, 4 на групповые входы первого . блока 6 сравнения, поразрядно сравниваются.С приходом тактового импульса с выхода Ь блока 2) управления на вход управления первого блока 6 сравнения на его выходе формируется сигнал результата сравнения. Этот сигнал одновременно поступает на гервый вход первого счетчика 7 и — через элемент

ИЛИ 8 — на первый вход второго счетчика 10.

В случае различия кодов цветности соседних элементов изображения на выходе первого блока 6 сравнения формируется единичный импульс, обнуляющий первый счетчик 7 и увеличивающий состояние второго счетчика 10 на единицу. Если коды цветности соседних элементов совпадют, то под воздействием нулевого потенциала, поступаю— щего с выхода блока 6 сравнения, вто9471 )2

1О

45 ся.

55

11 152 рой счет их 10 сохранит свое состояние неизменным, а первый счетчик 7 под воздействием импульсов с ныхода 7 блока 21 управления увеличит свое состояние на единицу. Параллельный код цветности элемента (7,) с выхода первого регистра 3 через первый блок 5 задержки одновременно поступает на первые групповые входы блоков памяти (16, 17).Параллельный код длины полосы (П;) с группового выхода первого счетчика 7 одновреме»»но поступает на групповой вход первого элемента И 9 и — через второй блок 13 задержки— на вторые групповые входы блоков памяти (16, 17) .

Коммутатор 14 осуществляет подключение группового выхода второго счет,чика 10 к третьему групповому входу блока памяти, работающего в режиме записи (в рассматриваемом случае первого блока 16 памяти). Таким образом, по адресу формируемому вторым счетчиком 10, в первый блок 16 памяти производится запись кодированной инструкции (3., D .), Если коды

1 1 цветности текущего и предыдущего элементов отображения совпадают, то запись новой инструкции (с измененным

D;) производится по старому адресу. Если коды цветности текущего и предыдущего элементов изображения не совпадают, то запись новой инструкции производится по новому адресу.

Так как запись н блок памяти производится асинхронно, то смена адреса на третьем групповом входе блока памяти должна опережать смену кодов (3», D.) соответственно на первом, ° ! втором групповых входах того же блока памяти. Для выполнения этого условия используются первый, второй блоки 5, 13 задержки. Если длина

h полосы преньппает 2 элементов изображения, то кодирование происходит следующим образом.

При полном заполнении первого счетчика 7 (т.е. когда на его выходах установится и единиц ) на вьг ходе элемента И 9 формируется единичный потенциал, который проходя через элемент ИЛИ 8, воздействует на первый вход второго счетчика 10, при этом состояние счетчика 10 не меняется и инструкция (3;, Э,) записывается в блок 16 памяти по старому адресу. С приходом следующего тактового импульса на второй вход перного счетчика 7 этот счетчик обнул»»ется при этом ча выходе элемента И 9 формируется нулевой потенциал, образуя задний фронт импульса °

lIo этому заднему фронту второй счетчик 10 увеличивает свое состояние на единицу, и »»оная инструкция (с прежним », и D; = О) записывается в блок 16 памяти по новому адресу. !

Г!ри поступлении на вход устройства строчного синхроимпульса блок 2 установки опорного уровня выдает на вход 2 блока 21 управления импульс, синхронный строчному синхроимпульсу, при этом на время длительности этого импульса блок 21 управления пере— стает ныданать тактовь»е импульсь! на

«»вь»ходь» 3, 4, 6, 7. Это приводит к тому, что процедуре построчп -весеного кодирования будут подвергаться только те части полного ТВ-сигнала, которые несут информацию о цнетности.

После обработки последнего элемента кадра с нь»хода 9 блока 21 управления на первый вход третьего регистра 12 поступит импульс, под воздействием которого н регистр 12 запишется код максимального адреса, поступан»щит с группового выхода второго счетчика 10. По окончания записи кода максимального адреса в регистр 12 на выходе 5 блока 21 управления формируется импульс, обнуляющий первый регистр 3, второй регистр

4, второй счетчик 10, третий счетчик

11. .Одновременно с этим на выходе 11 блока 21 упранлен» я устанавливается нулевой потенциал, а на выходе 12 блока 21 управления — единичный потен. циал, чем достигается смена режимов работы первого и второго блоков (16, 17)памяти, На этом цикл кодирования текущего кадра изображения завершаетС поступлением кадрового синхроHh»»»óàbñà следующего кадра на вход устройства начинается цикл считывания.из первого блока 16 памяти инструкций о предь»душем кадре и коди- рования следующего кадра. Кодирование следующего кадра изображения осуществляется аналогично рассмотренному, с той разницей, что запись инструкций производится но второй блок

17 памяти.

152

Считынание информании на выход устройства осуществляется следующим образом.

С началом поступления с выхода блока 2 установки опорного уровня на вход 2 блока 21 управления им. пульса, соответствующего кадровому синхроимпульсу, с выхода 2 блока 21 управления на вход формирователя !9 кода синхронизации выдается единичный потенциал, с выхода 1 блока 21 управления на вход управления преобразователя 20 кода — (m+n) импульсов. Синхрокод в параллельном коде считывается с выхода формирователя

l9 кода синхронизации на перный групповой вход блока 18 элементон KIN, с выхода которого он поступает на групповой вход преобразователя 20 кода и с частотой поступления тактовых импульсов на вход управления преобразователя 20 кода выдается на выход устройства н последовательном коде.

По заднему фронту импульса, поступающего на вход 2 блока 21 управления и соответствующего кадровому синхроимпульсу, на выходе 2 блока

21 управления устанавливается нулевой потенциал, запрещающий считывание синхронхода с выхода формирователя 19 кода синхронизации. Ро окончании считывания синхрокода с .выхода 8 блока 21 управления на пер" вый вход третьего счетчика l! поступает импульс. Под воздействием этого импульса третий счетчик 11 формирует адрес обращения к блоку памяти, работающему н режиме считывания. В рассматриваемом случае коммутатор 14 подключает групповой выход счетчика 11 к третьему групповому входу первого блока 16 памяти. Инструкция, считываемая из ячейки памяти блока 16 памяти, поступает через блок 18 элементов ИЛИ на групповой вход преобразователя 20 кода и считывается на выход устройства н последовательном коде с :астотой тактовых импульсов, поступающих на вход управления преобразователя 20 кода. Код адреса, формируемый третьим счетчиком 11, сравнивается но втором блоке 15 сранненияс кодом максимального адреса, поступающего с выхода третьего регистра 12. Сигнал результата сравнения (О н случае

"не равно и н случае равно ) фор. мируется на выходе блока 15 сравне!

О !

55 выхода 10 блока 21 управления несколько опережают импульсы с выхода

8, второй блок 15 сравнения сравнивает код максимального адреса с кодом адреса ячейки памяти, инструкция иэ которой была только что считана.

Это приводит к тому, что импульс совпадения кода максимального адреса с кодом текущего адреса формируется на ныходе блока 15 сравнения по окончании считывания всех инструкций о данном кадре из первого блока 16 памяти. Этот импульс обнуляет третий регистр 12 и, поступая на вход 1 блока 21 управления, запрещает ныдачу импульсов с выходов 8, 10, 1 блока

21 управления до поступления на вход устройства кадронога синхроимпульса очередного кадра. На этом цикл считывания инструкции о данном кадре изображения завершается.

Блок 21 управления работает следующим образом.

В исходном состоянии второй триг— гер 26, первый триггер 23, перный счетчик-делитель 27, второй счетчикделитель 31, третий счетчик-целитель

32 обнулены. Поступающий на вход 2 блока 21 управления импульс одновременно подается на первый вход второго триггера 26 и вход инвертора 24. По переднему фронту импульса, соответствующего кадровому синхроимп, второй триггер 26 переключается н единичное состояние . Един»»чвый» потенциал с его выхода подается на третий вход первого элемента И 28. Однако нулевой потенциал с выхода инвертора

24 продолжает удерживать перньп» элемент И 28 н закрытом" состоянии, препятствуя прохождению тактоных импульсов с выхода ГГИ 25 на. выход элемента И 28. Ро заднему фронту поступающего на вход 2 блока 21 управления импульса на вь хгдe инвертора 24 формируется единичный пете»»циал, который поступает на второй вход первого элемента И 28, разрешая прохождение через него тактовых импульсов. Эти импульсы поступают не вход первого счетчика-делителя 27, осуществляющего деление частоты входной последовательности Hà (m+n). »!вгтота импульсов на выходе первого счетчика-делителя 27 равна част-.те

l4

9471 ния по приходу нц его тактовь»й вход импульса с вь»хода 10 блока 21 управ" ления. За счет тс!го, что импульсы с

l5

16

1529471 обработки информации АЦП 1. Эти импульсы одновременно поступают на вход второго счетчика-делителя 31, выход 4 блока 21 управления, а такжечерез первый блок 30 задержки — на выходы 6, 3, 7 блока 21 управления.

При поступлении на вход 2 блока

21 управления импульсов, соответствуюших строчным синхроимпульсам, инвертор 24 формирует сигнал, блокирующий на время этих импульсов прохождение тактовых импульсов через элемент И 28. При этом на это же время прекращается выдача импульсов на выходы импульсов 6, 3, 7, 4 блока

2I управления.

После поступления на вход второго счетчика-делителя 31 И импульсов на его выходе формируется импульс, об- 20 нуляюший второй триггер 26. При этом нулевой потенциал с выхода триггера 26 блокирует прохождение импульсов через первый элемент И 28.

Импульс с выхода счетчика-делителя 25

31, задержанный во втором блоке 34 задержки, поступает на выходы 5,9 блока 21 управления, а также на вход третьего триггера 33 и одновибратора

22. При этом триггер 33 переключает- ЗО ся в противоположное состояние, обеспечивающее смену управляющих сигналов на выходах 12, 11 блока 21 управления, а однозибратор 22 формирует импульс, длителность которого равна времени считывания синхрокода на выход устройства, а задний фронт его совпадает с задним фронтом кадрового синхроимпульса поступающего на вход устройства ТВ-сигнала. Им- 40 пульс с выхода одновибратора 22 поступает на выход 2 блока 21 управления и одновременно — на соответствующий вход первого триггера 23, при этом триггер 23 переключается в единичное состояние.

Единичный потенциал с выхода первого триггера 23 подается на второй вход второго элемента И 29, разрешая прохождение через него тактовых им- 50 пульсов с выхода ГТИ 25. Импульсы с выхода элемента И 29 поступают на выход 1 блока 21 управления и одно1 временно на вход третьего счетчикаделителя 32. Этот счетчик-делитель осуществляет деление частоты входной последовательности импульсов на (тп+и)„

С выхода счетчика-делителя 32 импульсы поступают на выход 10 блока 21 управления и - через третий блок 35 задержки — на выход 8.

При поступлении импульса на вход блока 21 управления первый триггер

23 переключается в нулевое состояние, блокируя прохождение импульсов через второй элемент И 29, что ведет к прекращению выдачи импульсов на выходы 1, 10, 8 блока 21 управления.

Положительный эффект, который мот жет быть получен в случае использова; ния изобретения, состоит в том, что с повышением коэффициента сжатия ттропорционально сокращается объем памяти для хранения г рафических изображений и время их передачи по каналам связи.

Формула и з о б р е т е н и я

1. Устройство для сжатия цифровых телевизионных сигналов цветного изображения, содержащее анало-цифровой преобразователь (АПП), два блока сравпештя, блок установки опорного уровня, вход которого соединен с входом АЦП и является входсм устройства, а также блок управления (БУ), формирова TpJII кода сиихро..изации, первый блок з аде ржк и, выход которого со единен с первым входом БУ, первый блок памяти и преобразователь кода, о тл и ч а ю щ е е с я тем, что, с целью увеличения коэффициента сжатия, введены три регис.тра, три счетчика, элемент ИЛИ, элемент И, второй блок задержки, коммутатор, второй блок памяти и блок э Ivi снтов ИЛИ, групповой выход которого подключен к групповому входу преобразователя кода, тактовый вход которого подключен к первому выходу БУ, второй выход которого соепииен через формирователь кода синхронизации с первым групповым входoM блока э1телтетттов ИЛИ, второй гру. ттовотт вход к Jòсрого подклкчен к групповому вт ходу пе рвого блока памяти, а третий групт оной в:-.пр, блока эпементов ИЛИ соединен с групповымвыходом второго б;тока 1амяти, первый групповой вход первого б1тока памяти соединен с первым грунтовым входом второго блока памяти и подключен к групповому выходу первого блока задержки, группов и вход которого соепинен r групповым выходом первого регистр», первым групп вч 1 пхоттс". перВОГО 5JI(, ка cDаIAIID ии I tI с ГР у D Г1о вым

»2u,,, 10

35 входом. второго регистра, групповой вход первого регистра подключен к групповому выходу AIJIr, первый вход первого регистра подключен к третьему ныходу БУ, четвертый выход которого соединен с первым входом второго регистра, групповой выход которого подключен к второму групповому входу первого блока сравнения, пятый выход

БУ подключен к второму входу первого регистра и второму входу первого регистра, шестой выход БУ соединен с входом управления первого блока сравнения, выход которого подключен к первому входу элемента ИЛИ и к первому входу первого счетчика, второй вход которого подключен к седьмому выходу БУ, групповой выход первого счетчика соединен через элемент И с вторым входом элемента ИЛИ, а через второй блок задержки соединен с вторы ми групповыми входами первого и второго блоков памяти, выход элемента

ИЛИ соединен с первым входом второго счетчика, нос мой выход БУ подключен к первому входу третье.-о счетчика, второй вход которого соединен с вторым входом второго счетчика и пятым выходом БУ, групповой выход второго счетчика подключен к групповому входу третьего регистра и к первому групповому входу коммутатора, второй групповой вход которого подключен к групповому выходу третьего счетчика, и первому групповому входу второго блока сравнения, девятый выход БУ соединен с первым входом третьего регистра, десятый выход БУ подключен к тактовому входу второго блска срав ения, выход которого соединен с вторым входом третьего регистра, групповой выход которого подключен к второму групповому входу второго блока сравнения, перный вход коммутатора соединен с первым входом первого блока памяти и первым входом второго блока памяти и подключен к одиннадцатому выходу БУ, двенадцатый выход которого подключен к второму входу коммутатора, второму входу первого блока памяти и второму входу второго блока памяти, третий групповой вход первого блока памяти соединен с первым групповым выходом коммутатора, второй групповой выход которого подключен к третьему групповому входу второго блока памяти, второй вход блока управления

7 18 подключен к ныхсду блока установки опорного уровня,а выход греобрззонателя кода является выходом устройства.

2. Устройст: о т о и. 1, о т л и— ч а ю щ е е с я тем, что блок управления (БУ) содержит одновибратор, три триггера, инвертор, генератор тактовых импульсов (ГТИ), три счетчика-делителя, два элемента И, и три блока задержки, при этом вход управления первого триггера является первым входом БУ, информационный вход первого триггера соединен с выходом одновибратора, синхровход нторого триггера соединен с синхровходом иннертора и является нт:рым входом BY, выход ГГИ подключен к первым нходам первого и второго элемен-ов И, второй вход первого элемента И подключен к выходу иннертора, третий вход первого элемента И ссединен с ньгходом второго триггера, к второму входу второго элемента И подключен выход первого триггера, причем выход первого элемента И через первый счетчик-делитель соединен с входом первого блока задержки и входом второго счетчика-делителя, выход которого соединен с информационным входом второго триггера, а через второй блок задержки — с входом однонибратора и входом третьего триггера, выход второго элемента И через третий счетчик-делитель соединен с входом третьего блока задержки, при этом выход второго элемента И явль— ется первым выходом БУ, выход однонибратора является вторым выходом

Бу, первый выход первого блока задержки является третьим выходом БУ, выход первого счетчика-делителя является четвертым выходом БУ, второй выход второго блока задержки является пятым выходом БУ, второй выход первого блока задержки является шестым выходом БУ, третий н -цхсд первогоо блока задержки — седьмы нь ходом

БУ, выход третьего блока задержки восьмым выходом БУ, т ретий выхс д второго блока задержки — девятьм выходом БУ, выход третьего счетчикаделителя — десятым выходом БУ, пер— вый выход третьего триггера — одиннадцатым выходом БУ, а второй выход третьего триггера является двенадцатым выходом БУ.

1529471

3

0

Фиг. 2

Составитель О. Канатчикова

Редактор А. Маковская Техред A. Кравчук Корректор Э.!1онч.:<кова

Подписное

Тираж 626

Заказ 7763/57

ВНИИПИ Государственного комитета по изооретениям и открмгиям при I ÊÍT СССР

113035, Москва, Ж-35, Раушская наб., д. <, 5

Производ<..твенн< -издательский ком<»гнат "Патент", г. Укг< 1»;<, уч. Гагар«на, 101