Арифметико-логическое устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения арифметических и логических операций. Цель изобретения - повышение быстродействия устройства. Последнее содержит три группы регистров 1-3, арифметико-логический блок 4, коммутатор 5, группу элементов ИЛИ 6, распределитель тактовых сигналов 7, триггер 8. Операнды через группу информационных входов записываются в первую и вторую группы регистров. Одновременно значения операндов поступают на группу элементов ИЛИ для выявления количества значащих цифр. Количество значащих цифр операндов определяет реальное время выполнения арифметических операций в устройстве. Логические операции выполняются за один такт работы устройства. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„з0„, шуршя

А1 (50 4 G 06 F 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИ4ЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4301898/24-24 (22) 08.09.87 (46) 23. 12.89. Бюл. 1Ф 47 (72) Г.А. Викторов, Л.П. Коршунов, И.А. Лобанов, М.А.Чеперин и Л.Г. Коршунова (53) 681.3(088.8) (56) Авторское свидетельство СССР

1 711563, кл. G 06 F 7/00, 1978.

Дроздов E.À., Пятибратов А.П. Электронные вычислительные машины Единой

Системы.-M. Машиностроение, 1981, с. 199, рис.6.1. (54) АРИФИЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО (57) Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения арифметических и логических операций. Цель изобретения — повышение быстродействия устройства. Последнее содержит три группы регистров 1-3, арифметико-логический блок 4, коммутатор 5, группу элементов ИЛИ 6, распределитель тактовых сигналов 7, триггер 8. Операнды через группу информационных входов записываются в первую и вторую группы регистров. Одновременно значения операндов поступают на группу элементов

ИЛИ для выявления количества значащих цифр. Количество значащих цифр операндов определяют реальное время выполнения арифметических операций в устройстве. Логические операции выполняются за один такт работы устройства. 3 ип.

1531086

Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения арифметических и логических операций в процессорах

ЭБМ и устройствах автоматики.

Целью изобретения является повышение быстродействия устройства.

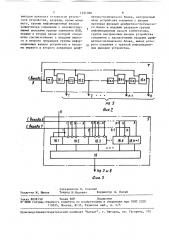

На фиг. 1 представлена структурная схема арифметико-логического уст- 10 ройства; на фиг. 2 — функциональная схема генератора тактовых импульсов; на фиг. 3 — функциональная схема коммутатора.

Арифметико-логическое устройство 15 (фиг. 1) содержит три группы регистров 1-3, арифметико-логический блок

4, коммутатор 5, группу элементов

ИЛИ 6, распределитель 7 тактовых сигналов, триггер 8, группу информацион- 20 ных входов 9, группу настроечных входов 10, настроечный вход 11, два управляющих входа 12 и 13, вход 14 запуска, выход 15 признака готовности результата. 25

Распределитель 7 тактовых сигналов (фиг. 2) содержит группу элементов

И 1b.1-16.k и группу элементов задержки 17.1-17.k (где k - число од- новременно анализируемых Групп one- 30 ранда) .

Коммут ат ор 5 (фиг . 3) содержит группу элементов И 18 . 1-1 8. k+ 1 и элемент ИЛИ 19.

Устройство работает следующим об- 35 разом.

Под управлением сигнала с первого 12 и второго 13 управляющих входов в первую и вторую группу регистров 2 и 1 соответственно записывают- 40 ся значения операндов с группы информационных входов 9, после чего под управлением сигнала с входа 14 запуска на прямом выходе триггера 8 формируется сигнал единичного уров- 45 ня, разрешающий запуск распределителя 7 тактовых сигналов, одновременно с этим на инверсном выходе триггера 8 формируется сигнал низкого уровня (признак занятости устрОйства).

Оба операнда с выходов первой 2 и второй 1 группы регистров поступают соответственно на входы первого и второго операндов арифметико-логического блока 4, на группу настроечных входов 10 которого подается код настройки, определяющий тип выполняемой операции, а на настроечный вход 11

I поступает сигнал, определяющий арифметическая или логическая операция выполняется устройством. Одновременно с этим на первые и вторые входы группы элементов ИЛИ 6 с выходов первой 2 и второй 1 группы регистров поступают значения операндов для определения старшей значащей цифры. Количество значащих цифр операндов определяет время выполнения арифмети . ческих операций в устройстве посредством формирования сигнала единичного уровня на выходе коммутатора 5.

Единичный сигнал на выходе коммутатора 5 разрешает запись результата вычисления с выхода арифметико-логического блока 4 на третью группу регистров 3 и блокирует формирование тактовых сигналов с выхода распределителя, одновременно с этим на инверсном выходе триггера 8 формируется сигнал признака готовности результата. Блокировка тактовых сигналов осуществляется посредством подачи сигнала единичного уровня с выхода коммутатора

5 на вход сброса триггера 8. Величина квантования выходных сигналов распределителя 7 тактовых сигналов выбирается в зависимости от выбора конкретного арифметико-логического блока 4 и числа одновременно анализируеылх групп входной информации на .руппе элементов ИЛИ 6.

При выполнении логических операнд единичный сигнал на выходе коммутатора 5 формируется под управлением первого сигнала с выхода распределителя 7 тактовых сигналов.

Таким образом, формирование результата на выходе устройства осуществляется за реальное время выполнения операции в арифметико-логическом блоке 4.

Формула изобретения

Арифметико-логическое устройство, содержащее арифметико-логический блок, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, онс содержит группу элементов ИЛИ, коммутатор, распределитель тактовых сигналов к триггер, причем вход запуска устройства соединен с тактовым входом триггера, прямой выход которого соединен с входом распределителя тактовых сигналов, выходы которого соединены с соответствующими управляющими входами коммутатора, выход которого соединен с входом сброса триггера, инверсный выход которого является

1531086

На 5

Фиг. Я

- Составитель В. Сорокин

Редактор И. Шулла Техред М.Ходанич Корректор Л. Патай

Заказ 8028/50 Тираж 668 Подписное

В ИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 выходом признака готовности результата устройства, разряды, кроме младшего, группы информационных входов коммутатора соединены с соответствующими выходами группы элементов ИЛИ, первые и вторые входы которой соединены соответственно с входами первого и второго операндов группы информационных входов устройства и входами первого и второго операндов арифметико-логического блока, настроечный вход устройства соединен с входом признака функций арифметико-логическо5

ro блока и младшим разрядом группы информационных входов коммутатора, группа настроечных входов устройства соединена с настроечными входами арифметика-логического блока, выход которого соединен с группой информационных выходов устройства.