Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и специализированных вычислительных устройствах. Цель изобретения - расширение функциональных возможностей за счет реализации операции извлечения корня из чисел, представленных в форме с плавающей запятой. В устройство, содержащее блоки памяти логарифма и экспоненты, сумматор и блок сдвига, введен нормализатор с соответствующим межэлементным подключением. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (111 (50 4 G 06 Р 7/552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMV СВИДЕТЕЛЬСТВУ п = 2"; k = 1,2,3....

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4394240/24-24 (22) 17.03.88 (46) 23.12.89. Бюл. № 47 (71) Ереванский политехнический институт им. К. Маркса (72) К.Ж. Цатрян и Г.Ж. Цатурян (53) 681.325(088. 8) (56) Ъузунов 10.À и Вавилов Е.Н. Принципы построения цифровых вычислительных машин. — Киев: Техника, 1972, с. 267.

Авторское свидетельство СССР

М 898424, кл. С 06 Е 7/52, 1980.

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и специализированных вычислительных устройствах.

Цель изобретения — расширение функциональных возможностей за счет реализации операции извлечения корня из чисел, представленных в форме с плавающей запятой.

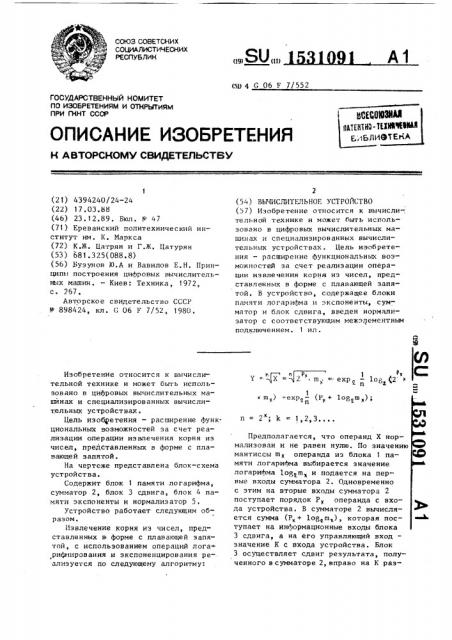

На чертеже представлена блок-схема устройства.

Содержит блок 1 памяти логарифма, сумматор 2, блок 3 сдвига, блок 4 памяти экспоненты и нормализатор 5.

Устройство работает следующим образом.

Извлечение корня из чисел, представленных в форме с плавающей запятой, с использованием операций лога рифмирования и экспоненцирования реализуется по следующему алгоритму:

2 (54) ВЪ|ЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к вычисли-, тельной технике и может быть исгользовано в цифровых вычислительных машинах и специализированных вычислительных устройствах. Цель изобретения — расширение функциональных воэможностей за счет реализации операции извлечения корня из чисел, представленных в форме с плавающей запятой, В устройство, содержащее блоки памяти логарифма и экспоненты, сумматор и блок сдвига, введен нормялизатор с соответствующим межэ уементным подключением. 1 ил . л(и Р„ 1 х

Y = Х = 2.".m -ехр — 1о8 (2 х

« 2п й

МЮ

«m «) =ехр 1 — (Р + 1og m >,); и х

Предполагается, что операнд Х нормализован и не равен нулю. По значению мантиссы m операнда из блока 1 па- CO мяти логарифма выбирается значение логарифма 1ор т„ и подается на первые входы сумматора 2. Одновременно с этим на вторые входы сумматора 2 поступает порядок Р« операнда с входа устройства. В сумматоре 2 вычисляется сумма (Р„ + 1оя,т„), которая поступает на информационные входы блока

3 сдвига, а на его управляющий вход— значение К с входа устройства. Блок

3 осуществляет сдвиг результата, полученного в сумматоре 2, вправо на К pas1531091

Формула изобре те ния

Составитель К. Иатрян

Техред И.Ходанич Корректор A ° Обручар

Редактор И. Шулла

Заказ 8028/50 Тираж 668 Подписное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственио-издательский комбинат "Патент", r Ужгород, ул. Гагарина, 101 рядов, т.е. на выходах блока 3 сдвига получается значение 2 (Р„+ log тп„).

Затем по этому значению из блока 4 памяти экспоненты выбирается значение

-Ц 5 экспоненты ехр<2 (Р + 1оя,м ) и подается на вход нормализатора 5. В нормализаторе 5 полученное значение нормализуется, т.е. на выходах младших разрядов получается нормализованная мантисса и подается на выходы мантиссы результата устройства, а на выходах старших разрядов — порядок и подается на выход порядка результата устройства. 15

Вычислительное устройство, содержащее блок памяти логарифма, сумматор,20 блок сдвига и блок памяти экспоненты, причем первый информационный вход устройства соединен с входом блока памяти логарифма, выход которого подключен к первому входу сумматора, о т— л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет реализации операции извлечения корня из чисел, представленных в форме с плавающей запятой, оно содержит нормапизатор, причем второй информационный вход устройства соединен с вторым входом сумматора, выход которого соединен с информационным входом блока сдвига, управляющий-.вксд которого подключен к управляющему входу устройства, выход блока сдвига соединен с входом блока памяти экспоненты, выход которого подключен к входу нормализатора, выходы старших и младших разрядов которого яв,-яются соответственно выходом порядка и мантиссы результата.