Устройство приоритетного обслуживания

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах коммутации, связи, вычислительных машинах для организации приоритетного обслуживания и приоритетных очередей заявок. Цель изобретения - повышение быстродействия устройства. Устройство приоритетного обслуживания содержит блок памяти, генератор импульсов, две группы элементов И, группу элементов ИЛИ, схемы сравнения, элемент ИЛИ, элемент И. Устройство позволяет производить параллельное сравнение кодов приоритета заявок, находящихся в очереди в блоке памяти, с кодом приоритета вновь пришедшей заявки. Параллельное сравнение кодов приоритета существенно повышает скорость формирования очереди запросов и, следовательно, работы устройства в целом. 2 ил.

СО(ОЭ CORETCHVlX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) А1 (594 06 Р 9 46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ (21) 4146678/24-24 (22) 10. 11. 86 (46) 23.12 ° 89. Бюл. № 47 (72) В.П. Улитенко, Г.Н. Тимонькин, С.Н. Ткаченко, В.С, Харченко, Е.В. Пугач и Д.В. Дмитров (53) 681.325(088.8) (56) Авторское свидетельство СССР

¹ 1141410, кл. G 06 F 9/46, 1983.

Авторское свидетельство СССР № 1348834, .кл. (06 Е 9/46, 05. 06. 86. (54) УСТРОЙСТВО ПРИОРИТЕТНОГО ОБСЛУ)КИВАНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано в системах коммутации, связи, Изобретение относится к вычислительной технике и может быть использовано в системах коммутации, связи, в вычислительных машинах для органиэации приоритетного обслуживания и приоритетных очередей заявок.

Цель изобретения — повышение быстродействия устройства.

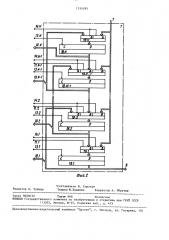

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 функциональная схема блока памяти.

Устройство приоритетного обслуживания содержит блок 1 памяти, схемы

2.1-2.N сравнения, элемент ИЛИ 3, элемент И 4, первый 5.1 и второй 5.2 выходы синхронизации, генератор 6 импульсов, информационный вход 7, сигнальный вход 8, выход 9 устройства, кодовые выходы 10.1-10.N блока 1 павычислительных машинах для организации приоритетного обслуживания и приоритетных очередей заявок. Цель изобретения — повышение быстродействия устройства. Устройство приоритетного обслуживания содержит блок памяти, генератор импульсов, две группы элементов И, группу элементов ИЛИ, схемы сравнения, элемент ИЛИ, элемент И.

Устройство позволяет производить параллельное сравнение кодов приоритета заявок, находящихся в очереди в блоке памяти, с кодом приоритета вновь пришедшей заявки. Параллельное сравнение кодов приоритета существенно повышает скорость формирования очереди запроЯ сов и, следовательно, работы устройства в целом, 2 ил. мяти, выходы 11.1-11 N и 12.1-12.N схем 2.1-2.N сравнения соответственно, входы 13.1-13.N синхронизации и адресные входы 14.1- 14.N блока 1 памяти, группу элементов ИЛИ 15.1-15.N группы элементов И 16.2-16.N и 17.117 ° N.

Блок 1 памяти (фиг. 2) содержит регистры 18. 1-18.N и коммутаторы

19. 1 — 19. N.

Устпойство работает следующим образом.

В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии (цепи установки исходного состояния не показаны).

Код заявки и код ее приоритета поступают на информационный вход 7

1531095 устройства. В результате этого на вы.ходе элемента ИЛИ 3 появляется единичный сигнал. Кроме того, код приоритета заявки поступает на входы В схем 2. 1-2. N сравнения, на Входы А которых поступают коды приоритетов заявок, хранящихся в блоке 1 памяти.

Сигналы сравнения поступают в блок

1 памяти.

Сигнал с выхода элемента ИПИ 3 открывает элемент И 4, и сигнал с первого выхода генератора 6 поступает в устройство. Поступая в устройство, сигнал с выхода элемента И 4 синхронизирует запись вновь пришедшей заявки, код которой поступает на информационный вход блока 1 памяти, в соответствии с сигналами с выходов схем

2.1-2. N сравнения.

Вновь пришедшая заявка ставится в очередь за заявками, приоритеты которых выше приоритета данной заявки и последней среди заявок равного с ней приоритета. 25

Заявка, стоящая первой в очереди, обслуживается обслуживающим органом.

После того, как последний выполнил заявку, он дает сигнал на вход 8.

Этот сигнал проходит через элементы

ИЛИ 15. 1-15.N и производит сдвиг заявок в блоке 1. В результате этого самая приоритетная заявка из регистра 18. 1 поступает в обслуживающее устройство, заявка из регистра 18.2 переписывается в регистр 18.1 и

35 т,д, Рассмотрим запись в очередь вновь поступившей заявки. Код заявки поступает с входа 7 на соответствующие

40 входы коммутаторов 19.1-19.N. Допустим, что при сравнении кодов приоритетов схемы 2.1-2.i=1 сравнения выдали сигналы на соответствующих выходах 11.1-11.i-1, а схемы 2.i-2.N срав"45 нения выдали сигналы на выходах 12.i12.N Это означает, что в соответствующих регистрах 18.1-18.i-I хранятся заявки, приоритеты у которых выше, чем приоритет у вновь пришедшей эаяв50 ки, а в регистрах 18.i-18.N хранятся заявки, приоритеты которых ниже приоритета вновь пришедшей заявки.

Таким образом, необходимо в регист рах 18.1-18.i-1 информацию не иэме55 нять, заявку, хранящуюся в регистре

18.i, переписать в регистр 18.i+1, заявку иэ регистра 18.i+1 переписать в ре гистр 18. i+2 и т.д., а в регистр

18.i записать заявку, поступившую на вход 7. Происходит это следующим образом.

В регистрах 18.1-18.i-1 информация не изменится потому, что соответствующие элементы И 17.1-17.i-1 закрыты нулевыми сигналами с выходов

12. 1-12. i-1 схем 2. 1-2. i-1 сравнения соответственно. В связи с этим сигнал с выхода элемента И 4 не пройдет на входы 13.1-13.i соответствующих регистров 18. i-18. i-1.

Коммутаторы 19. i+1 — 19.N открыты для информации от регистров 18. i18.N-t с порядковым номером на единицу меньше соответствующими нулевыми сигналами с выходов элементов И

16.i+1 16.N. Элементы И 17. i+1-17.N также открыты сигналами с выходов

12.i+1-12.N. Поэтому сигнал с выхода элемента И 4, пройдя через элементы

И 17.i+1 — 17.N и ИЛИ 15.i+1-15.N, поступит на входи 13.i+1-13.N и произведет перезапись информации из регистра 18 в регистр 18 с порядковым номером на единицу больше.

Элемент И 16.i буде открыт, так как схема 2.i.-1 сравнения выдала сигнал на выходе 11.i-1, а схема 2.i сравнения на выходе 12.i. Поэтому коммутатор 19.i будет открыт для информации, поступающей по входу 7.

Элемент И 17.i будет также открыт соответствующим сигналом с выхода 12.i схемы 2.i сравнения. Поэтому по заднему фронту сигнала с выхода элемента И 4 в регистр 18.i запишется заявка, код которой поступает по входу 7.

Когда очередная заявка, находящаяся в регистре 18. 1, выполнена, то по входу 8 поступает сигнал, который через элементы ИЛИ 15.1-15.N поступает на С-входи всех регистров 18. 1-18.N.B этот момент времени на информационном входе .7 должна быть нулевая информация. Тогда все схемы 2.1-2.N сравнения выдают сигналы на выходах

11.1 — 11.N, Поэтому коммутаторы 19. 119.N-1 открыты для информации от регистров с порядковым номером на единицу больше. Следовательно, произойдет сдвиг информации; в регистр

18.1 перепишется заявка из регистра

18.2, в регистр 18.2 — из регистра

18.3 и т.д.

Импульсы с выхода генератора 6, поступая на выход 5.1 устройства, Сигнал на входе 8 появляется в паузах между импульсами с выхода 5.1 генератора 6. Для синхронизации (вре10 менной привязки) поступления этого сигнала генератор б формирует импульсы на выходе 5.2, которые сдвинуты по фазе относительно импульсов, выдаваемых на выходе 5. 1.

Устройство приоритетного обслуживания, содержащее блок памяти, гене- 2О ратор импульсов, элемент ИЛИ, элемент И, группу элементов ИЛИ, первую группу элементов И и первую схему сравнения, причем информационный вход устройства соединен с входом элемента ИЛИ, первым входом первой схемы сравнения и информационным входом блока памяти, выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, сигнальный вход устройства соединен с первыми входа5 I531 синхронизируют поступле ние кодов заявок на вход 7 и сигналов на вход ,8. Заявка, поступающая на вход 7, поступает по заднему фронту следующего за ним импульса.

° 5

Формула изобретения

095 6 ми элементов ИЛИ группы, выходы которых соединены с группой входов записи блока памяти, выходы элементов И первой группы соединены с вторыми входами соответствукщих элементов ИЛИ груп" пы, первый выход блока памяти является выходом устройства, о т л и ч аю щ е е с я тем, что, с целью повышения быстродействия, устройство содержит (N-1)-ю схему сравнения (N — длина очереди заданий) и вторую группу элементов И, выходы которых соединены с группой адресных входов блока памяти, информационный вход устройст" ва соединен с первыми входами схем сравнения с второй по N-ю, i-й выход блока памяти (i=1,N) соединен с вторым входом i-й схемы сравнения, выход "Меньше" которой соединен с первым входом i-го элемента И первой группы, вторые входы которых соединены с выходом элемента И, выход "Меньгае" первой схемы сравнения соединен с адресным входом блока памяти, выход "Больше j A cx r сравнения (j

1, N-1) соединен с первым входом

j-ro элемента И второй группы и j-м входом сдвига группы входов сдвига блока памяти, выход "Меньше" (j+1)-й схемы сравнения соединен с вторым входом j-го элемента И второй группы.

1531095

Составитель M. Сорочан

Техред М.Ходанич Корректор А. Обручар

Редактор Н. Тупица

Заказ 80028/50 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101