Матричный накопитель для постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к интегральным схемам электрически репрограммируемых постоянных запоминающих устройств. Цель изобретения - повышение быстродействия накопителя. Для этого накопитель содержит первые транзисторы 12, 13 предзаряда, вторые транзисторы 14, 15 предзаряда, адресные транзисторы 18, 19, транзисторы 16, 17 стирания с соответствующими связями. В режиме стирание информации высоковольтное напряжение подается на вход 30 стирания. Это напряжение передается одним из транзисторов 16, 17 в нужную секцию накопителя, а одним из транзисторов 18, 19 и транзисторами 6, 7 выборки слов - на электроды стирания (вторые обкладки конденсаторов 2) выбранных элементов 1 памяти. В результате стирание информации может быть произведено с использованием только одной специальной шины на кажду строку. Уменьшение количества шин снижает паразитные емкости накопителя и, следовательно, повышает его быстродействие. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБ/1ИК

„„SU„„1531169 A i дц 4 С 11 С 17/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

2 накопитель содержит первые транзисторы 12, 13 предзаряда, вторые транзисторы !4, 15 предзаряца, адресные транзисторы 18, 19, транзисторы 16, 17 стирания с соответствующими связями. В режиме стирания информации высоковольтное напряжение подается на вход

30 стирания. Это напряжение передается одним из гранзисгоров 16, 17 в нужную секцию накопигеля, а одним из гранзисгоров 18, 19 и гранзис горами 6, 7 выборки слов на элекгролы сгирания (вгорые обкладки конденса горов 2) выбранных элементов 1 памяти. В результате стирание информации может быть произведено с использованием только одной (21) 4359097/24-24 (22) 06,01.88 (46) 23.12.89. Бюл. У 47 (72) Н.И.Хцынский, В.А.Ярандин, В.П.Сидоренко и А.М.Прокопенко (53) 681.327.6(088.8) (56) Патент США М 4375085, кл. С 11 С 11/40, опублик. 1983.

Патент ЕПВ Ф 0088815, кл. G 11 С 17/00, опублик. 1983. (54) МАТРИЧНЫЙ НАКОПИТЕЛЬ ДПЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА (57) Изобретение относится к вычислительной технике, а именно к интегральным схемам электрически репрограммируемых постоянных запоминающих устройств. Цель изобретения — повышение быстродействия накопителя. Для этого 1(специальной шины на каждую строку.

Уменьшение количества шин снижает паразистные емкости накопителя и, следовательно, повышает его быстродействие. 2 ил.

/Я

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1531169

Изобретение относится к вычислительной технике, а именно к интегральным схемам электрически репрограммируемых постоянных запоминающих уст1 ройств.

Целью изобретения является повьппение быстродействия накопителя.

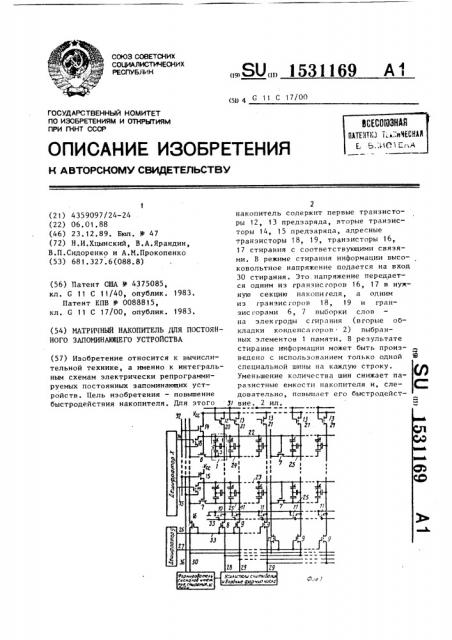

На фиг, 1 представлена электрическая схема накопителя на фиг. 2 — вре-10 менная диаграмма его работы.

Матричный накопитель содержит элементы 1 памяти, состоящие из трех конденсаторов 2-4, первые обкладки

5 которых объединены, транзисторы Ь и 7 выборки слов, транзисторы 8 и 9 выборки разрядов,разрядные транзисторы 10 и 11, первая группа транзисторов 12 и 13 предзаряда, вторая группа транзисторов 14 и 15 предзаряда, транзисторы 16 и 17 стирания, адресные транзисторы 18 и 19, разрядные шины 20 и 21, первые адресные шины 22 и 23, вторые адресные шины 24 и 25, входы 26 и 27 выборки разрядов, вхо- 25 ды-выходы 28 и 29, вход 30 стирания, три входа 31-33 синхронизации, входы

34 и 35 выборки слов, вход 36 записи-считывания.

Конструктивно элемент 1 памяти представляет собой МЛП-транзистор с плавающим затвором. Конденсатор 2 образован его плавающим и управляющим затворами, конденсатор 3 — туннельной областью и плавающим затвором, конденсатор 4 — областью истока и плавающим затвором. Объединенные первые обкладки 5 конденсаторов 2-4 являются плавающим затвором МДП-транзистора. 40

Предлагаемый матричный накопитель работает следующим образом.

При считывании в момент времени

t„ на входы 31 и 32 подаются импульсы напряжения, в течение которых до 45 момента времени с происходит заряд разрядных шин 20 и 21 и первых адресных шин 22 и 23. При этом на первых обкладках 5 элементов 1 памяти наводится за счет емкости конденсатора 3 перепад напряжения положительной полярности. Величина этого перепада зависит от знака заряда, хранимого на первых обкладках 5. Если хранится положительный заряд, то при подаче на адресные и разрядные шины 20-23 напряжения положительной полярности величина наведенного перепада потенциала на обкладках 5 значительно больше аналогичной величины в случае хране-г ния на обкладках 5 огрицательного заряда. В момент t на вход 36 подается отрицательный перепад напряжения от уровня питания, который чер:.з адресный транзистор 18 при возбуждении его по выбранному входу 34 передается на первую адресную шину 22.

Если на обкладках 5 хранится положительный заряд, то отрицательный перепад напряжения передается на разрядную шину 20. Если на обкладках 5 хранится отрицательный заряд, то отрицательный перепад напряжения с первой адресной шины 22 практически не передается на разрядную шину 20. Далее считанный сигнал с шины 20 через транзистор 8, управляемый по входу 26, передается на вход-выход 28 накопителя. После окончания действия импульса отрицательной полярности в момент времени с через транзисторы 10 и 11 производится разряд шин 20 и 21 при подаче импульса по входу 23 для подготовки следующего акта считывания.

В момент вермени t оканчивается действие импульса на входе 33.

Интервалы времени t6 t и t7-t8 относятся к случаям полувыборки элемента 1 по входам 26 и 34 соответственно. Интервал времени t y св относится к случаю невыбора элемента

1, В режиме стирания в момент времени с происходит подача сигналов вы4 борки на входы 26 и 34 (высоковольтные сигналы), а также высоковольтных сигналов на вход 36 и через транзистор 18 на выбранную шину 22. В момент времени с на входе 30 стирания формируется высоковольтное напряжение, которое через открытые транзисторы 16 и 6 (шина 22 при этом уже заряжена через транзистор IS) передается на шину 24. Одновременно с этим на разрядных шинах 20 и 21 первой секции формируется нулевой потенциал.

При этом высокое напряжение стирания прикладывается к конденсатору 2 выбранных элементов 1 памяти.

Во всех выбранных элементах 1 памяти эа счет туннельного пробоя конденсатора 2 происходит накопление положительного заряда на обкладках 5, т.е. высокого логического уровня ("1"). В момент времени г оканчивается. действие высоковольтного сигнала стирания, а в момент t4 произво дится отключение выбранных элементов

5 153116

1 памяти. В течение интервала времени С -t 4 происходит разряд шины 24 на вход 30 находящийся под нулевым потенциалом, а шины 22 на вход 36, также находящийся в это время под нулевым потенциалом. Начиная с момента времени t до момента времени происходит повторение цикла стирания, в теченйе которого элемент 1 памяти и другие элементы 1 данной секции накопителя оказываются полувыбранными по входу 34, а в течение интервала времени t>-t< они полуныбраны по входу 26, В течение укаэанных интервалов времени не происходит изменение состояния элементов 1 памяти.

После момента времени с, указанные элементы 1 находятся в невыбранном состоянии.

После окончания действия импульса записи в момент с происходит разряд разрядных шин 20 и 21 и второй адресной шины 22 через транзисторы 8 на входы-выходы 28 и 29 и вход 36. В момент времени с прекращается дейстФ ние сигналов выборки на входах 26 и

34, В течение интервалов времени t6-t> и t -t> происходит полувыборка тех же элементов 1 памяти по входам 26 и

34 соответственно, а после момента времени t элементы 1 оказываются в невыбранном состоянии. В течение всего -процесса записи на входе 30 поддерживается низкий потенциал, В полувыбранном и неныбранном состоянии в процессе записи не создаются условия для изменения информационного заряда элементов 1 памяти.

Матричный накопитель для постоянного запоминающего устройства, содержащий секции памяти, каждая из которых состоит из элементов памяти, выполненных на трех конденсаторах, первые обкладки которых объединены, а вторые подключены соответственно к первым и вторым адресным шинам и к разрядным шинам накопителя, транзисторы выборки слов, истоки которых подключены к соответствующим нгорым адресным шинам накопителя, затворы — к соответствующим первым адресным шинам накопителя,исгоки транзисторов выборки слов каждой секции памяти накопителя объединены, соответствующие первые адресные шины всех секций памяти накопителя объединены, транзисторы выборки разрядов, стоки которых подключены к соответствующим разрядным шинам накопителя, затворы транзисторов выборки разрядов каждой секции памяти объединены и являются соответствующими входами выборки разрядов накопителя, истоки соответствующих транзисторов выборки разрядон нсех секций памяти объединены и янляются входами-выходами накопителя, разрядные транизсторы, истоки которых подключены к соответствующим разрядным шинам накопителя, отличающий с я тем, что, с целью повьпления быстродействия накопителя, он содержит первую группу транзсторов предзаряда, вторую группу транзисторов предзаряда, адресные транзисторы, а в каждой сек40

В режиме записи в момент времени происходит формирование адресных сигналов выборки на входах 26 и 34.

В момент времени с на вход 36 подают"25 ся импульсы положительной полярности, а на входы-выходы 28 и 29 — высоковольтные сигналы записи (если необходимо произвести запись низкого логического уровня (вОв) в данный 30 элемент 1 памяти) или нулевые потенциалы (если необходимо оставить элемент 1 в состоянии высокого логического уровня ("1")). Эти сигналы передаются через транзсторы 8 и 9, открытые по входу 26, на разрядные шины 20 и 21 первой секции. В течение интервала времени t -tz происходит разряд шин 20, 22 и 24 до нулевого потенциала, заряженных в процессе предыдущих обращений к накопителю.

В момент времени t на вход 36 пода2 ется высокое напряжение, которое передается через транзистор 18 на шину 12. Сигнал записи на разрядных ши- 45 нах 20 и 21 тех разрядов, где необходимо произвести запись логического уровня "0", передается на обкладки

5. Для элемента 1 невыбранных строк; связанных с выбранной разрядной ши- 50 ной 20, 21 (столбцом), на соответствующих первых адресных шинах 22 и 23 ранее установлен нулевой потенциал.

Для этих элементов 1 на обкладки 5 передается с второй обкладки конденса- 55 тора 4 значительно меньшее напряжение. При этом в невыбранных элементах

1 памяти сохраняется существовавший ранее информационный заряд, формул а изобретения

1» 31169

78 44 tt 4г М44Ю te t г 1з t tq t>tf

y)оатыбание (б)СлшРоиие 2 Юаню °

Составитель С. Королев

Редактор ?!. Бланар Техред Л,Олийнык Корректор M.Øàðîøè

Заказ 7963/54 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 ции памяти транзистор стирания, сток которого соединен со стоками транзисторов выборки слов этой секции памяти, затвор соединен с затворами транзисторов-выборки разрядов этой секции памяти, а истоки транэисгоров стирания всех секций памяти объединены и являются входом стирания накопителя, стоки транзисторов предзаряда первой и второй групп подключены к шине питания накопителя, затворы транзисторов предзаряда первой группы объединены и являются первым входом синхронизации накопителя, а истоки подключены к соответствующим разрядным шинам накопителя, затворы транэисторов предзаряда второй группы объединены и являются вторым входом синхронизации накопителя, а истоки соединены со стоками соответствующих адресных транзисторов и подключены к соответствующим первым адресным шинам, затворы адресных гранэисгоров являются входами выборки слов накопителя, а истоки объединены и являются входом записи-считывания накопителя, затворы транзисторов разряда объединены и являются третьим входом синхронизации накопителя, а истоки подключены к шине нулевого потенциала накопителя.