Устройство для контроля аналого-цифровых преобразователей

Иллюстрации

Показать всеРеферат

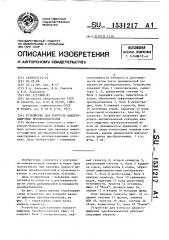

Изобретение относится к контрольно-измерительной технике и может быть использовано при проверке аналого-цифровых преобразователей в производственных и эксплуатационных условиях. Цель изобретения - повышение оперативности контроля и достоверности путем учета динамической погрешности преобразователя. Устройство содержит блок 1 синхронизации, селекторы 2,3, реверсивный счетчик 4, блок 5 задержки кодов, вычитатель 6 кодов, образцовый цифроаналоговый преобразователь 7, блок 8 регистрации, блок 9 анализа годности, блок 10 сравнения кодов, задатчик 11 кода допустимой погрешности, триггер 12 останова. Устройство позволяет проводить автоматический контроль аналого-цифровых преобразователей во всем их динамическом диапазоне с периодом смены контрольных кодовых комбинаций, равным минимальной длительности цикла преобразования. 1 з.п.ф-лы, 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН!

5п4 Н 03 М 1 10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А STOPCHOMY СВИДЕТЕЛЬСТВУ

2 оперативности контроля и достоверности путем учета динамической погрешности преобразователя. Устройство содержит блок 1 синхронизации, селекторы 2, 3, реверсивный счетчик 4, блок 5 задержки кодов, вычитатель 6 кодов, образ цовый цифроанало говый преобразователь 7, блок 8 регистрации, блок 9 анализа годности, блок

I0 сравнения кодов, эадатчик 11 кода допустимой погрешности, триггер 12 останова. Устройство позволяет прородить автоматический контроль аналого-цифровых преобразователей во всем их динамическом диапазоне с периодом смены контрольньж кодовых ком" бинаций, равным минимальной длительности цикла преобразования ° 1 з.п. флы, 2 ил.

Вааб вый селектор 2, второй селектор 3, СуФ реверсивный счетчик 4, блок 5 задержки кодов, вычитатель 6 кодов, образцовый цифроаналоговый преобразователь 7, блок 8 регистрации, блок. 9 Ьа) анализа годности, блок 10 сравнения кодов, эадатчик 11 кода допустимой погрешности, триггер 12 останова, шину 13 "Пуск", входную шину 14, первую 15 и вторую 16 выходные шины.

Блок анализа годности (фиг. 2) содержит счетчик 17 циклов, элемент

ИЛИ 18, триггер 19 сбоя, счетчик 20 сбоев, коммутатор 21, шину 22 Режим".

Устройство для контроля аналогоцифровых преобразователей работает следующим образом.

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4030553/24-24 (22) 03.03.86 (46) 23,12.89. Бюл. Н 47 (72) Е.А ° Банченко, В.В. Смирнов и 3.3. Зурканаев (53) 68 1 . 325 (088 .8) (56) Авторское свидетельство СССР

У 1042459, кл. С 01 R 35/00, 1982.

Авторское свидетельство СССР

У 399059, кл. Н 03 M 1/10, 1971.

I (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АНАЛОГОЦИФРОВЪ|Х ПРЕОБРАЗОВАТЕЛЕЙ (57) Изобретение относится к контрольно-измерительной технике и может быть использовано при проверке аналого-цифровых преобразователей в производственных и эксплуатационных условиях. Цель иэобретения — повьппение

Изобретение относится к контрольно-измерительной технике и может быть использовано при проверке аналого-цифровых преобразователей в производственных и эксплуатационных условиях.

Цель изобретения — повьппение оперативности контроля и достоверности путем учета динамической погрешности преобразователя.

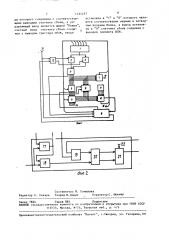

На фиг ° 1 представлена структурная схема устройства для контроля аналого-цифровьж преобразователей; на фиг. 2 — структурная схема блока анализа годности.

Устройство для контроля аналогоцифровых преобразователей (фиг. !) содержит блок I синхронизации, пер„„SU„„1531217 А1

1531217

10 l5

Перед началом работы выходные шины 15 и 16 соединяют соответственно с аналоговым и тактовым входами поверяемого АЦП, а его кодовые выходы соединяют с входной шиной 14. Блок

1 синхронизации вырабатывает все необходимые для работы остальных блоков устройства последовательности синхроимпульсов, а также счетные импульсы, поступающие через первый 2 и второй 3 селекторы соответственно на суммирующий и вычитающий входы реверсивного счетчика 4. Первый селектор 2 открывается и пропускает счетные импульсы по импульсу запуска, поступающему с шины 13 Пуски и устанавливающему триггер 12 останова в единичное состояние ° N-разрядный натуральный двоичный код линейно нарастающего сигнала, снимаемый с

1 выходов реверсивного счетчика 4, по дается на образцовый цифроаналоговый преобразователь 7, где преобразуется ,в линейно нарастающее ступенями, соответствующими единице младшего разряда, напряжение, равное для каждой кодовой комбинации U =р (N-1/2), и

И-1 где 1

I код, в общем случае не равный коду на выходах реверсивного счетчика 4.

Модуль разности зти:; кодов, образуемый на выходе вычитателя 6 кодов, сравнивается в блоке 10 сравнения кодов с кодом допустимой погрешности преобразования, поступающим с задатчика 11 кода допустимой погрешности.

В случае выхода разницы за пределы установленного допуска на выходе блока 10 сравнения кодов образуется единичный сигнал, устанавливающий триггер 19 сбоя в еиничное состояние. Следующий синхроимпульс с седьмого выхода блока 1 синхронизации, поданный на вход обнуления триггера

19 сбоя, сбрасывает его в нулевое состояние и тем самым записывает "1 в первый разряд счетчика 20 сбоев, фиксируя единичный сбой в одной из точек динамического диапазона поверяемого аналого-цифрового преобразователя ° Блок 5 задержки кодов, выполненный, например, на регистрах, вводит задержку на столько тактов, на сколько задерживается сигнал при про25

55 хождении через образцовый цифроаналоговый преобразователь 7 и поверяемый анало ro-цифровой преобразов атель.

После прохождения реверсивным счетчии ком 4 всех 2 точек динамического диапазона заканчивается первый цикл проверки и процесс контроля возобновляется. Количество циклов подсчитывает счетчик 17 циклов в блоке 9 анализа годности, счетный вход которого соединен с выходом переноса реверсивного счетчика 4. Контроль аналогоцифрового преобразователя в течение нескольких циклов устраняет влияние единичных сбоев разрядов на результат контроля работоспособности аналогоцифрового преобразователя, При реализации критерия останова, например, по двухкратному сбою допускается единичный сбой за два цикла проверки, после чего счетчик 20 сбоев обнуляется. В случае выхода дифференциальной ошибки преобразования в одной из точек динамического диапазона за пределы установленного допуска в каждом из двух циклов будет зафиксирован сбой, второй разряд счетчика

20 сбоев устанавливается при этом в единичное состояние и сбрасывает триггер 12 останова, закрывая тем самым первый селектор 2 и открывая второй селектор 3 ° Второй селектор

3, реализуемый, например, на БИС

К589ХЛ4, включенной в режиме формирования пачки заданного числа импульсов, пропускает на вычитакящий вход реверсивного счетчика 4 такое количество счетных импульсов, что содержимое реверсивного счетчика 4 уменьшается на число тактов задержки сигнала в цепи образцовый цифроаналоговый преобразователь 7 — поверяе мый аналого-цифровой преобраэовательвычитатель 6 кодов — блок 10 cpasнения кодов — триггер 19 сбоя — счетчик 20 сбоев - коммутатор 21 - триггер 12 останова и возвращает кодовую комбинацию, вызвавшую сбои. С этого момента состояние реверсивного счетчика 4 не изменяется и блоком 8 регистрации производится индикация

"Не годен", а также индикация (в простейшем случае светодиодами) кода проверяемой точки, в которой произошли сбои> и кода дифференциальной ошибки преобразования, При отсутствии отклонения характеристики преобразования за пределы допустимых rpa1531217 ннц останова реверсивного счетчика

4 не происходит и после заданного числа циклов проверки, например двух, последний разряд счетчика 17 циклов устанавливается в единичное состояние, которое регистрируется на табло

"Годен" блока 8 регистрации и производит останон работы устройства для контроля ° При наличии сигнала разрешения регистрации на шине "Режим" блока 9. анализа годности, поступающего на вход управления коммутатора

2l, к входу установки нуля триггера

12 останона подключается первый разряд счетчика 20 сбоев и после повторного ручного запуска устройства подачей команды на шину "Пуск" останов происходит ио однократному сбою в следующей точке выхода дифференциальной ошибки преобразования эа пределы установленного допуска, Таким образом можно зарегистрировать все точки отклонения характеристики преобразования аналого-цифрового преобразователя за пределы допуска.

Предлагаемое устройство позволяет проводить автоматический контроль аналого-цифровых преобразователей во всем их динамическом диапазоне с периодом смены контрольных кодовых комбинаций, равным минимальной длительности цикла преобразования, что позволяет повысить оперативность и достоверность контроля. формул а изобретения

1. Устройство для контроля аналого-цифровых преобразователей, содержащее блок синхронизации, первый выход которого соединен с управляющим входом блока сравнения кодов, первые информационные входы которого соединены с соответствующими ньгходами задатчика кода допустимой погрешности, вторые информационные входы — с соответствующими выходами вычитателя кодов, а выход соединен с первым входом блока анализа годности, первые информационные входы нычитателя кодов являются входной шиной, образцовый цифроаналоговый преобразователь выход которого является первой и выходной шиной, а второй выход блока синхронизации является второй ныходной шиной, блок регистрации, о т л и ч а ю щ е е с я тем, что, с целью повышения оперативности контроля

5

40 и достоверности путем учета динамической погрешности преобразователя, введены реверсинный счетчик, блок задержки кодов, два селектора и триг. гер останова, вход устанонки в "1" которого объединен с вторым входом блока анализа годности и является шиной "Пуск", вход установки в "O" триггера останова объединен с первым управляющим входом блока регистрации и подключен к первому выходу блока анализа годности, а прямой и инверсный выходы соединены соответственно с управляющими входами первого и второго селекторов, информационные входы которых объединены и подключены к третьему выходу блока синхронизации, а.выходы соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, кодовые выходы которого через блок задержки кодов соединены с соответствующими нторыми информационными входами вычитателя кодов, управляющий вход которого соединен с четвертым выхо-. дом блока синхронизации, пятый и шестой выходы которого соединены с управляющими входами блока задержки кодов и образцового цифроаналогового преобразователя соответственно, информационные входы последнего объединены с соответствующими первыми информационными входами блока регистрации и подключены к соответствующим кодовым выходам реверсивного счетчика, выход переполнения которого соединен с третьим входом блока анализа годности, второй выход которого с вторым управляющим входом блока регистрации, вторые информационные входы которого соединены с соответствующими выходами вычитателя кодон, а четвертый вход блока анализа годности соединен с седьмым ныходом блока синхро) низации, 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок анализа годности выполнен на элементе ИЛИ, триггере сбоя, коммутаторе, счетчике сбоев и счетчике циклов, счетный вход которого является третьим входом блока, вход установки в "0" объединен с первым входом элемента ИЛИ и является вторым входом блока, а выход соединен с вторым входом элемента

ИЛИ и является вторым выходом блока, первым выходом которого является выход коммутатора, информационные вхо1531217

Составитель И, Романова

Редактор С, Пекарь Техред М.дидык . Корректор С . Шекмар

Заказ 7834 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101 ды которого соединены с соответствующими выходами счетчика сбоев, а управляющий вход является шиной Режим", счетный вход счетчика сбоев соединен с выходом триггера сбоя, входы

5 установки в "1" и "0".которого являются соответственно первым и четвертым входами блока, а выход установки в "0" счетчика сбоев соединен с выходов элемента ИЛИ,