Преобразователь емкости в частоту

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может быть использовано в измерителях с емкостными датчиками. Цель - повышение точности измерения. Устройство содержит источник 1 опорных напряжений, переключатели 3 и 4, компаратор 6, интегратор 7, измеряемый и образцовый конденсаторы 8 и 9, соответственно усилитель 10 сигнала неравновесия, логический блок 11, синхронный детектор 12. Введение в устройство генератора 5 треугольного напряжения, логического блока 11 и аналогового инвертора 2 позволило уменьшить погрешности преобразования за счет уравновешивания мгновенных значений токов, протекающих через образцовый и измеряемый конденсаторы. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) А1 (sg 4 0 01 R 27/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BT0PCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4236368/24-21 (22) 27. 04. 87 (46) 30.12.89.Бюл. № 48 (» ) Ленинградский политехнический институт им.M.È. Калинина (72) А.Л.Соловьев и В.С.Гутников (53) 621.317.333 (088..8) (56) Бухгольц В.П., Тисевич Э.Г.

Емкостные преобразователи в системах автоматического. контроля и управления. M. Энергия, 19?2, с,38-44.

Авторское свидетельство СССР № 1205065, кл. G Ol R 27/26, 1983.

1 (54) ПРЕОБРАЗОВАТЕЛЬ ЕМКОСТИ В ЧАСТОТУ (57) Изобретение относится к нзмери2 тельной технике и может быть использовано в измерителях с емкостными датчиками. Цель — повышение точности измерения. Устройство содержит

iисточник 1 опорных напряжений, переключатели 3 и 4, компаратор 6, интегратор ? измеряемый и образцовый конденсаторы 8 и 9; соответственно усилитель 10 сигнала неравновесия, логический блок 11, синхронный детектор

12. Введение в устройство генератора

5 треугольного напряжения, логического блока 11 и аналогового инвертора 2 позволило уменьшитв погрешности преобразования за счет уравноветива" ния мгновенных значений токов, протекающих через образцовый и измеряемый конденсаторы. 2 ил.

1532885

Изобретение относится к измеритель-. ной технике, в частности к устройствам для измерения параметров электрических цепей.

Целью изобретения является повьппение точности преобразования за счет уравновешивания мгновенных значений токов, протекающих через образцовый и измеряемый конденсаторы. 10

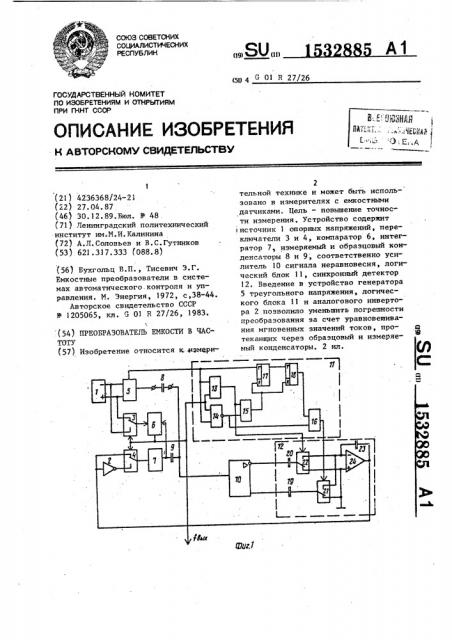

На фиг.1 приведена структурная схема устройства; на фиг.2 — временные диаграммы, поясняющие его работу.

Устройство содержит источник 1 опорных напряжений, аналоговый ин- 15 вертор 2, электронные переключатели, 3 и 4, генератор 5 треугольного напря, жения, компаратор 6, интегратор 7, измеряеМый 8 и образцовый 9 концен,сатори, усилитель 10 сигнала нерав- 20 новесия, логический блок 11, синхрон-, ный детектор 12.

Выходы. источника 1 соединены с входами генератора 5 и через пере1, ключатель 3 — с первым входом компа- 25 ратора 6, первые выводы конденсато . ров 8 и 9 соединены между собой и с входом усилителя 10, выходы которого соединены с сигнальными входами синх ронного детектора 12, выход которого соединен с первым входом переключателя 4 и, через аналоговый инвертор 2 с его вторым входом, выход переключателя 4 соединен с входом интеграто, ра 7, выход которого соединен с вторым входом компаратора 6 и вторым

35 выводом конденсатора 9, второй вывод конденсатора 8 соединен с аналоговым . выходом генератора 5, управляющий вы.! ход которого соединен с первым вхоi дом логического блока 11, второй вход которого соединен с выходом компаратора 6 и управляющими входами переключателей 3 и 4, первый и второй выходы логического блока 11 соединены соответственно с первым и вторым управляющими входами синхронного детектора 12.

Логический. блок 11 содержит логические элементы И 13, ИЛИ-НЕ 14, 50

ИЛИ 15,16 и триггеры 17,18, причем первый вход элемента И 13 соединен с первым входом элемента ИЛИ-НЕ 14, с входом триггера 1-7 и является пер-., вым входом логического блока 11 второй вход элемента И 13 соединен с вторым входом элемента ИЛИ-НЕ 14 и является вторим входом логического блока 11, выход элемента И 13 соединен с первым входом элемента ИЛИ 15 и является вторым выходом логического блока 11, выход элемента ИЛИ-НЕ 14 соединен с вторыми входами элементов

ИЛИ 15 и 16, выход элемента ИЛИ 16 является первым выходом логического блока 11, выход элемента ИЛИ 15 соединен с входами В триггеров 1? и 18, выход триггера 17 соединен с входом

Т триггера 18, выход которого соединен с первым входом элемента ИЛИ 16.

Синхронный детектор 12 содержит конденсаторы 19,20, переключатели 21, 22, конденсатор 23, усилитель 24, причем управляющие входы переключателей 21 и 22 являются соответственл но первым и вторым управляющими входами синхронного детектора 12, первые выходы переключателей 21 и ?2 соединены между собой, с инвертирующим - входом усилителя 24 и с первым выводом конденсатора 23, второй вывод которого соединен с выходом усилителя

24 и является выходом синхронного детектора 12, входы переключателей 21 и 22 соединены с входами синхронного детектора 12 через конденсаторы 20 и 19.

Устройство работает следующим образом.

Генератор 5 формирует на своем информационном выходе сигнал треугольной формы со стабильной частотой и амплитудой, равной + U>, где + U,< выходное напряжение источника 1 (см. фиг.2.1). Аналоговый инвертор 2, переключатели 3 и 4, ком аратор 6 и интегратор 7 представляют собой преобразователь напряжение-частота (ПНЧ). На выходе интегратора 7 формируется треугольное напряжение (см. фиг,2.2) с амплитудой +П „, размах которого стабильно поддерживается в пределах данного значения компаратором 6.. При возрастании напряжения на выходе интегратора 7 до значения

+Цоп срабатывает компаратор 6, на первый вход которого подается +U ä, через переключатель 3 от источника 1, а на второй вход — выходной сигнал интегратора 7. Выходной сигнал компаратора 6 управляет работой переключателя 3 и 4, следовательно, напряжение на первом входе компаратора 6 становится равным -U д,так как теперь первый вход компаратора 6 через переключатель 3 подключен к выходу

1532885

-U0„ источника 1. Одновременно с переключением переключателя 3 переключается и переключатель 4, вследствие чего знак напряжения прило5 женного к входу интегратора 7 -U q меняется на противоположный +U „ sc счет применения аналогового инвертора 2 ° Выходной сигнал интегратора

7 меняет направление интегрирования и при достижении на его выходе напряжения, равного -U и, опять срабатывает компаратор 6, переключатели 3 и 4 занимают первоначальные положения, и весь процесс периодически повторяется. Чем больший уровень выходного напряжения с синхронного детектора 12 подается на вход ПНЧ, т.е. на вход аналогового инвертора 2 и нормально замкнутую входную цепь коммутатора 20

4, тем выше частота выходного треугольного сигнала на выходе интегратора 7.Выходная частота треугольного сигнала на выходе интегратора..7.и прямоугольного сигнала на выходе ком- 25 паратора 6 определяется выражением

1 !

f = — — =U7

2 „вх 4Поп и сП1 оп с = Со1 сь " dt (г) " 1 оп

1 с

Сх Ы (3) Яоп где — — — скорость нарастания лиЫ нейного участка треугольгде f. — выходная частота преобра30 зователя емкость-частота; — время интегрирования инA тегратора 7, полученное из выражения и 35 гуопе = Ubx dt

Ц (>

VBK u и где Usa — напряжение на входе ин- 40 тегратора 7; галоп - выходное напряжение интег..ратора 7, изменяющееся от д +Поп

Т.„- постоянная времени интегра- 45 тора 7.

Величины токов, протекающие через образцовый 9 и измеряемый 8 конденсаторы, определяются углом наклона треугольного. сигнала на выходах генератора 5 и интегратора 7. ного сигнала на выходе интегратора 7.

Из выражения (4) манна сделать вывод, что функция преобразования данного преобразователя емкости в частоту будет определяться выраже кием:

, С

f f Ф .х о (5) где х — выходнаЯ частота пРеабРазо.вателя; о

à — частота генератора 5.

Преимуществам изобретения по сравнению с прототипом является уменьшение погрешности при работе с дифференциальными емкостными датчиками, так как в данном случае происходит уравнавешивание мгновенных значений токов, протекающих через измеряемый и образцовый конденсаторы, а также

dUon — скорость нарастания лиdt нейного участка треугольного сигнала на выходе генератора 5.

Погический блок 11 и синхронный детектор 1 2 работают таким образом, чта выходное напряжение последнего пропорционально разности токов в конденсаторах 8 и 9 в те моменты времени,кагда токи в них текут в противоположном направлении. Работу этих блоков поясняют эпюры на фиг. 2: фиг. 2. 1 напряжение на аналоговом выходе генератора 5; фиг.2.2 — напряжение на выходе интегратора 7; фиг. 2. 3 — логические сигналы на управляющем выходе генератора 5; фиг.2.4 — логические сигналы на выходе компаратора

6; фиг. 2.5 — логические сигналы на первом выходе блока 11; фиг.2.6— логические сигналы на втором выходе блока 11; фиг.2.7 — напряжение на выходе синхронного детектора 12.

Когда токи, протекающие через конденсаторы 8 и 9 в моменты време3 выравнены, напряжение на выходе усилителя 10 в эти моменты времени будет равно нулю. При достижении условия . равновесия в указанные интервалы времени токи, протекающие через конденсаторы 8 и 9, определяемые выражениями (2) и (3), равньг, 1

1532885 Формула изобретения

Составитель О. Богданович

Редактор О.Спесивых Техред Л,Олийнык Корректор 3. Ло нч аков а

Заказ 8095/51 Тираж 714 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

I Производственно-издательский комбинат "Патент", r.Ужгород, ул. Гагарина, 101 расширение функциональных всзможнос-4 ,тей благодаря способности нового пре.образователя измерять значение емкости при Со>С, С С, С Ñ при этом частота выходного сигнала может быть меньше, равна, или больше частоты генератора 5.

Преобразователь емкости в частоту, содержащий источник опорных напряжений, первый и второй электронные ,переключатели, образцовый и измеря, емый конденсаторы, первые выводы кото рых соединены с входом усилителя сигнала неравновесия, синхронный детектор, аналоговые входы которого . соединены с выходом усилителя сигнала неравновесия, интегратор и компаратор, соединенные последовательно, отличающий с я тем, что, с целью повышения точности, в него введены аналоговый инвертор, логический блок и генератор треугольного напряжения, причем выходы источника опорных напряжений соединены с входами первого коммутатора и генератора треугольного напряжения, аналоговый выход которого соединен со вторым выводом измеряемого конденсатора, а управляющий выход — с первым входом логического блока, второй вход которого соединен с выходом компаратора и управляющими входами переключателей, выход первого переключателя соединен с вторым входом компаратора, вход интегратора соединен с выходом второго переключателя, первый и второй выходы логического блока соединены с первым и вторым управляющими входами синхронного детектора, выход которого соединен с первым входом второго компаратора и через аналоговый инвертор — с вторым входом второго компаратора.