Устройство для умножения двоичных чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для выполнения арифметических операций. Цель изобретения - расширение функциональных возможностей за счет вычисления ряда чисел A<SB POS="POST">1</SB><SP POS="POST">.</SP>A<SB POS="POST">2</SB>, A<SB POS="POST">2</SB><SP POS="POST">.</SP>A<SB POS="POST">3</SB>, A<SB POS="POST">3</SB><SP POS="POST">.</SP>A<SB POS="POST">4</SB>,....,A<SB POS="POST">M-1</SB><SP POS="POST">.</SP>A<SB POS="POST">M</SB>. Новым в устройстве, содержащем регистры множимого 1 и множителя 2, две группы элементов И 3 и 4, два одноразрядных сумматора 5 и 6, группу регистров 7 и коммутатор 8, является введение двух групп элементов И-НЕ 9,1-9,3 и 10,1-10,3 и двух групп элементов И 11,1-11,7 и 12,1-12,7. Числа поступают на вход устройства непрерывным потоком. Группы элементов И 11 и 12 под действием сигналов управления с элементов И-НЕ 9,1-9,3 и 10,1-10,3 обеспечивают формирование только конъюнкций сомножителей из пар смежных чисел. Результат считывается с выхода устройства каждые полтакта. 2 ил.

СОЮЗ COBETCHHX социАлистичесник

РЕСПУБЛИН

С 06 Р 7/52 4 фЯ! Р Д «CAR

F " г) ..r,-,À фие. t

ГОСУДАРСТВЕННЫЙ НОМИТЕТ. г1о изоБРетениям и отнРьггинм пРи гкнт сссР

1 (21) 4434225/24-24 (22) 30.05.88 (46) 30.12.89. Бюл. К . 48 (71) Одесский политехнический институт (72) АвВо Дрозду ЕеЛе ПОлин, C,С, Шапо, В.Н. Огинский и 1О,В.Дрозд (53) 681.325(088.8) (56) Авторское свидетельство СССР

0 1203512, кл. G 06 F 7/52, 1984.

Авторское свидетельство СССР

11 1439579, кл. G 06 F 7/52, 1987. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВОИЧНЫХ ЧИСЕЛ (57) Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для выполнения арифметических операций. Цель изобретениярасширение функциональных воэможнос"

2 тей за счет вычисления ряда чисел а „а, а а, а ° ад...,,а, „а, Новым в устройстве, содержащем регистры множимого 1 и множителя 2, две группы элементов И 3 и 4, два одноразрядных сумматора 5 и 6, группу регистров 7 и коммутатор 8 является введение двух групп элементов И-НЕ 9-1 ...,9-3 и

10-1,...,10-3 и двух групп элементов.

И 1 11 9 ° о 1 17 и 121 ° ° 12 7а

Входные числа поступают на вход устройства -непрерывным потоком. Группы элементов И 11 и 12 под действием сигналов управления с элементов И-HR

9-1,...,9-3 и 10-1,...,10-3 групп обеспечивают формирование только конъюнкций сомножителей из пар смежных чисел. Результат считывается с выхода устройства каждые полтакта, 2 ил.

1332918

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для выполнения арифмети" ческих операций.

Цель изобретения — расширение

5 функциональных возможностей за счет вычисления ряда чисел а, а, а а, а а4, ...,а„,, а,„.

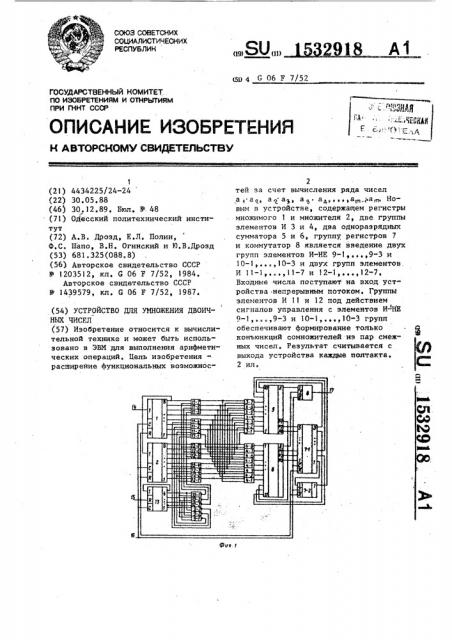

На фиг. 1 представлена функцио-. нальная схема устройства, на фиг.2— временная диаграмма работы устройства.

Устройство содержит регистр 1 мно, .жимого, регистр 2 множителя, элементы И 3-1, 3-2,...,3-7 второй группы, элементы И 4-1, 4-2,...,4-8 первой группы, одноразрядные сумматоры 5 и

6, регистры 7-1 и 7-2 группы, комму" татор 8, элементы И-НЕ 9-1, 9- 2 и 20

9-3 первой группы, элементы И-НЕ

l0-1, 10-2 и 10-3 второй группы, элементы И 11-1, 11-2,...,11-7 четвертой группы, элементы И 12-1, 12-2,..., ...,1.2-7 третьей группы, регистр 13 25 управления, вход 14 множимого устройства, вход 15 сброса устройства, тактовый вход 16 устройства и выход

17 устройства.

Устройство работает следующим образом.

На тактовый вход 16 устройства поступают синхроимпульсы (СИ типа меандр, тактирующие работу устройства.

На вход 15 сброса устройства поступает импульс, сбрасывающий в "О". регистры множимого.l и множителя 2, регистры 7-1 и 7-2, а также регистр

13 управления.

На вход 14 множимого устройства с частотой следования СИ поступают в последовательном коде разряды (начиная с,первого, младшего) потока чисел а,, а, а,...,а,„,, а„, (где ш — количество входных чисел), Под действием СИ, поступающих на входы сдвига регистров множимого 1 и множителя 2, разряды входных чисел продвигаются в каждом такте в регистре 1 и далее в последовательно соединенном с ним регистре 2 на одну позицию в сторону старших разрядов.

При этом на выходах разрядов регистров множимого 1 и множителя 2

55 формируются последовательности разрядов входных чисел в соответствии с временными диаграммами (фиг,2).

Числа, указанные на временных диаграммах выходов разрядов регистров 1 и 2 означают номера разрядов чисел а„,а,а, причем разряды чисел а и а> помечены (в отличие от разрядов числа а,) дним и двумя штрихами соответственно.

После обнуления регистров устройства в регистр управления 13 вдвигается под действием СИ единичное значение с инверсного выхода его четвертого разряда, При этом на прямом и инверсном выходах первого разряда регистра 13 управления формируются последовательности импульсов в четыре раза большей длительности, чем СИ. (фиг.2, инверсный выход первого разряда). С выходов второго, третьего и четвертого разрядов регистра 13 управления снимаются аналогичные последовательности импульсов, однако сдвинутые на один, два,и три такта работы устройства соответственно.

Последовательности импульсов с; прямого и инверсного выходов первого разряда регистра 13 управления поступают на первые входы элементов И-НЕ

9 и 10 группы. Последовательности импульсов с выходов второгo < третьего и четвертого разрядов регистра 13 управления подаются на вторые входы соответствующих элементов И-НЕ

9 и 10 групп. При этом на выходах элементов И-HE 9 и 10 групп формиру" ются сигналы управления .(фиг.2, выходы элементов 9 и 10), Последовательности разрядов чисел с выходов разрядов (исключая пятый разряд) регистров множимого 1 и множителя 2 поступают на первые входы элементов И ll и 12 групп, Яа вторые входы этих элементов И подаются сиг-. налы управления с выходов элементов

И-НЕ первой 9 и второй 10 групп,. а также с инверсного выхода регистра 13 управления, Элементы И 11 и 12 групп обнуляют часть разрядов в последовательностях разрядов чисел.в тактах, где соответ,ствующие сигналы управления принимают нулевые значения. Полученные усечен" ные последовательности разрядов чисел и последовательности с выходов пятых разрядов регистров множимого 1 и множителя 2 поступают на входы элементов

И 3 и 4 групп, которые под .их действием формируют последовательности конъюнкции, отображенных на соответ- ствующих временных диаграммах двух"

5 153 разрядными кодами. Первый и второй разряды укаэанных кодов являются разрядами чисел множимого и множителя, перемножаемыми на элементах И 4 и 3. .При этом на выходах элементов

И 3-1, 3-2,...,3-7 второй группы формируются конъюнкции с весовыми функциями 2, 2, 24...,,? ", а на выходак элементов 4-1, 4-2,...,4-8 первой группы — конъюнкции с весовыми функциями 2,2,2,...,2 " (k=O,1,2...в

° ° °,7}а

На одноразрядном сумматоре 5 складываются конъюнкции, имеющие одинаковые в такте весовые функции с четным значением k,,а также сигналы с выходов четных разрядов переносов сумма" тора 5, задержанные на регистрах группы 7, и сигналы с выходов нечет-ных разрядов переносов сумматора 6, задержанные на регистрах 7 группы.

Сигналы с выходов суммы одноразрядных сумматоров 5 и 6 поступают на информационные входы коммутатора 8, который под действием СИ подключает указанные сигналы на выход

17 устройства, в первых и вторых половинах тактов, Таким образом, с вы-: хода 17 устройства с удвоенной частотой следования синхроимпульсов СИ снимается последовательный код произведения перемножаемых чисел, причем в первых и вторых половинах так" тов вырабатываются разряды произведения, имеющие весовые функции с четными и нечетными значениями 1с, На временных диаграммах (фиг ° 2 показано, что вслед за разрядами

l,2,...,8 первого числа поступают .. без паузы разряды 1,2,...,8 второго. числа и т.д. Управляющие сигналы обеспечивают формирование только коиъюнкций сомножителей из пар смежных чисел потока. С выхода 17 устройства снимается непрерывная последовательность разрядов результатов а, -а, а a, à a<, ...а„,, а .

Формула изобретения

Устройство для умножения двоичных чисел, содержащее регистры множителя и множимого, первую и вторую группы элементов И, два одноразрядных сумматора, группу регистров и коммутатор, выход которого соединен с выходом устройства, тактовый вход которого соединен с входами сдвига реги2918

30 мационным .входом второго регистра группы, выход которого соединен с входом восьмого слагаемого второго одноразрядного сумматора, входы девятого и десятого слагаемых которого

35 соединены с выходами третьего и пятого разрядов первого регистра группы соответственно, выходы второго и четвертого разрядов которого соединены

0 соответственно с ..входами десятого и одиннадцатого слагаемых первого одноразрядного сумматора, выход пятого разряда регистра множимого соединен с вторыми входами четвертых элементов И первой и второй групп, выход пятого,разряда регистра множителя соединен с первым входом пятого элемента И первой группы и вторым входом четвертого элемента И второй группы, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностей sa счет вычисления ряда чисел а а<, а ° a» а ° а,1...,,а„, .а (ш — количество входных чисел), в него введены две группы элементов И-НЕ, третья и четвертая группы элементов

И и регистр управления, информационный вход которого соединен с инверс5

20 стров множимого и множителя, входами .записи регистров группы и управляющим входом коммутатора, первый и второй информационные входы которого соединены с выходами суммы первого и второго одноразрядных сумматоров соответственно, вход сброса устройства соединен с входами сброса регистров группы и регистров множителя, информационный вход устройства соединен с информационным входом регистра множимого, входы элементов И первой и второй групп соединены с входами с первого по восьмое слагаемых первого и с входами с первого по седьмое слагаемых второго одноразрядных сумматоров соответственно, выход первого разряда переноса второго одноразрядного сумматора соединен с входом девятого слагаемого первого одноразрядного сумматора, выходы третьего, второго и первого разрядов переноса первого одноразрядного сумматора и выходы третьего и второго разрядов переноса второго одноразрядного сумматора соединены соответственно с входами с первого по пятый разрядов первого регистра группы, выход первого разряда которого соединен с инфорным выходом четвертого разряда реги-.

1532918 стра управления, прямой выход первого разряда которого соединен с первыми входами элементов И-НЕ первой группы, вторые входы первого, второго и третЬего элементов И-НЕ первой группы соединены соответственно с выходами в срого, третьего и четвертого разрядов регистра управления и первыми в одами третьего, второго и первого элементов И-НЕ второй группы, первые взводы элементов И третьей и четвертой групп соединены соответственно с в ходами соответствующих разрядов ре" истров множимого и множителяg выходы лементов И-НЕ первой и второй групп оединены с вторыми входами соответтвующих элементов И четвертой и треьей групп соответственно, кроме втоых входов первых элементов И третьей о . четвертой групп, вторые входы.пер. ыех элементов И третьей и четверой групп соединены с вторыми входами лементов И-HE второй группы и ин" ерсным выходом первого разряда ре- 25 истра управления, выходы с первого

1 по седьмой элементов И четвертой групгруппы соединены соответственно с первыми входами с первого по четвертый и с шестого по восьмой элементов

И первой группы, выходы с второго

-1 по седьмой элементов И третьей группы соединены соответственно с первыми входами с первого по третий и с пятого по седьмой элементов И второй группы, выходы с первого по седьмой элементов И третьей группы соединены соответственно с вторыми входами с восьмого по пятый и с третьего по первый элементов И первой группы, вы-. ходы с второго по седьмой элементов

И четвертой группы соединены соответственно с вторыми входами с седьмого по пятый и с третьего по первый элементов И второй группы, выход восьмого разряда регистра множнмого сое-.. динен с информационным входом регистра множителя, тактовый вход и вход сброса устройства соединены соответственно с входом сброса и входом сдвига регистра управления.

1532918 йк. гзс2

6w.Âï2 вб. Aa t

Af. 9 дм.м94

Вим9-2

Вил 9-д

Ввиж3И биге.ЮЬмИ94

Викри бил Я бюкялИ биг4.24 ба.и Ы йимю-б би.м.б-г би.и4-f би.и4-2 бюкмИ йим4бым4 S

Bw.и4-б бим4 f биг444

áìõ./7

4 г л гг ю 5 г 4 ю ю

f 1 У 4Ф S Õ 6 б Td г4 т 4 4 гт

t я

Составитель Е. Мурзина

Редактор Л. Пчолинская Техред Л.Олийнык Корректор С. Черни

Заказ 8100/53 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-.35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101