Устройство для формирования позиционного признака в модулярной арифметике

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к устройствам для формирования позиционного признака в модулярной арифметике, необходимого при решении задач модулярной арифметики. Цель изобретения - упрощение устройства и повышение его быстродействия за счет суммирования констант малой разрядности. Код числа в остатках поступает на информационный вход 1 устройства и является адресом, по которому из блока 2 хранения констант считываются константы для суммирования в блоке 3 суммирования. Выход блока 3 суммирования разделен на три части, причем выходы, соответствующие старшим разрядам, образуют информационный выход 7 устройства, выходы, соответствующие средней части разрядов, соединены со входом схемы 4 сравнения с константой, выход которой является контрольным выходом 5 устройства. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (1!) 1,1)) 4 С 06 F 7/72

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К ASTOPCH0MY СВИДЕТЕЛЬСТВУ

1 (21) 4447536/24-24 (22) 04.05,88 (46) 30.12.89. Бюл, )) 48 (71) Институт математики и механики

АН КазССР (72) В,N.Àìåðáàåâ, И.Т.Пак, P.Н,Турмухамбетов и М.С.Суюндиков (53) 681.3(088.8) (56) Авторское свидетельство СССР

М.1125619, кл. G 06 F 7/72, 1983 °

Авторское свидетельство СССР

11,377766, кл. G 06 F 7/72, 1970. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПОЗИЦИОННОГО ПРИЗНАКА В МОДУЛЯРНОЙ

АРИФМЕТИКЕ (57) Изобретение относится к вычислительной технике,,а именно к устройствам для формирования позиционного признака в модулярной арифметике, необ2 ходимого при решении задач модулярной арифметики, Цель изобретения — упрощение устр-ва и повышение быстродействия за счет суммирования констант малой разрядности. Код числа в остатках поступает на информационный, вход

1 устройства и является адресом, по; которому из блока 2 хранения констант считываются константы для суммирования в блоке 3 суммирования. Выход блока 3 суммирования -разделен на три части, причем выходы, соответствующие старшим разрядам, образуют информаци-. онный выход 7 устройства, выходы со-, ответствующие средней части разрядов, соединены с входом схемы 4 сравне- g ния с константой, выход которой является контрольным выходом 5 устройства. 1 ил..

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1 5329 24

Изобретение относится к вычислиельной технике, предназначено для ормирования позиционного признака, еобходимого при решении задач моду5 ярной арифметики, и может быть исПользовано при технической реализации соответствующих устройств.

Цель изобретения — упрощение устройства. 10

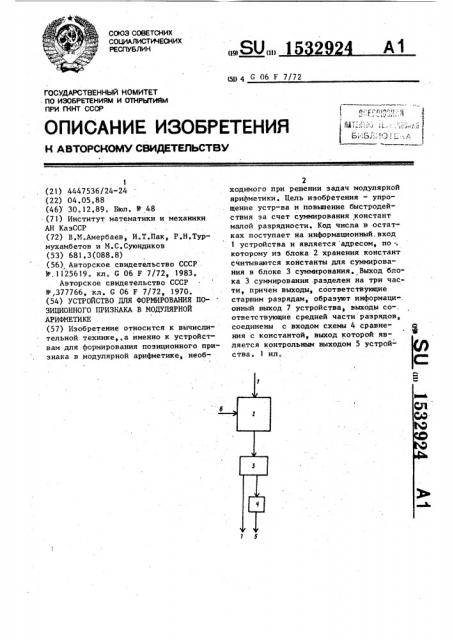

На чертеже представлена схема устойства для IbopMHpoBBHHsi позицион ого признака в модулярной арифметие.

Устройство содержит информационный 15 ход 1 устройства, блок 2 хранения онстант, блок 3 суммирования, схему сравнения с константой, контроль-! ый выход 5 устройства, тактовый вход 6 устройства и информационный выход

7 устройства.

Устройство может выполнять как параллельное, так и последовательное . формирование неточного ранга на выхо.дде 7 устройства. 25

В случае параллельного формирования неточного ранга на вход 1 устройства поступают и (где n — количество оснований) остатков ю6,, Блок 2 хране ния констант аналогично прототипу, содержит и ППЗУ объемом 2 x2)log nt бит для каждого модуля (где К; - разрядность остатков), Блок 3 состоит из сумматоров разрядности 3 1 logan) бит собранных по пирамидальной схеме, В случае последовательного форми рования неточного ранга на вход 1 уст,ройства одновременно поступают коды остатка и номера основания, блок 2: хранения констант содержит одно ППЗУ, 40 ,а блок 3 суммирования реализован в ви де накапливающего сумматора с входом обнуления и тактовым входом.

Блок 3 суммирования имеет 3 1log nj разрядный выход, из которых старшие 45

)1о 1, n(разрядов образуют первую группу выходов блока 3 суммирования, на которой формируется значение неточ- „ ного ранга, средние jlog nf разрядов игнорируется, 50

Схема 4 сравнения с константой может быть реализована посредством элемента И-НЕ и формирует единичные значения правильности ранга, . Устройство реализует kD-модель мо-! дулярной арифметики. Константы для вычисления ранга определяется по формуле:

P -I

2) 10 п1. 1 2

P.

1 где P1 - основания системы (нечетные) ; — вычеты числа А разрядности

К,(K; b)log P;(); и

m =/ Г Р /Р /Р - мультипликативК 1 ные обратные к П Р /Р; по модулю P

Устройство работает следующим образом.

Совокупность остатков числа А (очередной остаток и код номера остатка), для которого необходимо выработать позиционный признак, по информационному входу 1 соответствующей разрядности подается на адресный вход ( блока 2 хранения констант. По сигналу с входа 6 константы разрядности

2)log n(считываются в блок 3 суммирования, На выходе блока 3 суммирования образуется (при последовательном формировании неточного ранга через и тактов) результат. Старшие разряды результата поступают на выход

7 устройства, следующие sa ними разряды — на @ход схемы 4 сравнения с константой, на выходе которой формируется значение, поступающее на вы- ходе которой формируется значение, поступакнцее на выход 5 устройства.

При параллельном формировании неточного ранга достигается повышение быстродействия.

Формула. изобретения . Устройство для формирования позиционного признака в модулярной арифметике, содержащее блок хранения констант, блок суммирования и схему сравнения,с константой, причем инфор". мационный вход устройства соединен с адресным входом блока хранения констант, вход разрешения выборки которого является тактовым входом устройства, выход блока хранения констант соединен с входом .блока .сумми— рования, выход схемы сравнения с константой является контрольным выходом устройства, информационный выход icoторого соединен с первой группой выходов блока суммирования о т л и ч аю щ е е с я тем, что, с целью упрощения устройства, вторая группа выходов блока суммирования соединена с входом схемы сравнения с константой.