Устройство для сопряжения центрального процессора с абонентами

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для организации связи в распределенных вычислительных системах. Целью изобретения является расширение функциональных возможностей устройства за счет проверки возможности доступа и преобразования адреса вызываемого абонента. Устройство содержит первый дешифратор адреса 1, первый блок 2 определения возможности доступа, первый коммутатор 3, первый блок 4 анализа, первый накопитель данных 5, преобразователь 6 параллельного кода в последовательный, первый блок 7 гальванической развязки, блок 8 управления, второй коммутатор 9, дешифратор 10, второй блок 11 гальванической развязки, второй накопитель данных 12, второй дешифратор адреса 13, второй блок 14 определения возможности доступа, второй блок 15 анализа, преобразователь 16 последовательного кода в параллельный. Устройство обеспечивает сопряжение абонентов с центральной станцией с преобразованием адреса и контролем возможности обмена. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (!9) (11} (51)4 G 06 F 13/00

О ИОАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМЪГ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР

1 (21) -4315480/24-24 (22) 01.07.87 (46) 30.12.89. Бюл. М 48 (72) О.И. Буянов, М.А. Овчинников и Ю.А. Стародубцев (53) 681.3(088.8) (56) Патент США !(" 4231084, кл. G 06 F 13/00, опублик. 1980.

Патент Японии !(50 l8747, кл. G 06 F 3/00, опублик. 1975. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦЕНТРАЛЬНОГО ПРОЦЕССОРА С АБОНЕНТАМИ (57) Изобретение относится к вычислительной технике и может быть использовано для организации связи в распределенных вычислительных системах. Целью изобретения является расширение функциональных возможностей устройст.ва за счет проверки возмож2 ности доступа и преобразования адреса вызываемого абонента. Устройство содержит первый дешифратор 1 адреса, первый блок 2 определения возможности доступа, первый коммутатор 3, первый блок 4 анализа, первый накопитель 5 данных, преобразователь

6 параллельного кода в последовательный,первый блок 7 гальванической развязки, блок 8 управления, второй коммутатор 9,дешифратор 10,второй блок 11 гальванической развязки, второй нанопитель 12 данных, второй дешифратор

13 адреса, второй блок 14 определения возможности доступа, второй блок

15 анализа, преобразователь 16 последовательного кода в параллельный.

Устройство обеспечивает сопряжение абонентов с центральной станцией с преобразованием адреса и контролем воэможности обмена. 1 з.п. ф-лы, 3ил. а

1532936

Изобретение относится к вычислительной технике и может быть использовано для организации связи в распределенных вычислительных системах„

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения про верки возможности доступа и преобра,зования адреса вызываемого абонента.

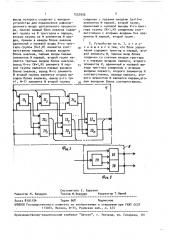

На фиг. 1 представлена блок-схема, устройства на фиг. 2 - схема блоков

1 анализа; на фиг. 3 - схема блока упра вления.

Устройство содержит (Фиг.1) первый 15 ешифратор 1 адреса, первый блок 2 пределения возможности доступа, пер,вый коммутатор 3, первый блок 4 ана лиза, первый накопитель 5 данных,, первый преобразователь б параллель-; 20 ного кода в последовательный, первый блок 7 гальванической развязки,, блок Я управления, второй коммутатор

1 9, дешифратор 10, второй блок 11 гальванической раз вяз ки, второй на - 25

;копитель 12 данных, второй дешифра тор 13 адреса, второй блок 14 опре деления возможности доступа, второй блок 15 анализа, преобразователь 16 последовательного кода в параллель-! ный, группу входов 17 устройства для подключения к выходам центральной станции, группу выходов 1 8 устройст ва для подключения входов абонентов, руппу входов 19 устройства для ,подключения выходов абонентов, груп пу выходов 20 устройства для подклю" чения входов центральной станции .

Блоки 4,15 анализа содержат (фиг.

2) группу 21 триггеров и первую, вто- 0 рую группы элементов И 22,23

Блок 8 управления (Фиг.3) содержит триггер 24 и первый, второй элементы И 25,26. Блоки 1,2, 13, 14 выполнены на ПЗУ.

Устройство работает следующим образом.

Запросы на организацию связи с абонентами поступают на .один из вхо- дов группы входов 17 устройства и инициируют дешифратор 1 содержащий информацию о соответствии адресов сопрягаемых абонентов, и блок 4 анализа.

Адрес абонента получателя поступа" ет на вход блока 2, в котором c:oäåðжится информация о возможности Физического и организационного доступа по каждому адресу абонента. Под воз" можностью физического доступа понимается наличие канала связи, работоспособность аппаратуры. Под возможностью организационного доступа понимается регламентация доступа к абонентам, Первый блок 4 анализа определяет возможность организации соединения с абонентом-получателем на основании информации, поступающей от блока 2.

В случае возможности организации соединения первый блок 4 анализа передает в преобразователь служебную информацию, поступающую по соответствующему входу группы входов 17 устройства, и выдает сигнал в первый коммутатор 3, обеспечивающий разрешение записи данных, поступающих по соответствующему входу группы входов

17 системы в первый накопитель 5 данных .

Преобразователь 6 обеспечивает преобразование служебной информации в вид, исполь3уемый абонентом.

Данные из первого накопителя 5 данных и служебная информация из преобразователя 6 поступают на соответствующие выходы группы выходов 18 устройства через блок 7, обеспечивающий электрическое согласование сигналов. Аналогичные функции по со" гласованию электрических сигналов выполняет блок 11. Они могут быть, например, оптронными приемниками и передатчиками, обеспечивающими согласование уровней и гальваническую развязку устройства с абонентами, стыкуемыми по выходам 18 и входам 19.

Первый блок 4 анализа выдает информацию о невозможности организации соединения, например, отсутствие адреса абонента и невозможность физического или организационного доступа, в центральную станцию по соответствующему выходу группы выходов 20.

Запросы на организацию соединений со стороны абонентов поступают по соответствующему входу группы входов

19 в дешифратор 0 через блок 11.

Дешифратор 10 инициирует дешифратор

13 и блок 14.

Дешифратор 13 содержит информацию о соответствии адресов сопрягаемых абонентов.

Блок 14 содержит информацию о возможности физического и организа" ционного доступа по каждому адресу сопрягаемых абонентов, 5

153

Второй блок 15 анализа на основании информации, поступающей от дешифратора 13 и блока 14, определяет возможность организации соединения.

В случае возможности организации соединения второй блок 15 анализа передает в преобразователь 16 служебную информацию, поступающую с дешифратора 10, и выдает сигнал во второй коммутатор 9, обеспечивающий разрешение записи данных, поступающих по соответствующему входу группы входов 19 через блок 11 во второй накопитель 12 данных.

Преобразователь 16 обеспечивает преобразование служебной информации в вид, используемый центральной станцией. Служебная информация и данные выдаются по соответствующим выходам группы выходов 20 устройства °

Первый блок 4 анализа и второй блок 15 анализа работают по командам, поступающим от блока 8 управления, который получает управляющую информацию по соответствующему входу группы входов 17. Эти команды являются Фактически сигналами опроса состояния блоков анализа и съема информации для передачи в соответствующие преобразователи кода и коммутаторы.

2936

l0

30 доступа, первый, второй блоки анализа, первый, второй коммутаторы, преобра зова тел ь па раллел ь ног о кода в последовательный, преобразователь последовательного кода в параллельный, первый, второй накопители данных и дешифратор, причем вход первого дешифратора адреса и первый вход первого блока анализа являются входом устройства для подключения адресного выхода центрального процессора, информационный вход первого коммутатора является входом устройства для подключения информа ционного выхода центрального процессора, выход первого дешифратора адреса соединен с информационнымм входом первого блока определения возможности доступа, выход которого соединен с вторым входом первогоо блока а нали за, пер вый выход которого соединен с управляющим входом первого коммутатора и через преобразователь параллельного кода s последовательный соединен с первым входом первого блока гальванической развяз- ки, входной вход синхронизации которого соединен с выходом первого нако пителя данных, вход которого соединен с выходом первого коммутатора, второй выход первого блока анализа является выходом устройства выходом устройства для подключения входа пре"

55 формуг<а и з обретения

1. Устройство для сопряжения центрального процессора с абонентами, содержащее первый, второй блоки гальванической развязки и блок управления, прич ем пер вый и второй выходы первого блока гальванической развязки RBJlRloTcR выходами устройства для подключения входов данных и синхронизации абонентов, первый, второй входы второго блока гал ь ва ничес кой развязки являются входами устройства для подключения соответственно выходов данных и запроса абонентов, вход блока управления я.вляется входом устройства для подключения адресного выхода центрального процессора, о тл и ч а ю щ е е с я тем, что, с це" лью расширения функциональных возможностей устройства за счет обеспече.ния проверки возможности доступа и преобразования адреса вызываемого абонента, в него введены первый, второй дешифраторы адреса и первый, второй блоки определения возможности

50 рывателя центрального процессора, первый, второй выходы второго блока гальванической развязки соединены соответственно с первым информационным входом второго коммутатора и с входом дешифратора, выход которого соединен с входами второго дешифратора адреса и второго блока определения возможности доступа, первый, второй, третий входы второго блока анализа соединены соответственно с выходами второго дешифратора адреса и второго блока определения возможности доступа и с первым выходом блока управления, второй выход которого соединен с третьим входом первого блока анализа, выход второго блока анализа соединен с управляющим входом второго коммутатора и с входом преобразователя кода последовательного в параллельный, выход которого является выходом устройства для, подключения адресного входа центрального процессора, выход второго коммутатора соединен с информационным входом второго накопителя данных, 1532936 соединен с первыми входами (р+1)=х элементов И первой, второй групп, единичный и нулевой выходы К-го триггера группы (К=1,М) соединены соответственно с вторыми входами К=х элементов И первой, второй групп.

Сост а ви тел ь С. Бурухи н

Техред N. Ходанцч Корректор Т. Палий

Редактор И. Бандура

Заказ 8101/54 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Выход которого соединен с выходом устройства для подключения информационного входа центрального процессора, причем каждый блок анализа содер- 5 жит группу из И триггеров и йервую, вторую группы из И элементов И каж,вая, причем в каждом блоке анализа единичный и нулевой входы К-го триггера группы (К1,И) являются соотетственно первым, вторым входами лока анализа, первые входы первых

Элементов И первой, второй групп являются третьим входом блока анализа, выход K-ro (К 1,И) элемента И пер ой группы является первым выходом блока анализа, выход И-го элемента второй группы является вторым вы <одом блока анализа, выход р-го (р=

М1, И-1) . элемента И второй группы

2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок управления содержит триггер и первый, второй элементы И, причем вход блока соединен со счетным входом триггера и с первыми входами первого, второго элементов И, единичный и нулевой выходы триггера соединены с вторыми входами первого, второго элементов И соответственно, выходы первого, второго элементов И являются первым,вторым выходами блока соответственно.