Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к запоминающим устройствам и может быть использовано при создании систем оперативной памяти вычислительных устройств, решающих информационно-логические задачи. Цель изобретения - повышение быстродействия запоминающего устройства и расширение области применения за счет обеспечения многомерного параллельного доступа. Устройство содержит адресные, управляющие, информационные входы, информационные выходы, одноразрядные накопители, коммутатор, распределитель информационных сигналов, первую и вторую группы коммутаторов, элементы НЕРАВНОЗНАЧНОСТЬ и инверторы. 2 ил.

СОЮЗ СОНЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„.ЯО„„5 (51)4 G 11 С 11/00

l р

t„

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И А ВТОРСИСМУ СВИДЕТЕЛЬСТВУ

Щ I

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

tlPH ГКНТ СССР

1 (21) 4338558/24-24 (22) 03,12,87 (46) 30.12,89. Бюл. 11 48 (71) Институт кибернетики им. В.М,Глушкова (72) N.А,Сабельников и K.Н.Дубровский (53) 681. 327. 6(088. 8) (56) Электроника, 1973, У 7, с, 45, Авторское свидетельство„СССР

В 928408, кл. С ll С 11/Gg, 1982 °

: (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к запоминающим устройствам и может быть использовано при создании систем оператив-„

Изобретение относится к запоминающим устройствам и .может быть использовано при создании .систем оператив-,. ной памяти вычислительных устройств, решающих информационно-логические задачи.

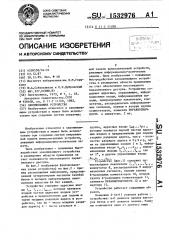

Цель изобретения — повышение быстродействия запоминающего устройства и расширение области применения за счет воэможности многомерного параллельного доступа, На фиг,l изображена функциональная схема устройства, на фиг.2 — пример расположения информации, представленной четырехмерным массивом 4х4х4х4 битов в четырех одноразрядных накопителях емкостью .64 бит каждый.

Устройство содержит адресные входы 1,, 1...,.1„ „ которые являются второй частью адресных входов устройства и предназначены для подачи m групп младших разрядов адреса в устройство, где km — число младших разрядов адреса, k — число разрядов в

2 ной памяти вычислительной устройств, решающих информационно-логические задачи. Цель изобретения — повышение быстродействия запоминающего устройства и расширение области применения

1 за счет обеспечения многомерного параллельного доступа. Устройство содержит адресные, управляющие, инфор". мационные входы, информационные выходы, одноразрядные накопители, коммутатор, распределитель информацион: ных сигналов, первую и вторую группы коммутаторов, элементы НЕРАВНОЗНАЧНОСТЬ и инверторы, 2 ил, группе, адресные входы 1я ...1 г, которые являются первой частью адресных входов и предназначены для подачи l старших разрядов адреса, где р - количество. разрядоа адреса и 0 - k

k-разрядных коммутаторов 10, вторую группу k-разрядных коммутаторов 11, элементы НЕРАВНОЗНАЧНОСТЬ 12 и инверторы 13.

Устройство работает следующим образом.

Возможны 2 ° (m+1) режимов работы . устройства: m+1 режимов записи векторов битов и к+1 режимов чтения. Режи1, мы отличаются один от другого лишь .

1532976 комбинацияии управляющих сигналов на входе 3 ° определяющем чтение или запись информации следует произвести, и на входах 60,6 )...6„,,, определяющих координатное направление век5 . тора битов, поэтому для уяснения принципа работы устройства достаточно рассмотреть чтение, запись каких-либо векторов битов по двум различным координатам, Описивая работу устройства, входную информацию будем представлять в виде последовательности иэ (в+1) мернЫх кубов, состоящих из информационных элементов (битов) ° Рассмотрим расположение одного (нулевого) (m+1)мерного куба в запоминающем устройстве, так как расположение остальных (оп+1)-мерных кубов будет периодичес20 кИ повторять расположение нулевого (оп+1)-мерного куба.

Введем координаты бита в (m+1)-мер- ном информационном кубе x»x, )... х„ а также координаты элемента в заломи- 25 нающем устройстве у,, у, где у, номер одноразрядного накопителя„ у адрес элемента в одноразрядном накопителе, 0(х,(2" -1; 0 =уф2"-1

О уф Л

ЗО

Для обеспечения возможности многоМерного доступа к векторам битов по различным координатам необходимо, чтобы координаты битов преобразовались по следующему закону:

35 у1 =х ) О х О ° e ° (1) а

K 2к еп хо+х< 2 +ха 2 +...х1 2 1

2к )) (2) где 9 — операция поразрядного суммирования

ent; (.. .1 - целая часть числа, Формула (1) реализуется: часть - 45 иа элементах НЕРАВНОЗНАЧНОСТЬ 12 и часть .- на распределителе 9 информационных сигналов, Формулу (2) в двоичном исчислении можно пРедставить в виде Ур (х, -) х - 50 ...х, ), где х; — двоичный код соответствующей координаты, младшие разряды находятся слева; - — операция конкатенации.

Если необходимо записать или счи- 55 тать вектор битов по.координате хо, то есть х,=О)1«2)...,? -1> а х,,х ., ° «х заданы постоянными, то íà ад(Х)-ъ X g а ° ° Х ) — ъ у< 9 х +

9 ...х;», ®х,®х;+, (+)хщ-) х; х ) При этом на управляющие входы распределителя 9 информационных сигналов с выходов элементов НЕРАВНОЗНАЧНОСТЬ 12 подается двоичный код

SÄ, Е ...,Е,Е;„О... „

Распределитель 9 информационных сигналов осуществит перестановку бит1 информации при записи и чтении согласно прямому .и обратному преобразованиям: к х; О)1) а «.,2 -1, к

У1 ««0) ° ° ° ° ) ) у, S> ®х;, S) ® yti ресные входь1 второй части адресных входов необходимо подать двоичный код: у =(х,- x -) ...,х ), при этом х, в двоичном коде подается на адресные входы нулевой группы адресных входов одноразрядных накопителей, х в двоичном коде — ца адресные входы первой группы адресных входов одноразрядных накопителей и так далее до х, которая в двоичном коде подается на адресные входы (ш-1)-й группы адресных входов одноразрядных накопителей, При этом на управляющие входы распределителя 9 информационных сигналов с выходов элементов НЕРАВНОЗНАЧНОСТЬ 12 подается двоичный код Я, х„ {+) х (9 ...х, а распределитель информационных сигналов реализует перестановку бит инфориации согласно формуле у, S 9 х, где х> 0,1,2..., 2"-1 то есть в накопитель с номером у) поступит бит с информационного входа устройства с номером х,(х, 0 21-1 ) при ааписи информации и на информационный выход устройства с но" мером х; поступит бит, считанный из накопителя.с номером у,(у,**О(2"-1)) при чтении, согласно обратному„прерб" разованию х =Б 9 у,, где у 0,1,2 ° ...(2"-1) °

Если же необходимо считать или записать вектор битов по любой„крординате х, где 11)2) ..л) х1=0,1,2,...

)К

2 -1) а х ) х1)...х 1 )х °, ). ° .хя заданы постоянными, то на адресные входы, второй части адресных входов одноразрядных накопителей подается двоичный код. 15329 где в качестве номеров разрядов информационных входов и выходов соответственно устройства будет выступать х °

Так как О у, « 2"-1, то операцию

S Q+ у можно заменить разрядной инс версией тех разрядов двоичного кода

SI, в которых двоичный код у имеет единицы. Это осуществляется с помощью 10 инверторов 13, Логический адрес. вектора бит ука- зывается двумя кодами, определяющими номер (m+1)-мерного куба, в котором

I расположен данный вектор (код 1, ) и 15 код начального элемента в (m+1)-мерном кубе (I. ), причем младшие m-1 разрядов физического адреса, поступающие на входы )о...,l„„,,, и являются кодом начального элемента ()." ) в 20 (m+1)-мерном кубе, а код L равен коду старших разрядов адреса на входах

1 . l

eg > " Р

Рассмотрим работу устройства в двух режимах при k=?, m=3. 25

Режим первый. Запись вектора бит с координатами начального элемента в двоичном коде х,=/01/, хг=/11/з хз=

=/11/, то есть L = /Ol/, /11/, /Il/, а хб=/00/; /)О/; /01/; /11/; L =О! 30

Аззго э Аззгл, Аззгг Аззаз (А хзхгх(хо)

Код на управляющих входах 6»6,, 6 равен /OOG/. На адресные входы 1,, у 11 Iз ° 1 . )з поступает код

/011111/, на адресные входы 4,...1 -1 35 код /00...0/, На информационные входы 4» 4,, 4, 4з поступает информационное слово A»zo А,зг< А ззгг Аэзг» з которое по сигналу "Запись: на входе

3 через коммутатор 8 поступает на рас-4О пределитель 9 информационных сигналов.

Распределитель 9 информационных сигналов под воздействием кода Sq--Ol поступившего на его управляющие входы 45 с выходов элементов НЕРАВНОЗНАЧНОСТЬ

1?о, 12,, производит перестановку бит информационного слова:

Аззгг A эзи А ззго Аэъг1 э

50 которые по сигналу "Запись" на входах

2, 3 будут записаны в одноразрядные накопители 7, При этом, поскольку сигнал на входах 6,, 6,, 6 равен нулю, то адрес на адресные входы накопи-55 телей 7,, 7,...,7„, проходит без изменения через k-разрядные коммутаторы первой группы IO и второй группы

11 k-разрядных коммутаторов.

76 6

Таким образом, бит А з . запишется в накопитель 7 по адресу у

=/0l 1111/=62, бит А >qzq — в накопитель 7 по адресу у /011111/=62, бит

A — в накопитель 7г по адресу у =/01 l I l I/=62, бит А ззд — в накопитель 7 по адресу у =/0)11)1/=62 °

Режим второй, Чтение вектора бит с координатами начального адреса в дво-, ичном коде х /01/ ° х =/ll/ ° х1 /)1/з то есть L =/01) I И/, а х /00/> /10/, /OI/, /l1/; Li a0:

АзогзАз,gg Азггз Азггъ

Код на управляющих входах 6, 6, 6 равен /010/, На адресные входы 1 » 1:, 1, 1, 1, 1 поступает код /01)lll/ ° на адресные входы 1 ...,,)p (- код.

/О, О/, на управляющие входы 2, 3сигнал, соответствующий режиму "Чтение".

Сигнал на входах 6, 6 равен нулю, следовательно, содержимое нулевой и второй групп адресных входовустРойства на адресные входы нулевой и второй групп адресных входов накопителей 7 пройдет беэ изменения через k-разрядные коммутаторы

10, 10г, l l о, 1)г, На адресные входы второй группы ,адресных входов накопителей 7 через

k-разрядные коммутаторы 10 11, пройдет содержимое их вторых информационных входов, так как управляющий сигнал на входе 6 равен единице.

На вторые информационные входы

k-разрядного коммутатора 10 с выходов элементов НЕРАВНОЗНАЧНОСТЬ 12 подается код Sz-=х Э х О+ хз=01, а на вторые информационные входы k-разрядного коммутатора 11, с выходов ин- верторов 13 подается код S =10.

Таким образом, на адресные входы одноразрядных накопителей 7 подаются следующие коды: (у ) Нако- Код питель

О 7о 0101) 1

9 71 011111

2 7г 018011

3 7 011011

Адрес (уз ) 58

62

1

По сигналу "Чтение" на управляющих входах 2 и 3 биты с определенными адресами поступают на выход соответствующих накопителей и, проходя че1532976 рез коммутатор 8, образуют на входе распределителя 9 информационных сигналов информационное слово:

A zz» А3з з в АЗом в Амаь

Распределитель 9 информационных сигналов под воздействием кода 8 01 поступившего на его управляющие входы с выходов элементов НЕРАВНОЗНАЧHOCTb 12, производит перестановку эле ментов информационного слова: А®, ),, А,, А ><3, которые появят-„ ся на информационных выходах 5, 5<, 5, 5, устройства (фиг. 1, 2) .

Формула изобретения

Запоминающее устройство, содержа- 20 щее одноразрядные накопители, входы обращения которых объединены и являются входом обращения устройства, ад1 енсые входы старших разрядов одноразрядных накопителей объединены и являются адресными входами лервой группы устройства, распределитель информационных сигналов и коммутатор, Информационные входы первой группы которого соединены с соответствующи- 30 ми выходами одноразрядных накопителей, информационные входы второй группы коммутатора являются информационны" ми входами устройства, управляющий вход коммутатора соединен с входами запись " чтение одноразрядных накопителей и является входом записи чтения устройства, выходы коммутатора соединены с информационными входами распределителя информационных сигналов, выходы которого соединены с информационными входами одноразрядных накопителей и являются информационными выходами устройства, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия устройства и расширения области его применения за счет организации многомерного параллельного доступа, в него введены две группы коммутаторов, группа элементов

НЕРАВНОЗНАЧНОСТЬ и группа инверторов, управляющие входы коммутаторов первой и второй групп объединены и являются соответствующими входами задания режима устройства, информационные входы первой группы коммутаторов первой и второй групп .объединены и являются адресными входами второй группы устройства, входы элементов НЕРАВНОЗНАЧНОСТЬ соединены с первыми информационными входами соответствующих коммутаторов первой и второй групп, выходы элементов НЕРАВНОЗНАЧНОСТЬ соединены с информационными входами второй группы коммутаторов первой группы и с соответствующими входами группы инверторов, выходы которых соединены с информационными входами второй группы коммутаторов второй группы, выходы коммутаторов первой и второй групп соединены с соответствующими адресными входами младших разрядов одноразрядных накопителей °

) 532976

1532976

Ф

О1 агг

DDD а и а

1И1 а

1 fZ а а юо т

d d

1 а12 ю а

1dd ЮМ

d а

Ж2 f131

l2 1 а а

ОЯ1 l

d т а

Not ао..а

ИИ г1

2110

212Ю г 21 и и1 а аю а г

Н

Составитель N.Ñû÷åí

Редактор А.Маковская Техред g.дидык Корректор И.Муска

Закаэ 8!05/56

Тираж 558

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1l3035, Москва, Н(-35, Раушская наб., д. 4/5

Проиэводственно-иэдательский комбинат "Патент", r.Óæãîðoä, ул. Гагарина, 101

Ф1

ФЛ а а а а ао яю D а и ии а И ю а а а

@11 lf Ю dF1? 0811 а

d d d а а а

21ал uznez1 а а а а а а а ю ом аэ z агм ю

21DD yD

2111

212