Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано в регистрирующей электронной аппаратуре для измерения аналоговых сигналов. Цель изобретения - уменьшение аппаратт-ix средств. Поставпенная цель достигается введением первого и второго триггеров управления записью, триггера управления чтением, элемента И, триггера определения чет-нечет и формирователя сигналов, а также тем, что матричный накопитель выполнен на ячейках аналоговой памяти с двойной блокировкой информации по входу и двойной выборкой по выходу и разделен на две подматрицы, причем ячейка аналоговой памяти содержит входные ключи, ключ сброса, накопительный элемент на конденсаторе, ттоковые повторители, выходные ключи и генератор тока, 2 э.п. ф-лы, 2 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„ 535232 А 1 (51) 5 Г 11 С 27/On

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H ABTOPCHOMV СВИДЕТЕЛЬСТВУ

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, может быть использовано в регистрирующей электронной аппаратуре для измерения аналоговых сигналов.

Целз изобретения - уменьщение аппаратных средств.

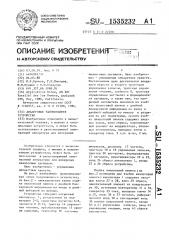

На фнг.1 изображена функциональная oõeìa прелложенцого устройства; на фиг.2 — электриче<..кал схема ячейки аналоговой памяти с двойной блокировкой информации на входе и двойной выборкой на ззиходе, Устройс rno солержит матричньп сзс1копителE> 1 > P<< .злелеHIEEiEEE EEа вод матрицы 2-5, сднигоные регистры 6-8, элементы tt 9-13, триггер )4 управления чтением> преобразователь 15 уровня СИ ГисЗЛОН > ГЕ НЕ р а ТО р 1 6 E a VTAT1hEX

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (46) 07,09.91. Бюл. Р 33 (21) 4404095/?4 (22) 04.04.88 (72) И, Б. Буянзин, Г, П, 11ак аров >

Ю,Н.Пунжнн н В.П.Токарчук (53) 681 . 3? 7 . 66 (088. 8) (56) AppliE ati on Notes, AN 201

Parallel Лпе los ttemory, Analutek

LTD, 11ау> 1986, California, Авторское свидетельство СССР

1t> 1196957, кл. G 11 С 27/00, 1984.

1 (54 ) АНАЛОГОВОЕ ЭАПОИИН А10И! ЕЕ

УСТРОЙГТВО (57) Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано зз регистрирующей электронной аппаратуре для измерения аналоготзых сигналов. Цель изобретения — уменьшение аппаратных средств.

Поставленная цель достигается введением первсго и второго триггеров управления записью, триггера управления чтением, элемента П, триггера определения чет-нечет и формирователя сигналов, а также тем, что матричный накопитель выполнен на ячейках аналоговой памяти с двойной блокировкой информации по входу и двойной выборкой по выходу и разделен на дне подматрицы, нричем ячейка аналоговой памяти содержит входные клю ш> ключ сброса, накопительный элемент на козщенсаторе> пзтоковые повторители, выходные ключи и генератор тока, 2 э,п, ф-ли, 2 ил. импульсов, делитель 17 частоты, триггеры 18 и 19 управления записью, триггер 20 чет-нечет, формирователь

21 сигналов, мультиплексоры 22 и 23, вход 24 сброса накопителя 1, входы

25 и 26 сброса устройства.

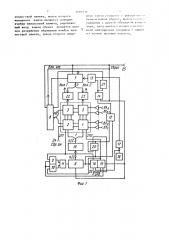

Ячейка аналоговой памяти (на фиг,2 приведены две ячейки аналоговой памяти ) накопителя 1 содержит входные ключи 27 и 28, ключ 29 сброса> накопительный элемент на конденсаторе 30, истоковые повторители 31 и 32, р генератор 33 тока, выходные ключи 34 и 35, щины 36 и 37 питания, информаEEEEnEEEE»Eit вход 38 и тактирующий вход

39 ячейки аналоговой памяти, входы

40 и 41 управпения записью, вход 42 управления чтением, вход 43 сброся накопит>п>з.

1 5357:32

Устр й< тно рлботлет <.ледунняим обрлз< и. Перед tt t tллoм рлботьt подают си<.нлл ебросл r нходл 25 нл триггеры 18 и 19 и сднигоные регистры 6-8

5 чтобы привести их н исходное состояни<, н выполняют аналоговый сброс ячеек плмяти млтричного накопителя 1 через параллельные ключи 29 (фиг. 2) .

В режиме записи входные аналоговые сигнллы положительной полярности поступают нл и-входы. По сигнллу записи нключлется триггер 18 (ЗП1), который рлзблокирует n > n/2 затворов трлнзисторон ключей 28 (строк) и рлзрешлет сдниговому регистру 6 через преобрлзонлтель 15 стробиронлть значение п входных аналоговых сигиллон. В момент перпого такта в п ячеек первой строки, открывая ключи 27 временного стробирования днух соседних ячеек столбцов, записывают первые знлчения и аналогоных сигналов. Пропесс записи продолжается тлким образом ил п/2 тактов, запоминая n < n/2 значений аналоговых сигналов ° По заднему фронту n/2 такта включается триггер 19 (ЗП2) и происходит дальнеttlltee стробировлние эле" мецтон строк с n/2+! до п. В накопитель 1 злписыва<отся n ° п значений лнллого.tbtx сигнллон. После n -ro тактл включаются триггеры 18 и 19, и устройство переходит н режим хранения. П1:t этом все ключи накопителя 1 з:.:рыты. Режим чтения аналоговой и;;формации происходит только по окончл.<пи режимон записи и хранения. В эом режиме включают триггер 14 и подлют сигнал старт" на входы пер< ных триггеров регистров 7 и 8 с формирователя 21. Поделенная тактоная частота с делителя 17 устанавливает первые триггеры н состояния "1" регистров 7 и 8. Прн этом считывают первые две аналоговые ячейки памяти, принадлежащие первой стррке и перным двум соседним столбцам (1 и 2) и подмлтрицам 2, 3 и 4, 5.

Под действием тактовой частоты сднигоный регистр 7 стробирует последующие строки двух соседних столбцов (1 и 2 1, с которых аналоговая информация поступает на выходы (ных.1 и ных.2) соответстненно, CJlRHloBblA регистр 7 стробирует и строк двух соседних столбцов за и тлктов. По заднему фронту и-го тактового импуэ<ьсл сднигоный регистр 8 переключа<. Tc ft нл « еду<ощую пару gyttyx срседних столбцов. Таким образок, полное считья<лние аналоговой информации с матричного про исходит эл и ° n/2 тактов, л сднигоный регистр 8 содержит в дна раза меньшее число элементов. По окончании режима чтения устройство снова приходит и режим хранения, из которого можно опять начать запись аналоговой информации или ее чтение.

Введение новых элементов, разделение накопителя на подматрицы, реализация устройства на ячейках с двойной бл жировкой по входу иднойной выборкой по выходу и ннод дополнительных элементов позволяет сократить число элементов в функциональнь<х узлах уполнления, что, в свою о ередь, упрощает узлы управления, совершенствует топологию матричного иакоп1<теля нл кристалле, уменьшает размеры крис галла и повь<шает скорость считывания аналогoRbtx сигналов. Использование описанного устройства в многоканальных системах пропорциональных и дрейфовых камер позволяет получить следующие преимущества: низкую стоимость канала изме» рений аналогоных сигналов, высокую плотность компоновки блоков измерений, сокращение аналого-цифровых преобразователей при тех же разрешающей способности и динамическом диапазоне измерений значений амплитуд аналоговых сигналов в цифре.

Формула изобретения

1, Аналогово е запоминающе е устройство, содержащее матричный накопитель, информационные входы столбцов котороro являются информационными входами устройства, преобразователь уровня сигналов, выходы которого соединены с тактирующими нходамн матричного накопителя, первый сднигоный регистр, первый выход которого соединен с входом преобразователя уровня сигыалов, первый и второй элементы И, первые входы которых соединеньг с выходом генератора тактовых импульсон, третий элемент И, входы которого соединены с выходами первого и второго элементов И, выход третьего элемента И соединен с тактирующим входом первого сдвигового регистра, второй сдннгоный регистр,,»1)й 1!::пд к<этор(?(п «.< )и(1(11 «

1 ° 3 . (2 )<)

Рп(п .)TIP(!PI(1 A 1(< I(I(3(A)t С TIPpt)t It! ;и ();1 н!(. (н)пи(1,и Tlxi!Ii <11111 (T < P)1() 1 и и н то()О—

I с»!Ул).тип!!< 1«? Ор<) 1) ) 1» тле ртый )лс) (ент (f 11!>(ХОД К() ТОРО 1 П (П> )(Ил (ll Г Иl(фОРМЯ

5 !

,)1> )!!НЫМ (ЗХОЦ(?1! () TOPO t Î С ДНИ ГО НОГО регистра, делитель «;(< тоты, выход которого соединен с перным входом (етнертого .)лемеитя И. иифс рманион-! ((,!н нходы мультиплексор<)н соединены с 1» Ixor(A)ffr матричис Гп (; копите(:я, тр< f (fit сднигоный ре(истр, информационный f)x(д которого соединен с

РТОРЬIМ Р(TXO+0)f f) POPOÃÎ СДНИ ГОВО ГО

1)< Ги< Tpа ) РхОДы сбрОс а сДРи Г<)пых 15

pPI lfCTpOI3 ОбЪ<)д11(<Г(!Н ll (If!(I>II()TCH пе(1Ti1)t! Рхпдом < О(О(а устр(й-тла, выходы

r ×Jftt PÈÏJiPt<ÑOf),Н >)-(ЧЮТ(Ч >!)>ХС)даМИ ус тройстна, )11:;,пь(1 (тьс го сp(1)III.оаоГО РЕГ>i< ТРЯ С< . ЦИ((Е(П> с Г)нпЛАМИ СТРОК )Р

1! (ТПИ IIIOI O ИАК< Л<(Т< 1(», !)>11(<?Д ГЕ((Е— рлтпр1 тактoT)b(x T)t (Г !Il (. >(с()е-(инеи () )«)ло)! де лит< и >(А < TOT! ) T)xoJT, < ()P()(Л f;O POPO f О Sf! >:" < ТС 11 РХОД>))! сброся И<(колите>()(, о т л и ч а ю — 25 щ е е с я те)1, что, с це.л(,ю упрощ<—

II!fff, и него ннг цен),(дРА триггера управления 1апи<. ),ю, триггер управления чтением, пят) (й P)IP)!e)11 И, тригГЕр ОПрЕДЕ(1(33()1>(ЧЕТ-(TP Е г и форин- 3Г( ро(<) т T) I сиг(31л<г, 1 I.".;((К<) тс рс го

< ОПДИI(< И С Н-<ОД1) >1 уо TAÈ(?I)Ê(f ЕДИНИЦЫ

РТОРО(O И ТРС ) < . П С!! )S)> О))!(Х РЕГИСТ

1)п(>, llxoJ(ф<)1)), ;; . т! П)1 "и Г 1(элоп соР

1>1!)1! 11 «1;И(ХО(, П 1 >)1):. ". ) ) УПР<) НЛЕНИ((35 чтеи)(с (i и птп,)-()! v.. .ojgot; лет(<Арто го элп)!>з)(та И, пх<)ды <.Та((О>(ки нуля триггега уп()1)ч<.) л» чт и .!<.и и второго

ТP) ° ГГ)=PА Vtlс) а13П< ПИ>(1;111ITC >,t<) CОPП?3((PIII>t с нх ?Дом сбро< А Tfepf)of О слпиГпвОГО 4О г егистра, второй н)(ход которого сое,>)инеи Г иифор)(,1цио(13(11(1! лходами первого тригi-r pя управлении записью и триггера of1O< Деления -(ет- печет и с перл; (м Рходо(! пятого элемента И, пыход котоp< I <) (opJ(I()»(I с информационным пхсдом триг(сн ;лрянлени I чте— иием, в topol< лхсд пн1пг< зл.мента И

copmfIteI(г T)pr(«.. Гыхо»п)! и ииформаI(((of(Itsç!(! н () )и "> т(!)1! (.е()А <)(ll)i .,»

ЧЕ.(-И ЧС" Р, Нт:,(><) (".(,ХПД КОтОРОГП СОЕ-. дииси < 1.; :, ))н(rl: . (я(° пходом нторог О три г 1 (p;(. Tlp;)! i)! !>) Is! з А 1 (l ". 11(<) ) так ти" рующие Flx< ды три(1 ?1)пн .:пр (нл ния

)- 1()ИС Ь)<) (i)»,I(! («С (!(!/,ОДОМ < )(СР>>

55 тоРА; 11;т .:-»1;! и .I :!1, пн, 11;nfj Уста((онки IT>J(s 1;егн?Г< г, I .(еря у!)равле.

ИИЯ Заlп(<, «" Ч)>!1(!" > < !1 Г 1 . Р,1,"1 НХПДОМ сброся уст(;. (. н .. )) !I! Ихпд п..р-Р ХС)ДОМ У((Р ) 1)ЛГ(llt

2, У«тройстно ио и,1, о т л и ч а ю щ е р Г и т(м „чтО матр((чнь(й накопитель выполнен иа ячейках ((на)(огоно((памяти с двойной блокиp0(T(ь(, в первой из кото)ых распо.по?)(ено 31/2 ячеек аналоговой памяти, а по Рторой — и ячеек

Аналоговой пя((ят(3.

3. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что ячейка аналоговой памяти с двойной блокировкой информации на входе н двойной выборкой на выходе содержит входные клн)чи, ключ сброса, накопительный элемент иа конденсаторе, истоковые повторители, выходные ключи и генератор тОкА выход которого соединен с перв(,м входом питания первого исто(;оного повторителя, входы питания Генератора тока и второй и третий входы питания первого истокового повторителя соедиие(!ы с пшнами питания ячейки яиалоговой памяти, ииформационнь(й вход первого входного ключа является информационным входом ячейки аналоговой памяти, вход управления первого ключа является тактирующим входом ячейки аналоговой памяти, вьгход первого входного ключа соединен с информационным входом второго, управляющий вход которого является первым входом управления записью ячейки аналоговой памяти, выход второго входного кл(оча соеди-! (pl(с входом истокового повторителя и одной из обкладок конденсатора, другая обкладка которого соединена с одной из шин питания, выход первого истокового повторителя соединен с входом второго, выход которого соединен с информационными входами первого и второго выходных ключей, управляющие входы которьл(янллн тся входами управления «1 p«(t(!Tf !((())(t Î выходного кл)<)ча является выходом ячейки аналоговой памяти, упр<)вля))щий вход кл(<)ча сброса является вхо,дом разре!))ения.обращения ячейки аналоговой памяти, выход второго входтора, вход иитв 11 (вт<)роги ис T

В Х () (! ! !.(К (! 1<) ! В < 6 !! О

COE (tIIIt«t! C ДРУГ

< И В)!)(И )<

1535232

КРАИ

ЪП1

Редактор Г.Федотов

Корректор С.Черни

Заказ З723 - Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открьггиям при ГКНТ СССР

1130З5, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,101

Ti

Nf бх

1ф) Составитель Л,Амусьева

Текред М.Ходанич