Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода информации о состоянии двухпозиционных датчиков. Цель изобретения - повышение надежности устройства. Устройство содержит буферный регистр 2, коммутатор 3, дешифратор 4, счетчик 5, блок синхронизации 6, элемент задержки 7, блок сравнения 8, блок памяти 9. В цикле опроса адреса датчиков, изменивших свое состояние, заносятся в блок памяти 9. После опроса последнего датчика включается режим чтения адресов из блока памяти 9. После того, как все адреса, записанные в предыдущем цикле опроса в блок памяти 9, прочитаны, начинается новый цикл опроса. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 5 G 06 F 3/00

ОПИСАНИЕ . ИЗОБРЕТЕНИЯ

-«1t/Ñi

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

r1O ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4412478j24-24 (22) l9.04.88 (46) 15.01.90. Бвп..У 2 (72) А.А. Борисов и 1т.П. Паршин (53) 681. 327. 11 (088. 8) (5á) Авторское свидетельство СССР

У 1 285456, кл. G 06 F 3 700, 1 985.

Авторское свидетельство СССР

У 1201842, кл. G 06 F 13700, 1984. (54) УСТРОЙСТВО Д11Я ВВОДА ИНФОРИАЦИИ (57) Изобретение относится к автома-! тике и вычислительной технике и мо-, жет быть использовано для ввода информации о состоянии двухпозиционных

„„SU„„1536365 А 1

2, датчиков. Цель изобретения — повышение надежности устройства. Устройство содержит буферный регистр 2, коммутатор 3, дешифратор 4, счетчик 5, блок синхронизации 6, элемент задержки 7, блок сравнения 8, блок памяти

9. В цикле опроса адреса датчиков, изменивших свое состояние, заносятся в блок памяти 9. После опроса последнего датчика включается режим чтения адресов из блока памяти 9. После того, как все адреса, записанные в ттредыдущем цикле опроса в блок памяти

9- прочитаны, начинается новый цикл опроса. 1 s.ï. ф-лы, 2 ил.

1«36365

Изобретение относится к автоматике и -вычислительной технике и может использоваться дпя ввода информации о состоянии двухпозиционных датчиков в управляющие или вычислительные системы.

Цель изобретения — повышение надежности устройства.

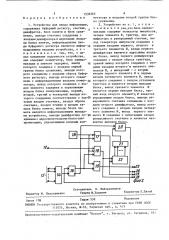

На фиг. 1 показана функциональная схема устройства1 на фиг. 2 — схема блока синхронизации.

Устройство соцержит информационные входы 1 устройства, буферный регистр

2, коммутатор 3, дешифратор 4, счет- 15 чик 5, блок 6 синхронизации,, элемент

7 задержки, блок 8 сравнения, блок 9 памяти, шифратор 10 и выходы устройства 11.

На фиг. 2 обозначены управпяющий 20

12 и адресные 13 входы блока 6 синхронизации, первый дешифратор 14,„ генератор 15 импульсов, триггер 16, элементы И 17-20, второй дешифратор

21, реверсивный счетчик 22, выходы 25

23-26 блока 6.

Устройство работает следующим образом.

Импульсы генератора 15 поступают 30 на входы элементов И 17-19. Срабатывает элемент И 19, на второй вход которого подан разрешающий сигнал с прямого выхода триггера 16 (установленный в единичное состояние по на чальному сбросу) . Вы.....дные импульсы элемента И 19 через первый выход 23 блока 6 подаются на вход счетчика 5, который формирует последовагельные адреса опрашиваемых датчиков. На ин- 40 формационные входы 1 устройства поступают, сигналы. с датчиков, по перед-ним фронтам сигналов возбужденных датчиков взводятся соответствующие триггеры буферного регистра 2. Дешифратор 4 последовательно подключает выходы триггеров буферного регистра 2 к выходу коммутатора и, следовательно, через управляющий вход 12 блока 6 к входу элемента И 1 8. Если подключенный выход триггера 2 находится в единичном состоянии, то на выходе коммутатора 3 имеется высокий потенциал, элемент И 18 вырабатывает сигнал, по которому реверсивный счетчик 22 уве- >5 личивает свое состояние, и в память

9 записывается адрес входного датчика, имеющего единичное состояние.

Процесс записи управляется сигна- лом, поступающим на вход записи блока

9 с четвертого выхода 26 блока 6.

Высокий потенцил с выхода коммутатора 3 через элемент задержки 7 подается также на входы бпока 8 сравнения. В соответствии с номером возбужденной шины дешифратора 4 сработает один из элементов блока 8 и сбрасывает адресуемый триггер буферного регистра 2 °

Таким образом, в течение цикла onроса в блок 9 последовательно запишутся адреса всех возбужденных входных датчиков.

Как только опрошен датчик с последним номером, то ц соответствии с набором нулей и единиц на входах 1 3 блока 6 дешифратор 14 выработает единичный потенциал, который установит триггер 16 в нулевое состояние, на входе элемента И 17 установится разрешающий сигнал . Импульсы с генератора 15 теперь подаются через элемент

И 17 на вычитающий вход реверсивного счетчика 22 и через третий выход 25 блока 6 — на вход чтения блока 9.

Адреса возбужденных датчиков последовательно считываются через шифратор 10 и выход 11 в управляющую вычислительную машину. Когда считан последний адреса, в реверсивном счетчике 22 установится нулевое состояние, по которому вьгкод дешифратор 21 примет единичное состояние, четвертый элемент

И 20 сработает и установит триггер 16 в единичное состояние, а счетчик адреса — в нулевое. ФГмпульсы с генератора 15 вновь подаются на счетный вход счетчика адреса 5 и повторится цикл опроса..

Если в цикле опроса не выявлено новых возбужденных состояний, датчиков, то элемент И 18 не выработает ни. одного импульса, реверсивный счетчик 22 останется в нулевом состоянии и сразу же после установки. триггера 16 в нулевое состояние сработает элемент И 20, переводя триггер 16 в единичное состояние, сработает элемент И 20, переводя триггер 16 в единичное состояние, счетчик адреса 5 — в нулевое °

Начинается новый цикл опроса, Таким образом, устройство обеспечивает опрос датчиков, формирование и передачу в управляющую вычислительную машину адресов датчиков, именивших свое состояние.

5 153636 изобретения

Формула иг2

Составитель В. Файз рахманов

Техред М. Ходанич Корректор Л.Патай

Редактор М. Недолуженко

Тираж 559 Подписное

Заказ 108

ВНИИПИ Государственного комитета по изобретениям и открытия р иям п и ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, . р

tt

r, Ужго од ул. Гагарина, 101

1 . Устройство для ввода информации, содержащее буферный регистр, счетчик, дешифратор, блок памяти и блок сравнения, выходы счетчика соединены с входами дешифратора и адресными входами блока памяти, информационные входы буферного регистра являются инфор- 1р мационными входами устройства, .о т— л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит коммутатор, блок синхронизации и элемент задержки, выход 15 которого соединен с входами первой группы блока сравнения, выходы которого соединены с входами сброса буферного регистра, выходы которого соединены с информационными входами комму- 20 татора, выход которого соединен с входом элемента задержки и управляющим входом блока синхронизации, первый, второй, третий и четвертый выходы которого соединены соответственно с так-25 товым входом счетчика, входом сброса счетчика, входом чтения и входом записи блока памяти, выходы блока памяти являются информационными выходами устройства, вьжоды дешифратора со- 3р единены с адресными входами блока синхрониз ации, управляющими входами ком5 6 мутатора и входами второй группы блока сравнения.

2. Устройство по п, 1, о т л и ч а ю щ е е с я тем,что блок синхронизации содержит генератор импульсов, четыре элемента И, триггер, два дешифратора и реверсивный счетчик, выход генератора импульсов соединен с первыми входами первого, второго и третьего элементов И, входы первого дешифратора являются адресными входами блока, выход первого дешифратора соединен с входом сброса триггера, прямой выход которого соединен с вторыми входами второго и третьего элементов И, а инверсный — с вторым входом первого элемента И и первым входом четвертого элемента И, выход которого соединен с входом установки триггера и является вторым .выходом блока, выход третьего элемента И является. первым выходом блока,. третий вход второго элемента И является управляющим входом блока, выходы реверсивного счетчика соединены с входами второго дешифратора, выход которого соединен с вторым входом четвертого элемента И, выход первого элемента И соединен с вычитающим входом реверсивного счетчика и является четвертым выходом блока,