Устройство для обмена информацией

Иллюстрации

Показать всеРеферат

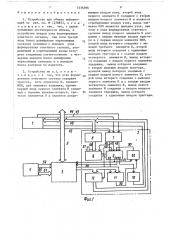

Изобретение относится к вычислительной технике и предназначено для обмена информацией между ЭВМ, имеющей общую магистраль с совмещенными шинами "Адрес/Данные", и периферийными устройствами. Целью изобретения является повышение достоверности обмена. Устройство содержит блок ввода-вывода, блок дешифрации управляющих сигналов, селектор адреса, магистральный приемник адреса, узел магистральных приемников сигналов управления, узел формирования ответного сигнала, магистральный передатчик данных, блок контроля по паритету, магистральный передатчик квитанции. 1 з.п. ф-лы, 7 ил.

СОЮЗ СОВЕтСНИХ социАлистичесних

РЕСПУВЛИН..SU„„1536395 А 2 (51)5 С 06 Р 13 1

* (ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМЪ СВИДЕТЕЛЬСТВУ

1, интерфейсное устройство 2, блок С

3 ввода — вывода, периферийное устройство 4, шины 5 .общей информационной магистрали, магистральный прием- laeaL ник 6 адреса данных, узел 7 ма- СЛ гистральных приемников сигналов СФ управления, селектор 8 адреса, блок

9 дешифрации управляющих сигналов, р магистральный передатчик 10 квитанции, блок 11 контроля по паритету, магистральный передатчик 12 данных, схему 3 сравнения, элемент И 14, элемент 15 задержки, элемент 16 сложения по модулю два, элементы И 17, 18, элементы ИЛИ 19, 20, элемент

НЕ 21, триггер 22, элементы И 23-25, элементы 26-28 задержки, элемент )

ИЛИ 29, узел. 30 формирования контрольного разряда, схемы 31 сравнения, элемент И 32, магистральный приемник 33, узел 34 формирования конт рольного разряда, мультиплексор 35, ГОСУДАРСТВЕННЫЙ НОМИТЕТ

Ilo изоБРетениям и ОТНРытиям

ПРИ ГННт СССР (e» 1278872 (21) 4408553/24-24 (22) 12.04.88 (46) 15,01.90. Бюл. № 2 (72) Б.А.Фураш, А.К.Вавилов и П.И.Крупецкая (53) 681.325 (088.8) (56) Авторское свидетельство СССР

И 1278872, кл. С 06 F 13/14, 1985. (54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ (57) Изобретение относится к вычислительной технике и предназначено для обмена информацией между ЗВМ, Изобретение относится к вычислительной технике, предназначено для обмена информацией между ЭВМ, имеющей общую магистраль с совмещенными шинами "Адрес/Данные", и периферийными устройствами, касается усовершенствования известного устройства по авт, св. № 1278872, Целью изобретения является повышение достоверности обмена, На фиг.1 представлена структурная схема устройства; на фиг.2-6 — функциональные схемы селектора адреса, схемы сравнения селектора адреса, блока дешифрации управляющих сигналов, блока контроля по паритету и блока ввода — вывода; на фиг.7-приведен пример возможной реализации узла формирования ответного сигнала.

Устройство для обмена информацией содержит центральный процессор

2 имеющей общую магистраль с совмещенными шинами "Адрес/Данные", и периферийными устройствами. Целью изобретения является повышение достоверности обмена. Устройство содержит блок ввода.†.вывода, блок дешифрации управляющих сигналов, селектор адреса, магистральный приемник адреса, узел магистралях приемников сигналов управления, узел формирования ответного сигнала, магистральный передатчик данных, блок контроля по паритету, магистральный передатчик квитанции.

1 з и ф-лы 7 ил.

1536395 буферный регистр 36, коммутатор 37 данных, элемент..38 задержки, элементы ИЛИ 39, 40, узел 41 элементов

И, цепи; квитанции выставленного про цессором адреса устройства или ячейки памяти (цепь 42) ОБМ (" Обмен" ); запроса на чтение данных (цепь 43)

ДЧТ (" Данные читать"); квитанции записываемых данных (цепь 44) ДЗП ,("Данные записать"); квитанции вво:димых в процессор данных или сигнала о завершении операции записи от адресованного устройства (цепь 45)

ОТВ "Ответ"; сигнала ОБМ (цепь 46) с выхода магистрального приемника; ! . сигнала ДЧТ (цепь 47) с выхода ма-. гистрального приемника; сигнала ДЗП (цепь 48) с выхода магистрального приемника; сигнала разрешения работы устройства (цепь 49); сигнала паритета (цепь 50)> сигнала ОТВ (цепь 51) на магистральный передатчик; сигнала стробирования передатчика данных (цепь 52); сигнала ст1 обирования конт- 5 роля по паритету (цепь 53); сигнала стробирования блока ввода — вывода при чтении от интерфейсного устройства (цепь 54.); сигнала стробирования блока ввода — вывода при записи от интерфейсного устройства (цепь

55); магистраль 56 данных из блока ввода — вывода, шину 57 прошитого кода адреса устройства ввода/вывода, шину 58 кода адреса устройства вво-

35 да — вывода с выхода магистрального приемника, цепь 59 сигнала стробирования блока ввода — вывода при чтении от периферийного устройства; цепь 60 сигнала стробирования блока

40 ввода — вывода при записи от периферийного устройства; шину 61 данных периферийного устройства; узел 62 формирования;ответного сигнала (ОТВ) содержащий элементы..И 63-67, Ф

45 элемент ИЛИ 68, триггер 69, элементы

70, 71 задержки.

Функциональное назначение и конструктивное выполнение. входящих блоков (фиг.2-6) аналогично их назначению и выполнению в прототипе.

Узел 62, предназначенный для формирования и управления сигнллами

ОТВ, работает следующим образом, При наличии сигнала по цепи 50

"Паритет" сигнал по цепи 54 »Pазрешение чтения" формирует на выходах элементов И 64 и ИЛИ 68 сигнал аналогичной формы.

При отсутствии сигнала по цепи

50 сигнал по цепи 54 формирует соответствующий сигнал на выходе элемен- та И 63. При этом в первом цикле поступления сигнала "Разрешение чтения" триггер 69 в нулевом состоянии закрывает элемент И 67 и открывает элемент И 65, По окончании сигнала по цепи 54 с выхода элемента 70 задержки, длительность которого равна длительности сигнала по цепи 54, устанавливается в единичное состояние триггер 69, который закрывает элемент И 65 и открывает элемент И

66, после чего узел *62 ожидает поступления следующего сигнала по цепи 54. Во втором цикле сигнала по цепи 54 он проходит через элементы

И (i7 и 68, в результате чего формируется сигнал по цепи 50 на выходе узла 62, Одновременно сигнал по цепи 54 проходит через элемент И 66 и после задержки на элементе 71 задержки на длительность сигнала по цепи

54 сбрасывает триггер 69, который вновь запирает элемент И 67 и подготавливает свою установку через элемент И 65 в следующем цикле сигналов по цепи 54.

Устройство работает следующим образом, Процессор 1, установив на шинах

5 код адреса, активизирует цепь 42 сигнала ОБМ, который с выхода блока

7 стробирует селектор 8 адреса, в котором происходит сравнение кода адреса шин 5 с выхода магистрального приемника 6 и кода адреса блока 3 ввода — вывода, прошитого на первом входе 57 селектора 8адреса, При совпаденни всех разрядов активизируется выход по цепи 49 селектора 8 адреса, который устанавливает триггер 22, что означает выбор данного блока 3.

При несовпадении адресов устройство остается в исходном состоянии. Дальнейшее функционирование устройства при совпадении адресов разбивается на два режима: записи (вывод данных из процессора 1 в блок 3 ) и чтения (ввод данных в процессор 1 из блока 3)

В режиме записи процессор 1 устанавливает на шине 5 данные, а на цепи 44 — сигнал ДЗП, который с выхода узла 7 активизирует блок 9 дешифрации управляющих сигналов, который вырабатывает строб по цепи 55 для блока 3 ввода — вывода и сигнал

95 6

5 15363 по цепи ОТВ 51 для ЦП, задержанный относительно него на элементе 28 задержки. В ответ на строб по цепи

55 блок 3 ввода — вывода формирует

5 в узле 34 контрольный разряд для слова с выхода магистрального приемника 33 и после задержки элементом

38 задержки переключает мультиплексор

35 и открывает для записи буферный 10 регистр 36. Таким образом, в буферный регистр 36 будет записано с шин 5 слово данных с контрольными разрядами, а ЦП, получив сигнал ОТВ, снимает сигнал ОБМ, чем обеспечивается приведение устройства в исходное положение.

В режиме чтения процессор 1 устанавливает сигнал ДЧТ по цепи 43, который с выхода узла 7 активизирует 2р блок 9 дешифрации управляющих сигналов, который вырабатывает строб по цепи 54 для блока 3 ввода — вывода, переключающий коммутатор 37 и откры- . вающий буферный регистр 36 для чте- 25 ния, Данные из буферного регистра

36 через коммутатор 37 поступают на входы блока 11 и магистрального передатчика 12. Сигнал по цепи 53, задержанный элементом 26 задержки отно- Зр сительно сигнала по цепи 54 на время, необходимое блоку 3 для выдачи данных из буферного регистра 36, разрешает работу блока 11, формирующего контрольный разряд и сравни 35 вающего его с контрольным разрядом, считанным из буферного регистра ° При отсутствии ошибки в запрещенных процессором I данных на выходе блока

11 по цепи 50 вырабатывается сигнал, проходящий без изменения через узел

62 на вход элемента И 25 блока 9 дешифрации управляющих сигналов. На другой вход элемента И 25 подается сигнал с выхода элемента И 23, за- 4> держанный элементами 26 и 27 задержки на время, необходимое для работы блока 11. При этом в блоке 9 формируется сигнал по цепи 52, стробирующий передатчик 21 для выдачи данных на магистраль, и сигнал по цепи ОТВ

5l для ЦП. Таким образом, процессор

1 получает сигнал ОТВ как квитанцию вводимых данных, установленных на шинах 5 общей магистрали. Считав данные, процессор 1 завершает режим аналогично режиму записи.

При сбое, если сигнал контроля по паритету по цепи 50 по каким-либо причинам не формируется, в текущем цикле чтения узел 62 на выходе по цепи 50 сигнала не формирует, следовательно, в блоке 9 дешифрации управляющих сигналов сигнал ОТВ по цепи

51 не формируется, данные на магистраль не выдаются (сигнал по цепи

52 не сбрасывается), Процессор 1, не получив сигнала

ОТВ, в течение 10 мкс, переходит на стандартную процедуру обработки прерывания, Дпя установления наличия устойчивого или случайного сбоя и локализации неисправности процессор может выполнить процедуру записи— чтения и поразрядного сравнения контрольного слова, При этом функционирование узла 62 рассматривается для двух режимов: режима случайного сбоя и режима устойчивого сбоя.

Если при повторной операции чтения сигнал контроля по паритету по цепи 50 формируется (режим случайного сбоя) узел 62 также формиl рует выходной сигнал по цепи 50 (переходя при этом в исходное состояние). Выполнив еще несколько раз операцию чтения контрольного слова, процессор может установить факт случайного сбоя и перейти к выполнению прерванной программы.

Если при повторной операции чтения контрольного слова сигнал контроля по паритету по цепи 50 вновь не формируется. (устойчивый сбой), то узел 62 аппаратно формирует выходной сигнал по цепи 50 каждую вторую операцию чтения, давая возможность блоку 9 дешифрации управляющих сигналов сформировать сигнал по цепи 51 ОТВ и сигнал по цепи для стробирования передатчика данных. При этом факт устойчивого сбоя процессор 1 может установить по невозможности выполнения каждой второй операции чтения. По резуль-. татам сравнения при устойчивом искажении одного или нескольких бит контрольного слова устанавливается факт неисправности тракта передачи при чтении этого слова, при отсутствии искажений — неисправности блока 9 дешифрации сигналов управления, блока 11 контроля по паритету, цепи управления этих блоков, элементы и цепи управления блока 3 ввода вы- вода.

1536395

Формула изобретения

1. Устройство для обмена информацией по авт. св. Р 12788/7, о т л и. ч а ю щ е е с. я тем, что, с целью

5 повышения достоверности обмена, в устройство введен узел формирования ответного сигнала, при этом третий вход блока дешифрации управляющих сигналов соединен с выходом узла формирования ответного сигнала, разрешающий и стробирующий входы кото1 рого соединены соответственно с четвертым выходом блока дешифрации 15 управляющих сигналов и с выходом блока контроля по паритету.

2. Устройство по и,. 1, о т л и— ч а ю щ е е с я тем, что узел форми- 2О рования ответного сигнала содержит триггер, пять элементов И, элемент

ИЛИ, два элемента задержки, причем первый вход первого элемента И соединен с первыми входами,второго, тре- 25 тьего элементов И и является разрешающим входом узла, второй вход первого элемента И соединен с вторым входом второго элемента И и является стробирующим входом узла, выход элемента ИЛИ является выходом узла, при этом в узле формирования ответного сигнала выход второго элемента И соединен с первым нулевым входом триггера и с первым входом элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И,.второй вход которого соединен с единичным выходом триггера и с первым входом четвертого элемента И, выход которо"о соединен с входом первого элемента задержки, выход которого соединен с вторым нулевым входом триггера, нулевой выход которого соединен с первым входом пятого элемента И, вто" рой вход которого соединен с выходом первого элемента И и с вторым входом четвертого элемента И, выход пятого элемента И соединен с входом второго элемента задержки, выход которого соединен с единичным входом триггера.

57 ЯЧ6

)53б395

1536395

Фиг, б

Фиг. 7

Составитель С,Пестмал

Редактор А.Маковская Техред М.Ходанйч Корректор Т.Малец

Заказ 110 Тираж 555 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101