Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах обработки информации. Целью изобретения является повышение быстродействия устройства. Устройство содержит первый и второй блоки памяти, выходы которых соединены с информационными входами коммутатора, выходы которого являются выходами старшего и младшего полуслов устройства, блок инкрементирования адреса, управляющий вход которого подключен к управляющему входу устройства и является младшим адресным входом устройства, адресные входы первого блока памяти соединены с выходами блока инкрементирования адреса, информационные входы которого подключены к адресным входам второго блока памяти и являются старшими адресными входами устройства. В устройстве обспечивается выборка слов за один цикл обращения к блокам памяти, как выровненных, так и не выровненных по границе четного полуслова. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 5 G 11 С 1 1/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР

1 (21) 440782S/24-24 (22) 01.02 ° SS (46) 15.01.90. Бюл, Ф 2 (71} Специальное конструкторское бюро "Кибернетика" с опытным производством Института кибернетики АНАэССР (72) А.И,Браурман (53) 681. 327. G (088. 8) (56) Иикропроцессоры, Справочник, Л,: Судостроение, 1987, с.178-180, Иикропроцессоры/Под ред. А.Н.Преснухина. Кн, 1. .N.: Высшая школа, .

1986, с. 344. (54) ЗАПОИИИА10ЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть исполь.зовано в системах обработки информации. Цель изобретения — повышение быстродействия устройства. УстройстИзобретение относится к вычислительной технике и может быть использовано в системах обработки информации.

Цель изобретения — повышение быстродействия запоминающего устройства.

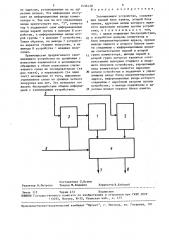

На чертеже представлена схема запоминающего устройства, .Иа фиг. 2, 3 показаны варианты расположения считываемого слова в блоках памяти.

Устройство содержит первый блок 1 памяти, второй блок 2 памяти, блок 3 инкрементирования адреса, коммутатор

4, адресные входы группы 5 устройства, адресный вход 6 устройства, выходы 7 старшего полуслова устройства, „.,su„„ А1

2 во содержит первый и второй блоки памяти, выходы которых соединены с информационными входами коммутатора, выходы которого являются выходами старшего и младшего полуслов устройства, блок инкрементирования адреса, управляющий вход которого подключен к управляющему входу устройства и является младшим адресным входом устройства, адресные входы первого блока .памяти соединены с выходами блока инкрементирования адреса, информационные входы которого подключены к адресным входам второго блока памяти и являются старшими адресными входами устройства, В устройстве обеспечивается выборка слов эа один цикл обращения к блокам памяти как выровнен.ных, так и не выровненных по границе четного полуслова. 1 ил, 2 табл..выходы 8 младшего полуслова устройст-: ва.

Коммутатор 4 может быть выполнен, например, на базе БИС обмена информацией КР 1802 ВВ1.

Возможны два случая расположения считываемого полуслова в блоках памяти: считываемое слово выровнено по границе четного полуслова; считываемое слово не выровнено по границе четного полуслова.

В случае, если считываемое слово выравнено па границе четного полусло-. ва, т,е, старшее полуслова имеет четный адрес, то старшее полуслова располагается в первом блоке 1 памяти, 1536438 а младшее полуслов о р ас пол а гает ся во втором блоке 2 памяти (см. табл. 1, Х вЂ” любая информация), При этом ячейки первого блока 1 памяти и второго блока 2 памяти, в которых хранятся

5 считываемые полуслова, имеют один и тот же адрес. А.

Таблица 1

10 + адрес

Содержимое первого блока паСодержимое второго блока памяти

Старшее полуслово

Ипадшее полуслово

В случае, если считываемое слово не выровнено по границе четного полуслова, т. е. старшее полуслово имеет нечетный адрес, то старшее полуслово располагается во втором блоке

2 памяти, а младшее полуслово .— в первом блоке 1 памяти (см. табл. 2, 30

Х вЂ” любая информация). При этом ячейка первого блока памяти, в которой хранится младшее полуслово, имеет адрес (А+,1), на единицу больший, чем ячейка второго блока 2 памяти, в которой хранится старшее полуслово.

Таблица 2

Адрес Содержимое 40 первого блока паСодержимое второго блока памяти

Старшее полуслово упадшее полуслово

При обращении к запоминающему устройству на адресный вход 6 устройства,подается младший разряд адреса .обращения, а на входы 5 устройства подаются о<.òàëüíûe разряды адреса обращения.

Устройство работает следующим образом, При обращении к запоминающему устройству по четному адресу на адресный вход 6 устройства подается лог.

"0", одновременно поступающий на управляющие входы блока 3 инкрементирования адреса и коммутатора 4. При этом адрес с входов 5 устройства поступает одновременно на информационные входы блока 3 инкрементирования .адреса н на адресные входы второго блока 2 памяти. Так как на управляющем входе блока 3 присутствует лог. "0", инкрементирование адреса не производится и на выходе блока 3 появляется адрес, равный адресу, установленному на его выходе. Этот адрес поступает на адресные входы блока 1 памяти. В результате одновременно происходит считывание ячеек первого блока 1. памяти и второго блока 2 памяти с одним и тем же адресом, причем на выходах первого блока 1 памяти .появляется старшее полуслово считываемого слова, а на выходе второго блока 2 памяти— младшее полуслово считываемого слова.

Эта информация поступает на информационные входы коммутатора 4. Так как на его управляющем входе присутствует лог. "О", то коммутатор 4 подключает свои информационные входы первой группы к выходам 7 устройства, а информационные входы второй группы — к выходам 8 устройства. Таким образом, на выходы 7 устройства выдается старшее полуслово, а на выходы 8 устройства— младшее полуслово.

При обращении к запоминающему устройству о нечетному адресу на адресный вход 6 устройства подается лог. 1, одновременно поступающая на управляющие входы блока 3 инкрементирования адреса и коммутатора 4. При этом адрес с входов 5 устройства поступает одновременно на информационные входы блока 3 и на адресные входы блока 2 памяти. Так как на управляющем входе блока 3 присутствует лог. "1", пройзводится инкрементирование адреса и на выходe блока 3 появляется адрес, на единицу больший адреса, установленного на его входах. Этот адрес пос" тупает на адресные входы блока 1 памяти. В результате происходит одновременное считывание младшего полуслова из первого блока 1 памяти и старшего полуслова из второго блока 2 памяти

38 6

Формула изобретения

Составитель О.Исаев

Редактор И.Петрова .Техред И. Ходанич

Корректор B. Кабаций

Заказ 112 Тираж 473 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул. Гагарина, 101

5 15364 по адресам, установленным на их ад= ресных входах. Эта информация поступает на информационные входы коммутатора 4. Так как на его управляющем входе присутствует лог. ")", коммута5 тор 4 подключает свои информационные входы первой группы к выходам 8 устройства, а информационные входы второй группы — к выходам 7 устройства.

Таким образом, на выходы 7 устройства выдается старшее полуслово, а на выходы 8 устройства — младшее полуслово

Преимущество предлагаемого запоминающего устройства по сравнению с известным заключается в возможности обращения к обоим полусловам считываемого слова не последовательно (эа два такта), а параллельно (за один 20 такт) независимо от того, выровнено считываемое слово по границе четного полуслова или нет. Это позволяет повысить быстродействие обмена информацией с запоминающим устройством. 25

Запоминающее устройство, содержащее первый блок памяти, второй блок памяти, адресные входы которого являются адресными входами группы устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство введены коммутатор н блок инкрементирования.адреса, причем выходы первого и второго блоков памяти соединены с информационными входами соответственно первой и второй групп коммутатора, выходы первой и второй групп которого являются соответственно выходами старшего и младmего полуслов устройства, управляющий вход коммутатора является адресным входом устройства и подключен к управляющему входу блока инкрементирования адреса, информационные входы которого соединены с адресными входами группы устройства, а выходы подключены к адресным входам первого блока памяти.