Накопитель

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике ипредназначено для использования в цифровых системах памяти на биполярных транзисторах. Цель изобретения - повышение надежности накопителя - достигается за счет изменения связей ключевого элемента и элементов предотвращения ложной записи накопителя, который приобретает функцию формирования опорного уровня считывания, что обеспечивает высокую степень соответствия уровня считывания уровню напряжения в выбранном элементе памяти в условиях воздействия внешних дестабилизирующих факторах и разброса параметров компонентов. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19).е (111 (51 5 С )1 С 11 0

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР

1 (21) 4402251/24-24 .(22) 04 .04 .88 (46) !5.01.90. Бюл, 11 2 (72) С.М.Игнатьев (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

1(с 1305774, кл. G 11 С 11/40, 1985.

Авторское свидетельство CCCP

И 1137537, кл. G 11 С 11/40, 1985. (54) НАКОПИТЕЛЬ (57) Изобретение относится к вычислительной технике и предназначено для использования в цифровых системах паИзобретение относится к вычислительной технике и предназначено для использования в цифровых схемах памяти на биполярных транзисторах.

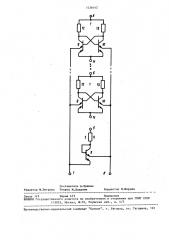

Цель изобретения — повышение надежности накопителя, На чертеже представлена схема накопителя.

Накопитель содержит матрицу элементов 1 памяти и элементы 2 предот вращения ложной записи, каждый из которых состоит из ключевого элемента

3 на двухэмиттерном транзисторе и элемента 4 смещения на резисторе, шину 5 напряжения смещения накопителя, входы 6 словарной выборки, информационные входы-выходы 7 и 8 столбца накопителя, нагрузочные элементы 9 и 10 на транзисторах, входы 11 тока хранения и нагрузочные элементы 12 и )3 на резисторах.

Накопитель работает следующим образом.

2 мяти на биполярных транзисторах.

Цель изобретения — повышение надежности накопителя — достигается за счет изменения связей ключевого элемента и элементов предотвращения ложной записи накопителя, который приобретает функцию формирования опорного уровня считывания, что обеспечивает высокую степень соответствия уровня считывания уровню напряжения в выбранном элементе памяти в условиях воздействия внешних дестабилизирующих факторов и разброса параметров компонентов. 1 ил.

В режиме записи информации выборка нужного элемента 1 осуществляется посредством повышения потенциала иа входе 6 соответствующей строки матрицы и включения тока записи в один из входов-выходов 7, 8 соответствующего столбца матрицы. Ток записи включает" ся в тот вход-выход 7, 8, к которому подключен эмиттер управления элементов 9 или 10 выбранного элемента 1, у которого в соответствии с поступаю.щей информацией в результате записи на базе должен установиться высокий потенциал. Уровень напряжения на шине 5 накопителя равен напряжению на входах 6 невыбранных строк матрицы, этот уровень лежит ниже нижнего уровня напряжения на базах элементов 9 и 10 выбранного элемента 1. Таким образом, среди элементов 3, 9 и 10, эмиттеры которых подключены к входувыходу 7, 8 с включенным током записи, самый высокий потенциал на базе

1536442 у элементов 9 или 10 выбранного элемента 1 не зависит от его состояния и, следовательно, ток записи ответвится в эмиттер этого элемента, что

5 приведет к установке выбранного элемента 1 в требуемое состояние. В режиме считывания информации выборка строки матрицы, содержащей нужный элемент 1, осуществляется аналогично режиму записи, на шине 5 устанавли вается напряжение, равное напряжению .на входе.,б выбранной строки матрицы, а для. выборки нужного столбца матрицы в соответствующие входы-выходы 7, 8 включаются токи считывания. Ток считывания, включенный в узел, соответствующий эмиттеру управления элементов 9 или 10 выбранного элемента

l с низким уровнем напряжения íà базе, протекает в соответствующем эмиттере элемента 3 элемента 2, так как в момент включения тока считывания этот элемент имеет самый высокий базовый потенциал. Ток считывания, включенный в узел, соответствующий элементу 9 или 10 выбранного элемента 1 с высоким базовым потенциалом, по завершении формирования уровня напряжения на базе элемента 3 целиком протекает в выбранный элемент 1, В результате описанного распределения токов считывания на входах-выходах 7, 8 выбранного столбца матрицы сформи" руются логические напряжения в соответствии с состоянием выбранного элемента 1, На входе-вых е 7, 8, где ток считывания протекает в элементе

3, формируется напряжение низкого логического уровня, равное напряжению на базе элемента 3 минус напряжение 40 между базой и соответствующим эмиттером элемента 3, а на другом входевыходе 7, 8 формируется напряжение высокого логического уровня, равное высокому базовому уровню в выбранном элементе 1 минус напряжение между базой и эмиттером соответствующего элемента 9 или 10.

Элементы 2 выполняют две функцииформирование информационной разности потенциапав на информационных входахвыходах 7, 8 и предотвращение включения тока считывания в элементы 9 или

10 выбранного элемента 1„ что может привести к ложной записи, Наиболее

I оптимальное выполнение обеих функций в данном устройстве достигается в том случае, когда базовое напряжение элемента 3 занимает средний уровень между высоким и низким уровнями напряжений в выбранном элементе 1. Для обеспечения такого соотношения необходимо подобрать величину сопротивления элемента 4. При использовании в накопителе элементов 1 с резистивными нагрузками сопротивление элемен" та 4 равно половине номинального сопротивления нагрузочных элементов 12 и 13, Таким образом, предлагаемый накопитель обладает по сравнению с известными более высокой устойчивостью к разбросу параметров компонентов, что позволяет повысить надежность его работы в условиях воздействия внешних дестабилизирующих факторов и тех" нологичность при производстве. Применение накопителя наиболее целесообразно в интегральных микросхемах ОЗУ малой информационной емкости, содержащих элементы памяти с линейными нагрузками, например в HC ОЗУ типа

К15ООРУО?3 емкостью 64к4 бит, Ф о р м у л а и з обретения

Накопитель, содержащий матрицу элементов памяти, элементы предотвращения ложной записи, каждый из которых состоит из ключевого элемента на двухэмиттерном транзисторе и элемента смещения на резисторе, первый и второй выводы которого подклю" чены соответственно к базе двухэмиттерного транзистора ключевого элемента и шине напряжения смещения накопителя, в каждом столбце матрицы первые и вторые информационные входьгвыходы элементов памяти подключены соответственно к первому и второму эмиттерам двухэмиттерного транзистора ключевого элемента соответствующего элемента предотвращения ложной записи, отличающийся тем, что, с целью повышения надежности накопителя, в каждом элементе предотвращения ложной записи коллектор двухэмиттерного транзистора ключевого элемента подключен к его базе.

1536442

Со стави тел ь А. Ершова

Редактор М.Петрова Техред М,Ходанич Корректор И.Шароши

Заказ 112 Тираж 473 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101