Устройство для контроля многоразрядных блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для контроля многоразрядных блоков памяти, а также для функционального контроля микросхем ОЗУ. Цель изобретения - повышение достоверности контроля. Устройство содержит генератор 1 тактовых сигналов, блок 2 пуска-останова, первый триггер 3, первый счетчик 4, второй триггер 5, второй счетчик 6, блок формирования сигнала "Выбор кристалла" 7, блок постоянной памяти 8, блоки сравнения 9, блоки индикации 10, многоразрядный блок 11 памяти. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

А1

9Я0 (51)5 G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯЫ

ПРИ ГНКТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4177810! 24-24 (22) 07.01.87, (46) 15.01.90. Бюл. 1» 2 (72) С,Н.Семенов и 10.А.Марков1 (53) 681,327.6(088.3) (56} Авторское свидетельство СССР

У 771730, кл. G 11 С 29/00, 1980.

Авторское свидетельство СССР

N 1244727, кл, G ll С 29/00, 1986. (54) УСТРОЙСТВО ДЛЯ 1(ОНТРОЛЧ МНОГОРАЗРЯДНЫХ БЛО1(ОВ ПЫХТИ (57) Изобретение относится к вычисли" тельной технике и может быть исполь2 зовано для контроля многоразрядных блоков памяти, а также для Функционального контроля микросхем ОЗУ.

Цель изобретения — повьппение достоверности контроля. Устройство содержит генератор 1 тактовых сигналов, блок 2 пуска-останова, первый триггер 3, первый счетчик 4, второй триггер 5, второй счетчик 6, блок 7 формирования сигнала "Выбор кристалла", блок 8 постоянной памяти, блоки

9 сравнения, блоки 10 индикации и многоразрядный блок 11 памяти. 2 ил, 1536444

Изобретение относится к вычислительной технике и может быть использовано для контроля многоразрядных блоков памяти, а также для функционального контроля микросхем ОЗУ.

Цель изобретения — повышение достоверности контроля.

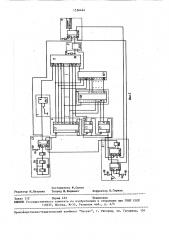

На фиг. 1 приведена схема устройства для контроля многоразрядных блоI ков памяти; на фиг. 2 — пример воз" можной практической реализации пред,лагаемого устройства.

Устройство (фиг. 1) содержит генератор 1 тактовых сигналов, блок 2 пуска-останова, первый триггер 3, первый счетчик 4, второй триггер 5, второй счетчик 6, блок 7 формирования сигнала"Выбор кристалла", блок 8 постоянной памяти, И блоков 9 сравне- 20 .ния, группу И блоков 10 индикации, многоразрядный блок 11 памяти. На фиг. 1 обозначено: и — количество адресных входов контролируемого многоразрядного блока 11 памяти И вЂ” коли- 25 чество информационных входов контро.лируемого многоразрядного блока 11 ,памяти; К вЂ” разрядность дополнительного счетчика 6.

Устройство работает следующим об" ,разом.

Контроль многоразрядных блоков памяти проводится в два этапа.

На первом этапе контроля выявляют ся неисправности схем "Выбор кристалла". С помощью формирователя 7

35 сигнаЛа "Выбор криста "ча" отключаются ,схемы "Выбор кристалла". По команде

"Пуск" с блока 2 пуска-останова устройство формирует управляющие сигналы.

H тестовую последовательность íà эа пись. При выключенных схемах "Выбор кристалла" контролируемый многоразрядный блок 11 памяти не должен записывать и считывать тестовую информацию.

Наличие сигнала "Брак" на первом этапе, контроля говорит о том, что контролируемый многоразрядный блок 11 памяти имеет неисправимые дефекты схемы "Выбор кристалла" и дальнейшему контролю не подлежит, На втором этапе контроля устройство также работает в двух режимах: в режиме записи информации по адресам и

55 в режиме считывания записанной информации, при котором осуществляется выявление неисправностей проверяемого многоразрядного блока памяти.

Перед началом работы устройства первый триггер 3, первый счетчик 4, второй триггер 5, второй счетчик 6 находятся в нулевом состоянии, Перед началом второго этапа контроля с помощью формирователя сигнала "Выбор кристалла" включаются схемы "Выбор кристалла", затем по команде "Пуск" блок 2 пуска-останова запускает генератор 1 тактовых сигналов, который начинает выдавать тактовые импульсы на первые входы И блоков 9 индикации и на счетный вход первого счетчика 3.

Второй триггер 5 формирует код, обеспечивающий реализацию режимов записи и считывания: "0" — запись, "1" — считывание информации для контролируемоro многоразрядного блока памяти.

Код адреса поступает в многоразрядный блок памяти с выходов счетчика 4 и этот же код поступает íà и входов младших адресов разрядов блока 8 постоянной памяти. На K старших адресных разрядов блока постоянной памяти подается код с соответствующих выходов второго счетчика 6.

Блок 8 постоянной памяти формирует тестовую последовательность, поступающую как на информационные входы контролируемого многоразрядного блока 11 памяти, так и на вторые входы

И блоков 9 сравнения, на первые входы которых подается считываемая из контролируемого многоразрядного блока памяти тестовая последовательность.

И блоков 9 сравнения служат для сравнения данных, считанных из контролируемого многоразрядного блока 11 памяти по заданным последовательностям адресов, с данными, которые были записаны по тем же последовательностям адресов, и работают следующим образом °

Считываемые из контролируемого многоразрядного блока 11 памяти коды без изменения поступают на первые входы М блоков 9 сравнения, которые осуществляют поразрядное сравнение . поступающих на них кодов. По результатам сравнения информации, записанной s контролируемый многоразрядный блок 11 памяти и считанной из него, формируются . сигналы "Годен-брак", которые с выхода М блоков 9 сравнения поступают на вторые входы И блоков 10 индикации, где фиксируется неисправность.

5 15

При этом формируется сигнал "Брак" и загорается элемент индикации, по которому фиксируется неисправность в соответствующем разряде контролируемого многоразрядного блока 11 памяти, По окончании цикла контроля (после того, как все тестовые последовательности, предварительно записанные в блок 8 постоянной памяти, иэ него считаны) при полном совпадении информации, записанной в контролируемый многоразрядный блок ll памяти, с информацией считанной из этого блока памяти, второй счетчик 6 формирует сигнал, который поступает в блок 2 пуска-останова, который в свою очередь формирует сигнал "Останова", по которому генератор 1 тактовых сигналов прекращает формирование тактовых импульсов.

Формула изобретения

Устройство для контроля многоразрядных блоков памяти, содержащее генератор тактовых сигналов, первый счетчик, первый вход генератора тактовых сигналов является входом задания режима. устройства, о т л и— ч а ю щ е е с я тем, что, с целью повьппения достоверности контроля, в устройство введены первый и второй триггеры, второй счетчик, блок формирования сигнала "Выбор кристалла", блок постоянной памяти, группа бло ков сравнения, инверсный выход первого триггера соединен с входом синх36444 6 ронизации первого счетчика, выход переноса которого соединен с входом синхронизации второго триггера, инверсный выход которого соединен с входом синхронизации второго счетчика, первый выход генератора тактовых сигналов является выходом синхронизации устройства, второй выход генератора тактовых сигналов соединен .с входом синхронизации первого триггера, пря мой выход которого соединен с входом блока формирования сигнала Выбор кристалла", выход которого является выходом разрешения выборки устройства, входы начальной установки первого и второго триггеров, первого и второго счетчиков объединены и являются соответствующим входом устрой20 ства, выход переноса второго счетчика является выходом "1(онец работы" устройства, выходы группы блоков сравнения являются выходами результата контроля устройства, прямой вы25 ход второго триггера является выходом записи-чтения устройства, выходы первого счетчика соединены с входами первой группы блока постоянной памяти и являются адресными выходами уст30 ройства, входы второй группы блока постоянной памяти соединены с вьмодами второго счетчика, выходы блока постоянной памяти соединены с входами второй группы блока сравнения и являются информационными выходами устройства, входы первой группы бло" ка сравнения являются информационны" ми входами устройства.

1536444

Составитель В. Сычев

Редактор М.Петрова Техред М, Ходанич Корректор В.Гирняк

Заказ 112 Тираж 472 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, И-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101