Преобразователь кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - упрощение преобразователя. Преобразователь содержит логические ячейки. Логическая ячейка содержит элемент ИЛИ и элемент И. Преобразователь кодов является многопороговым логическим элементом, реализующим на выходах пороговые функции с порогами, равными порядковым номерам выходов, от числа переменных, равного числу входов преобразователя. 2 ил.

СОЮЗ СОНЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ЕНИЯ, ГОСУДАРСТНЕННЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4398981/24-24 (22) 29.03.88 (46) 15.01.90. Бюл. Р 2 (72) Б.М. Солодухин, А.С. Серков, С ° M. Федоров и Л.Н. Ким (53) 681. 325 (088.8) (56) Авторское свидетельство СССР

Р 1261122, кл. Н 03 M 7/14, 1985.

Авторское свидетельство СССР

М 1264346, кл. Н 03 M 7/14, 1985.

Изобретение относится к автоматизации и вычислительной технике.

Цель изобретения — упрощение преобразователя.

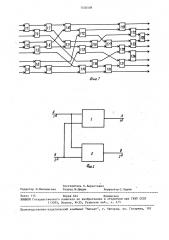

На фиг. 1 представлена схема преобразователя кодов; на фиг. 2 — схема логической ячейки.

Преобразователь кодов содержит логические ячейки 1,1-1,25.

Логическую ячейку образуют элемент

ИЛИ 2 и элемент И 3.

Преобразователь кодов работает следующим образом.

Преобразователь кодов является многопороговым логическим элементом, реализующим на выходах пороговые функции (пороги, равны порядковым номерам выходов) от числа переменных, равного числу входов преобразователя.

При подаче на любую из входных шин одного единичного потенциала единичный потенциал появляется на соответствующем входе и выходе соответ„„SU„„1536509 А1, (51) 5 Н 03 И 7/02 7/14

2 (54 ) ПРЕОБРАЗОВАТЕЛЬ КОДОВ (57) Изобретение относится к автоматике и вычислительной технике. Цель изобретения — упрощение преобразователя. Преобразователь содержит логические ячейки. Логическая ячейка содержит элемент ИЛИ и элемент И. Преобразователь кодов является многопороговым логическим элементом, реализующим на выходах пороговые функции с порогами, равньпж порядковым номерам выходов, от числа переменных, равного числу входов преобразователя. 2 ил. ствующей ячейки 1, первом выходе следующей ячейки 1 и т.д. и на соответствующей выходной шине.

Работа преобразователя кодов аналогична описанному при любом числе единичных сигналов на входных шинах.

Формула изобретения

Преобразователь кодов, содержащий логические ячейки, каждая из которых имеет первый и второй входы, первый и второй выходы, первый выход первой логической ячейки соединен с одноименным входом второй логической ячейки, второй выход которой соединен с первым входом третьей логической ячейки, первый выход которой соединен с одноименным входом четвертой логической ячейки, второй выход первой логической ячейки соединен с первым входом пятой логической ячейки, первый выход которой соединен с вторым входом

1536509 второй логической ячейки, второй выход третьей логической ячейки соединен с первым входом шестой логической ячейки, первый выход которой соединен с вторым входом четвертой логи5 ческой ячейки, первый выход седьмой логической ячейки соединен с одноименным входом восьмой логической ячейки, второй выход седьмой логичес- о кой ячейки соединен с первым входом девятой логической ячейки, первый выход которой соединен с вторым входом восьмой логической ячейки, второй выход десятой логической ячейки соеди15 нен с первым входом одиннадцатой логической ячейки, первый выхоц которой соединен с вторым входом двенадцатой логической ячейки, второй выход одиннадцатой логической ячейки соединен с первым входом тринадцатой ячейки, первый выход которой соединен с вторым входом четырнадцатой. логической ячейки,первый выход которой соединен с вторым входом пятнадцатой логи геской ячейки, первый выход которой соединен с вторым входом шестнадцатой логической ячейки, второй выход пятнадцатой логической ячейки соединен с первым входом семнадцатой логической ячейки, первый выход восемнадцатой логической ячейки соединен с вторым входом двенадцатой логической ячейки, второй выход которой соединен с первым входом двадцатой логической ячейки, второй выход которой соединен с одно- 35 именным входом тринадцатой логической ячейки, второй выход восемнадцатой логической ячейки соединен с одноименным входом двадцатой логической ячейки, второй выход четырнадцатой логической ячейки соединен с первым входом дваццать первой логической ячейки, второй выход тринадцатой логической ячейки соединен с одноименным входом двадцать первой логической ячейки, двадцать вторую — двадцать пятую логические ячейки, вторые выходы шестнадцатой и двадцать первой логических ячеек и первый и второй выходы семнадцатой логической ячейки 5О являются соответственно первым — четвертым выходам преобразователя, о тл и ч а ю шийся тем, что, с целью упрощения преобразователя, первый выход второй логической ячейки соединен с одноименным входом седьмой логической ячейки, второй выход восьмой логической ячейки соединен с первым входом двадцать второй логической ячейки, второй выход которой соединен с первым входом двадцать третьей логической ячейки, второй выход пятой логической ячейки соединен с первым входом четырнадцатой логической ячей.ки, первый выход двенадцатый логической ячейки соединен с вторым входом девятой логической ячейки, второй выход которой соединен с первым входом двадцать пятой логической ячейки, первый выход которой соединен с одноименным входом шестнадцатой логической ячейки, первшй выход которой соединен с вторым входом двадцать третьей логической ячейки, первый и второй выходы четвертой логической ячейки соединены соответственно, с вторыми входами двадцать второй и двадцать пятой логических ячеек, второй выход двадцать пятой логической ячейки соединен с первым входом пятнадцатой логической ячейки, первый выход десятой логической ячейки соединен с одноименным входом двенадцатой.логической ячейки, первый и второй выходы которой соединены с вторыми входами, соответственно седьмой и третьей логических ячеек, первый выход двадцатой логической ячейки соединен с вторым входом шестой логической ячейки, второй выход которой и первый выход двадцать первой логической ячейки соединены соответственно с первым и вторым входами двадцать четвертой логической ячейки, первый выход которой соединен с вторым входом семнадцатой логической ячейки, первый и второй входы первой, десятой и восемнадцатой, вторые входы пятой и одиннадцатой и первый вход девятнадцатой логических ячеек являются соответственно первым — девятым входами преобразователя, первые выходы восьмой и двадцать второй, первый и второй выходы двадцать третьей и второй выход двадцать четвертой логических ячеек являются соответственно пятым — девятым выходами преобразователя.

1536509

Составитель С.Берестевич

Техред М:Дидык Корректор С.Черни

Редактор Л.Пчолинская

Заказ 115 Тираж 644 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101