Ограничитель вибраций газотурбинного двигателя

Иллюстрации

Показать всеРеферат

Изобретение позволяет повысить надежность ограничителя вибраций ГТД путем предотвращения ложной выдачи сигнала о превышении допустимого уровня вибрации. В момент контроля сигналы управления в виде последовательности импульсов начинают поступать на входы блока 11 памяти, схемы 14 И-НЕ задатчика 12 порогового уровня и блока 10 отказа. С выхода блока 11 памяти сигнал, соответствующий состоянию выхода амплитудного дискриминатора 4, в момент начала контроля через вход схемы 15 ИЛИ-НЕ и схему 6 И поступает на исполнительный механизм 7, сохраняя состояниие последнего неизменным во время контроля, если ограничитель исправен. Блок 10 отказа при поступлении сигнала контроля производит запоминание состояния выхода амплитудного дискриминатора 4 в момент начала контроля, а затем, в процессе контроля, анализирует изменение этого состояния. Наличие обратной связи с выхода амплитудного дискриминатора 4 через задатчик 12 порогового уровня на его второй вход обеспечивает выдачу сигнала о превышении вибрации при колебаниях величины сигнала на его первом входе. При отсутствии оборотов определенного уровня или при наличии неисправности в цепях амплитудного дискриминатора 4 с выходов тахометрического сигнализатора 5 и блока 10 отказа соответственно на входы схемы И 6 поступают сигналы в виде логического "О", запрещающие выдачу сигнала о превышении допустимого уровня вибраций. Такое выполнение устройства повышает надежность его работы. 5 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 5 F 02 С 9/00

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ вЂ” -К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

1 (21) 4315506/25-06 (22) 12. 10 ° 87 (46) 23. 01. 90. Бюл. Ф 3 (72) В.И. Михайленко и Г.А. Душенко (53) 621.438-55(088.8) (56) Авторское свидетельство СССР к- 502552, кл. F 02 С 9/00, 1 97 3. (54) ОГРАНИЧИТЕЛЬ ВИБРАЦИЙ ГАЗОТУРБИННОГО ДВИГАТЕЛЯ (57) Изобретение позволяет повысить надежность ограничителя вибраций ГТД путем предотвращения ложной выдачи сигнала о превышении допустимого уровня вибрации. В момент контроля сигналы управления в виде последовательности импульсов начинают поступать на входы блока 11 памяти, схемы И-HE

14, задатчика 12 порогового уровня и блока 10 отказа. С выхода блока 11 памяти сигнал, соответствующий состоянию выхода амплитудного дискриминатора 4, в момент начала контроля через вход схемы ИЛИ-НЕ 15 и схему И 6 поступает на исполнительный механизм

7, сохраняя состояние последнего неÄÄSUÄÄ 1537856 А 1

2 изменным во время контроля, если ограничитель исправен. Блок 10 отказа при поступлении сигнала контроля производит запоминание состояния выхода амплитудного дискриминатора 4 в момент начала контроля, а затем, в процессе контроля, анализирует изменение этого состояния. Наличие обратной связи с выхода амплитудного дискриминатора 4 через задатчик 12 порогового уровня на его второй вход обеспечивает выдачу сигнала о превышении вибрации при коле баниях величины сигнала на е ro первом входе. При отсутствии оборотов определенного уровня или при наличии неисправности в цепях амплитудного дискриминатора 4 с выходов тахометрического сигнализатора 5 и блока

10 отказа соответственно на входы схемы И 6 поступают сигналы в виде логического "0", запрещающие выдачу сигнала о превышении допустимого уровня вибраций. Такое выполнение устройства повышает надежность его работы.

5 ил.

1537 85 6

Изобретение относится к области автоматического управления и контроля газотурбинных двигателей (ГТД), в частности к устройствам ограничения вибраций.

Цель изобретения — повышение надежности ограничителя вибраций газотурбинного двигателя путем предотвращения ложной выдачи сигнала о превышении допустимого уровня вибрации за счет обеспечения контроля работоспособности.

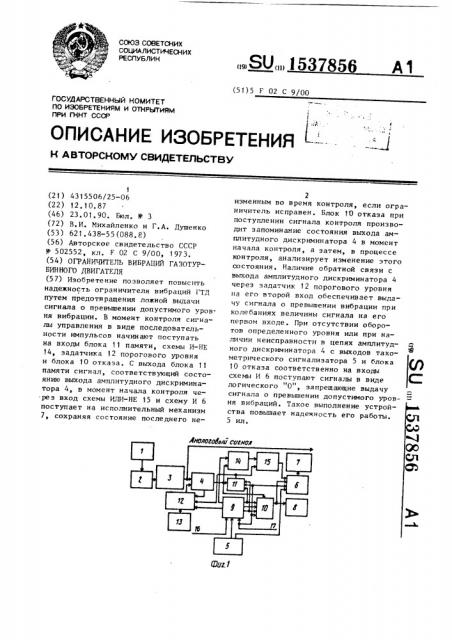

На фиг. 1 представлена структурная хема ограничителя вибраций ГТД; на фиг. 2 — структурная схема задатчика порогового уровня; на фиг ° 3 — структурная схема блока управления; на фиг. 4 — структурная схема блока от. каза и его соединений; на фиг.5— временная диаграмма работы ограничителя при контроле работоспособности.

Ограничитель вибраций ГДТ (фиг.1) содержит последовательно соединенные датчик 1 вибраций, фильтр 2, преобра- 25 зователь 3 и амплитудный дискриминатор 4, последовательно соединенные тахометрический сигнализатор 5, схему И 6 и исполнительный механизм 7, индикатор 8, блок 9 управления, блок 30

10 отказа, блок 11 памяти, задатчик 12 порогового уровня, источники 13 ( эталонного напряжения, схему И-НЕ 14, схему ИЛИ-НЕ 15, шину 16 внешнего запуска контроля и шину 17 установки, подключенную к первым входам блока 9 управления, блока 10 отказа и блока

11 памяти и второму входу схемы И 6, третий вход которой подключен к входу индикатора 8 и выходу блока 10 40 отказа, второй вход которой подключен к входу индикатора 8 и выходу блока

10 отказа, второй вход которого подключен к первому выходу амплитудного дискриминатора 4, второму входу бло- 45 ка 11 памяти и первому входу схемы

И-НЕ 14, второй вход которой подключен к первому выходу блока 9 управления, а выход — к первому входу схемы

HJIH-HE 15 второй вход которой подУ

50 ключен к первому входу задатчика 12 порогового уровня и выходу блока 11 памяти, а выход — к четв ер тому входу схемы И 6, шина 16 внешнего запуска контроля подключена к второму входу блока 9 управления, третий вход ко55 торого подключен к второму выходу тахометрического сигнализатора 5, второй, третий и четвертый выходы соответственно к третьему, четвертому и пятому входам блока 10 отказа, а пятый выход — к второму входу задатчика 12 порогового уровня, третий вход которого подключен к второму выходу амплитудного дискриминатора 4, четвертый вход — к выходу источников 13 эталонного напряжения, а выход — к второму входу амплитудного дискриминатора 4, третий и четвертый выходы блока 9 управления подключены к третьему и четвертому входам блока

11 памяти.

Задатчик 12 порогового уровня содержит ключи 18, схему 19 управления ключами и резистивные делители

20, а блок 9 управления (фиг„ 3) содержит генератор 21 опорной частоты, счетчик 22 импульсов, триггер 23, формирователь 24, схему ИЛИ вЂ 25, дешифратор 26, схему ИЛИ 27.

Блок 10 отказа (фиг. 4) содержит инвертор НЕ 28, элемент ИЛИ 29, триггер 30, элемент И-НЕ 31, элемент И-НЕ

32, инвертор НЕ 33 и триггер 34.

Ограничитель работает следующим образом.

После подачи питающих напряжений сигналом установки "0" (фиг,5а) блок

9 управления, а также блок 11 памяти и блок 10 отказа устанавливается в исходное состояние, при этом с выхода блока 9 управления (фиг. 5г) на вход схемы И-HE 14, с выхода блока 11 памяти (фиг ° 5к) на вход схемы ИЛИ НЕ 15 и с выхода блока 10 отказа на вход схемы И 6 (фиг ° 5н) поступают сигналы в виде логической

"1", разрешающие нормальное функционирование указанных схем. Одновременно при этом сигнал установки "О" (фиг. 1 и 5a), поступая на вход схемы И 6, запрещает ее функционирование, чем предотвращается ее возможное срабатывание и выдача ложного сигнала в момент включения питания.

Сигнал в виде переменного напряжения, пропорциональный уровню вибрации корпуса ГТД и изменяющийся как по амплитуде, так и по частоте, с датчика 1 вибраций через фильтр 2 контролируемого диапазона частот и через преобразователь 3 переменного напряжения в постоянное поступает на первый вход амплитудного дискриминатора 4 и одновременно на выход устройства для регистрации величины преобразованного постоянного напря5 15 жения (аналоговый сигнал, фиг. 1), например, в регистратор. При наличии вибраций, не превышающих допустимых, уровень напряжения на первом входе не превышает заранее установленного уровня напряжения на втором входе амплитудного дискриминатора 4 и с его второго выхода сигнал, например, в виде логического "0 поступает на вхо ды блока 10 отказа, блока 11 памяти и схемы И-НЕ 14. С выхода схемы И-НЕ

14 инвертированный сигнал в виде логической "1" поступает на вход схемы

HJlH-HE 15, на другой вход которой с момента включения питания подается сигнал в виде логической "1" с выхода блока 11 памяти. Далее сигнал с выхода схемы ИЛИ-НЕ 15 в виде логического "0" поступает на вход схемы

И 6, на два оставшихся входа которой поступают сигналы с выхода блока 10 отказа и тахометрического сигнализатора 5.

Наличие сигнала с уровнем логического "0" на любом из входов схемы

И 6 не вызывает срабатывания исполни-! тельного механизма 7. При нарастании ,оборотов до определенного уровня сра-! батывает тахометрический сигнализа,тор 5 и с его выхода сигнал в виде логической "1" поступает на один иэ входов схемы И 6, разрешая тем самым прохождение через эту схему остальных сигналов, поступающих на другие ее входы. По мере нарастания оборотов с другого выхода сигнализатора 5 через первый вход схемы ИПИ-HE

25 блока управления сигнал в виде логического "0 поступает на вход формирователя 24 блока 9 управления.

Аналогичный сигнал (фиг. 5б) "Внешний запуск контроля" через другой вход схемы ИЛИ-НЕ 25 блока 9 управления может поступить на вход формирователя 24, например, от оператора ипи определенного устройства системы автоматизированного контроля. В момент поступления сигнала в виде логического "0" на вход формирователя

24 блока 9 управления последний срабатывает и с его выхода импульс в виде логического "0" поступает на вход триггера 23, вследствие чего триггер 23 переключается и с его выхода на один из входов счетчика 22 импульсов поступает сигнал в виде логической "1" и он начинает считывание импульсон, поступающих с выхода

37856 6

0

55 генератора 21 опорной частоты. С выходов дешифратора 26 сигналы управления (в момент контроля) в виде последовательности импульсов (фиг.5в-з) начинают поступать на входы блока 11 памяти, схемы И-НЕ 14, эадатчика 12 порогового уровня и блока 10 отказа (фиг ° 4) .

Блок 11 памяти по сигналу "1 И

Запоминания" (фиг.5в) производит запоминание уровня сигнала, имеющегося на выходе амплитудного дискриминатора 4 в момент начала контроля ° С выхода, блока 11 памяти сигнал, соответ-: ствующий состоянию выхода амплитудного дискриминатора 4 (например, в виде логической "1", если вибрации ниже допустимого уровня), через вход схемы ИЛИ-НЕ 15 и схему И 6 поступает на исполнительный механизм 7, сохраняя состояние последнего, существовавшее до начала контроля.

Сигнал "ОИ Запрета" (фиг.5г), поступающий из блока 9 управления на вход схемы И-НЕ 14, запрещает на время проведения контроля прохождение через нее сигналов с выхода амплитудного дискриминатора 4 на вход схемы

KIH-HE 15 .

Поэтому срабатывание амплитудного дискриминатора 4 в процессе контроля работоспособности не приводит к изменению состояния исполнительного механизма 7.

Блок 10 отказа при поступлении сигнала "1И Запоминания" (фиг.5в) производит запоминание состояния выхода амплитудного дискриминатора 4, существующее в момент начала контроля °

Посредством сигнала "1И Управления" (фиг. 5e) на время действия этого сигнала уровень выходного сигнала задатчика 12 порогового уровня в зависимости от уровня сигнала с выхода блока 11 памяти изменяется таким образом, чтобы обеспечивалось срабатывание амплитудного дискриминатора 4, если последний исправен.

Так, например, если амплитудный дискриминатор 4 исправен и перед началом контроля работоспособности выдавал сигнал о превьппении допустимого уровня вибрации, то при поступлении сигнала "1И Управления" в эадатчик 12 порогового уровня на выходе последнего формируется сигнал в виде постоянного напряжения (например, 1537856

7В), которое превышает величину напряжения (например, на 107), поступающего с выхода преобразователя 3 переменного напряжения в постоянное на первый вхор амплитудного дискриминато5 ра 4 в случае наличия предельно допустимой вибрации, и обеспечивает выключение амплитудного дискриминатора 4 и возвра щение его выходного сигнала к уровню, 10 когда сигнал о превышении допустимой вибрации не выдается.

И наоборот, например, если амплитудный дискриминатор 4 исправен и перед началом контроля работоспособности сигнал о превышении вибрации не выдавал, то при поступлении сигнала "1И Управления" в эадатчик 12 порогового уровня на выходе последнего формируется сигнал в виде посто- 20 янного напряжения (например, -О, 1 В), который и при отсутствии вибрации обеспечивает срабатывание амплитудного дискриминатора 4, и последний во время действия сигнала "1И Управления 25 выдает сигнал о превышении вибрации.

Посредством сигнала "1И Отказа" (фиг. 5а) блок 10 отказа формирует сигнал отказа (неисправности) амплитудного дискриминатора 4 в виде логи- 30 ческого "0", если выходной сигнал последнего во время действия сигнала

"1И Управления" не изменился на противоположный по сравнению с его выходным сигналом перед началом контроля работоспособности.

В этом случае сигнал отказа (неисправности) с уровнем логического 0" с выхода блока 10 отказа, поступая на вход схемы И 6, запрещает прохож- 40 дение через нее других сигналов, поступающих на ее другие входы, т.е, путем проведения контроля работоспособности предотвращается выдача ложного сигнала неисправного устройства. 45

Одновременно этот же сигнал отказа, поступая на вход индикатора 8, вызывает срабатываение последнего, сигнализируя о неисправности устройства.

Если амплитудный дискриминатор 4 исправен, то на выходе блока 10 отказа посредством сигнала "1И Отказа" формируется сигнал в виде логической

"1", т. е. уровень выходного сигнала блока 10 отказа остается прежним. и, поступая на вход схемы И б, не препятствует прохождению других сигналов через ее другие входы.

После окончания контроля работоспособности с выхода дешифратора 26 через схему ИЛИ 27 на вход триггера

23 блока 9 управления поступает сигнал, устанавливающий триггер 23 в исходное состояние. С выхода последнего на вход счетчика 22 импульсов поступает сигнал, запрещающий функционирование счетчика 22 импульсов.

Одновременно в момент окончания контроля из блока 9 управления в блок

11 памяти, блок 10 отказа подается сигнал ИО Окончания контроля" (фиг. 5з) на установку в исходное состояние, а на схему И†HE 14 (фиг.5г)— разрешение в виде логической " 1" для нормального прохождения через нее сигналов с выхода амплитудного дискриминатора 4.

Если уровень вибраций превышает допустимый, то уровень напряжения на первом входе амплитудного дискриминатора 4 превышает заранее установленный уровень напряжения на его втором входе и амплитудный дискриминатор 4 срабатывает и с его выхода сигнал о превышении вибраций допустимого уровня в виде логической "1" поступает на входы блока 11 памяти, блока 10 отказа и через схемы 8 и И-НЕ 14 и

ИЛИ-ИЕ 15 на один из входов схемы

И 6.

Выходные сигналы блока 11 памяти и блока 10 отказа не изменяют своего состояния, так как блоки срабатывают только в процессе контроля работоспособности, Если на всех входах схемы И 6 имеются сигналы с уровнем логической

"1", то схема И Ь срабатывает и включает исполнительный механизм 7.

Временная диаграмма работы ограничителя вибраций ГТЦ в процессе контроля работоспособности графически представлена на фиг. 5.

По сигналу "1И запоминания" на выходе блока 11 памяти устанавливается сигнал с уровнем логической "1" (фиг. 5к), если в промежуток времени t, — t на втором выходе амплитудного дискриминатора 4 был установлен уровень логического "0" (фиг.5и).

С выхода блока 11 памяти сигнал с уровнем логической "1" подается на вход схемы ИЛИ-HF. 15 (фиг.4) и на один из входов схемы 19 управления ключами эадатчика 12 порогового уровня (фиг. 2).

1537856

Поступление сигнала "1И Запоминания" на вход Т триггера 30 блока 10

I отказа (фиг ° 4) в данном случае не вызывает переключения триггера 30 (так как на вход I триггера 30 непо5 средственно е выхода амплитудного дискриминатора 4 поступает сигнал с уровнем логического "О", а на вход К триггера 30 — сигнал проинвертиро1

1О ванный инвертором НЕ 28 блока 10 отказа, с уровнем логической "1", т.е. триггер 30 останется в исходном состоянии, а поэтому с выхода Q триггера 30 сигнал с уровнем логического

"О" подается на второй вход схемы

И-HE 31, а с выхода Q триггера 30 сигнал с уровнем логической "1"— на вход схемы И-HF. 32 блока 10 отказа (фиг. 4).

Сигнал ОИ Запрета с уровнем логического "О" действует в промежуток времени -t< (фиг.5г) и подается на вход схемы И-HF, 14, запрещая на время контроля прохождение через пер- 25 вый ее вход сигналов с выхода амплитудного дискриминатора 4 на вход схемы ИЛИ-НЕ 15 (фиг. 1 и 4) в процессе произведения проверки исправности.

Поэтому при наличии сигнала ОИ Запрета" на вход схемы ИЛИ-НЕ 15 на протяжении времени t -t подается сигнал с уровнем логической "1", который не препятствует работе схемы ИЛИ-НЕ 15, Так как с выхода блока 11 памяти на вход схемы ИЛИ-НЕ 15 в этом случае

35 подается сигнал с уровнем логической

"1", то с выхода последней на вход схемы И 6 продолжает подаваться сигнал с уровнем логического О, По сигналу "1И Управления" (фиг.5e) поступающего на вход схемы 19 управления ключами задатчика 12 порогового уровня (фиг. 2), при наличии на ее первом входе сигнала с уровнем логической "1" с выхода блока 11 памяти схема 19 управления ключами срабатывает и посредством ключей 18 и резистивных делителей 20 (фиг. 2) формирует на выходе эадатчика 12 порогового уровня выходной сигнал низкого уровня (например, Г,-= — 0,1ВР, уровень которого абес11ечивает срабатывание амплитудного дискриминатора 4 при низких уровнях вибраций, в том числе и на неработающем иэделии. 55

Вследствие этого амплитудный дискриминатор 4, если он исправен, срабатывает на протяжении времени (фиг. 5и) . При срабатывании амплитудного дискриминатора 4 с его первого выхода на один из входов задатчика

12 порогового уровня поступает сигнал, который вызывает понижение до заранее определенного значения уровня эталонного напряжения, поступающего на второй вход амплитудного дискриминатора 4, благодаря чему обеспечивается устойчивая выдача сигнала о превышении допустимого уровня вибраций при возможном уменьшении значения напряжения íà его первом входе вследcraze колебания уровня вибраций в -заранее установленных пределах. Сигнал с второго выхода дискриминатора 4 с уровнем логической "1" (фиг.5и) подается на вход схемы И-НЕ 14, вход блока 11 памяти и на входы инвертора

HF. 28, вход I триггера 30 и вход элемента И-НЕ 32 блока 10 отказа (фиг.4).

Схема И-НЕ 14 не срабатывает и уровень сигнала на ее выходе не изменяется, так как в это время на ее вход подается сигнал "ОИ Запрета" с уровнем логического "О" (фиг. 5г, и).

Выходной сигнал блока 11 памяти остается прежним, так как сигнал "1И Запоминания" в момент времени t )t, отсутствует. Поэтому в момент времени t q (t t срабатывает элемент

И-НЕ 32 блока 10 отказа, так как на оба его входа в это время подаются сигналы с уровнем логической "1": на один вход — с выхода амплитудного дискриминатора 4, а на другой — с выхода О триггера 30 блока 10 отказа (фиг. 4) . Вследствие этого в общей точке соединения выходов элементов

И-HE 31 и 32 на входе I триггера 34 и входе инвертора НЕ 33 устанавливается сигнал с уровнем логического

"О", а на входе К триггера 34 — сигнал с уровнем логической "1" (фиг.4).

В промежуток времени Г. 3 - 4 на вход Т триггера 34 поступает сигнал

"1И Отказа" (фиг. 5ж). Триггер 34 не переключается и остается в исходном состоянии, т.е. на выходе О триггера 34, соединенном с входом схемы

И 6 и индикатором 8, остается сигнал

l с уровнем логической "1", который не препятствует работе схемы И 6.

Если амплитудный дискриминатор 4 неисправен, то при подаче в промежуток времени г — с на его второй вход, например U»= -0,1В, он не срабатывает и сигнал на его втором выходе оста1537856!

2 ется прежним, с уровнем логического

"0". Этот сигнал, поступая на вход элемента И-НЕ 32, не вызывает его срабатывания в момент времени

Поэтому на выходах элементов И-НЕ 31 и 32,входе I триггера 34 и входе инвертора НЕ 33 устанавливается сигнал с уровнем логической "1", а на входе К триггера 34 блока 10 отказа — сигнал- с уровнем логического "0".

В связи с этим поступление сигнала

"1И Отказа" на Т-вход триггера 34 вызывает срабатывание триггера 34 и . на его выходе Q после окончания curIl 11

15 нала 1И Отказа устанавливается потенциал с уровнем логического "0".

Этот сигнал поступает на один из входов схемы И 6 и выход индикатора 8 °

В момент времени t< действие сигнала "1И Управления" (фиг.5e) прекращается и на выходе эадатчика 12 порогового уровня устанавливается прежний, предшествующий контролю, уровень.

Вследствие этого амплитудный дискри- 25 минатор 4 переключается, если он исправен, и на его выходе устанавливается прежний, предшествующий контролю, уровень логического О" (фиг.5и) °

В момент времени t действие сигнала "ОИ Запрета" с уровнем логического "0" прекращается и на вход схемы И-НЕ 14 с выхода блока 9 управления подается сигнал с уровнем логической "1", который не препятствует работе схемы И-НЕ 14 (фиг.5г).

В промежуток времени t <-t 7 на вход блока 11 памяти и через элемент ИЛИ

29 на R-вход триггера 30 подается сигнал "ОИ Окончания контроля" (фиг.5з), который устанавливает их в исходное состояние. При этом с выхода блока 11 памяти на второй. вход схемы ИЛИ-НЕ 15 подается сигнал с уровнем логической "1", который не препятствует работе схемы ИЛИ-НЕ 15.

Проверка исправности амплитудного дискриминатора 4 окончена, ограничитель вибраций готов к штатной работе.

Поступление сигнала с уровнем ло11 ll

50 гического 0 на один иэ входов схемы

И 6 (фиг. 1 и 4) запрещает прохождение остальных сигналов, поступающих на ее другие входы, и блокирует включение исполнительного механизма 7 до следующего цикла контроля, если не55 исправность амплитудного дискриминатора 4 устранится в процессе работы.

Поступление сигнала с уровнем логического "б" на вход индикатора 8 включает последний, который сигнализирует о наличии неисправности (отказа) несработавшего амплитудного дискриминато ра 4.

Таким образом, в ходе пров ерки исправности амплитудного дискриминатора 4 при U „„= 0 и при наличии неисправности последнего блок 10 отказа обеспечивает выдачу на индикатор

8 сигнала о неисправности амплитудного дискриминатора 4 и блокирует включение исполнительного механизма 7.

В промежуток времени -t, на вход блока 11 памяти и через элемент ИЛИ

29 на R-вход триггера 30 (фиг.4) подается сигнал ОИ Окончания контроля 1 (фиг, 5з), который устанавливает их в исходное состояние.

Fсли на втором выходе амплитудного дискриминатора 4 перед началом контроля установлен уровень логической

"1", что соответствует состоянию выдачи сигнала о превышении уровня допустимой вибрации (фиг. 5л), то после подачи сигнала "1И Запоминания" (фиг. 5в) на входы блока 11 памяти и блока 10 отказа (фиг.4) на выходе блока 11 памяти устанавливается сигнал с уровнем логического "0" (фиг. 5м), а триггер 30 блока 10 отказа устанавливается в состояние„ при котором на его выходе Ц будет установлен сигнал с уровнем логической

"1 1, а на выходе 0 — сигнал с уровнем логического "0".

С выхода блока 11 памяти еигнал с уровнем логического "0" подается на вход схемы ИЛИ-HF. 15 (фиг. 1 и 4) и на вход схемы 19 управления ключами (фиг. 2) на все время проверки исправности (фиг.5м). Поступление на второй вход схемы И!!!1-IIF, 15 сигнала с уровнем логического "0" удерживает на ее выходе уровень логической "1" на все время произведения контроля исправности, чем обеспечивается поддержание неизменным состояния исполнительного механизма 7,если он был включен перед началом контроля, Сигнал "ОИ Запрета" (фнг.5г), поступая на вход схемы !1-1!Е 14 (фиг.4), на протяжении всего цикла контроля препятствует прохожденин через ее другой вход изменяннцсгося в процессе контроля исправности сигнала с выхода амплитудного днсн риминатора 4, если последний иснрвllt ll а поэтому

1537856!

20

35

45 изменения уровней выходных сигналон амплитудного дискриминатора 4 с "1" в "О", (или с "О" в "1"), как в предыдущем случае, а также после окончания сигнала "1И Управления", в процессе проведения проверки исправности в промежутке времени (или tg-t ) не передаются на исполнительный механизм 7.

В момент времени t при паступлении на первый вход схемы 19 управления ключами задатчика 12 порогового уровня (фиг.2) сигнала "1И Управления" (фиг.5е) и при наличии на ее !

5 втором входе сигнала с выхода блока

11 памяти с уровнем логического "О" (фиг. 5м) последняя срабатывает и посредством ключей 18 и резистинных делителей 20 формирует на выходе резистивных делителей 20 сигнал, например Б, = 7,0 В, который подается на второй вход амплитудного дискриминатора 4.

Уровень Ц,= 7В обеспечивает вы- 25 ключение амплитудного дискриминатора

4 даже при уровне сигнала на его первом нходе, соответствующем предельно допугтимым вибрациям, например U npe4 ц р 6 3 В.

Амплитудный дискриминатор 4, если он исправен, в момент времени t< переключается и на его втором выходе устанавливается сигнал с уровнем логического "О" (фиг. 5л). Этот сигнал подается на соответствующие входы схемы И-HF. 14, блока 11 памяти и блока 10 отказа (фиг.4).

Схема И-fIE 14 в промежуток времени — t + не срабатывает, так как в течение этого времени на ее вход продолжает поступать сигнал "ОИ Запрета" (фиг.5г) с уровнем логического "О". Выходной сигнал с блока 11 памяти в промежуток времени также не изменяетгя. Элемент И-НЕ 32 блока 10 отказа не срабатывает, так как на его вход с выхода ч триггера

30 подается сигнал с уровнем логического "О".

В промежуток нремечи -t > сраба50 тывает только элемент И-HF 31 блока

10 отказа (в течение этого периода на его выходы подаютгя сигналы с уровнем логическои 1 с выхода Q триггера 30 и с выхода инвертора HE 28, фиг. 4) и на его выходе устанавливается сигнап с уровнем логического

"0"

В промежуток времени tq-t на вход Т триггера 34 блока 10 отказа (фиг. 4) поступает сигнал "1И Отказа" (фиг. 5ж) . Ввиду того, что в промежуток времени t -t на Э-вход триггера 34 подается сигнал с уровнем логического "О" и на вход К вЂ” сигнал с уровнем логической "1" с выхода инвертора 33 HF, то после воздействия сигнала "1И Отказа" триггер 34 устанавливается в состояние, при котором на его ныходе Q устанавливается сигнал с уровнем логической "1", т.в, уровень, соответствующий исходному состоянию, как и после воздействия сигнала ОИ Установки "О".

Этот сигнал с уровнем логической 1 подается на один из входов схемы И Ь и разрешает ее нормальное функционирование.

В момент времени прекращается действие сигнала "1И Управления" (фиг. 5e ), схема 19 управления ключами выключается, выключая и ключи 18, уровень сигнала на выходе задатчика

12 порогового уровня возвращается в исходное, предшествующее контролю, состояние. Вследствие этого амплитудный дискриминатор 4 грабатывает (фиг.5J1) и на его ныходе устанавливается сигнал с уровнем логической

lt (tl т.е. таким же, как перед проверкой ис.правности.

В момент времени Т прекращается действие сигнала ОИ Запрета (фиг.5г) и сигнал с выхода амплитудного дискриминатора 4 через вход схемы И-НЕ 14 начинает подаваться на вход схемы IDH — НЕ 15 (фиг. 4), на другом входе которой еще прис утс тв ует сигнал с уровнем логического "О" с выхода блока 11 памяти (фиг.5м).

В промежуток времени t -t 1 с выхода блока 9 управления через вход элемента ИЛИ 29 на вход R триггера 30 блока 10 отказа (фиг.4) поступает сигнал "ОИ Окончания контроля" (фиг.5э) и триггер 30 устанавливается в исхоц1 ое, как и после воздействия сигнала

ОИ Установки "0, cocòîÿíèå ° Цикл проверки исправности окончен и на вход схемы И-НЕ 14 с выхода блока 9 управления, на уход схемы !1ЛИ вЂ” HF 15 с выхода блока 11 памяти, на один из входов схемы И 6 с выхода блока 10 от-. каза, как и после включения питания, подаются сигналы с уровнем логичес1537856

16 кой "1", и ограничитель вибраций готов к работе.

Таким образом, ограничитель вибраций обеспечивает проверку исправности

5 амплитудного дискриминатора 4, находящегося в состоянии выдачи сигнала о превышении вибрации, и, несмотря на переключение амплитудного дискриминатора 4, во время контроля о6еспе- 10 чивает сохранение включенного состояния исполнительного механизма 7 при исправном амплитудном скриминаторе 4.

Если амплитудный дискриминатор 4 неисправен (или на его первый вход подается сигнал, например, с напряжением U g ) 7,0 В с выхода преоб-. разователя 3 переменного напряжения в постоянное, что соответствует неисправности последнего), то в промежуток времени - g дискриминатор 4 не переключается и на его втором выходе сигнал с уровнем логической 1 остается неизменным. Уровни выходных сигналов схемы И-НЕ 14 и блока 11 памяти (фиг. 5м) в промежуток времени

t< — t > не изменяются по описанным выше причинам, а уровень сигнала на выходе Q триггера 34 блока 10 отказа изменится.

В промежуток времени t -t на вход элемента И-НЕ 31 с выхода инвертора

HE 28 подается сигнал с уровнем логического "0!, поэтому íà его выходе устанавливается сигнал с уровнем логической "1". На выходе элемента

И-HE 32 также устанавливается сигнал с уровнем логической "1", так как с момента начала контроля с выхода ч триггера 30 (описано выше) на его вход подается сигнал с уровнем логического "0".

Следовательно, в промежуток времени Ч t 5 с общей точкой выходов элементов И-НЕ 31 и 32 на вход 3

45 триггера 34 подается сигнал с уровнем логической "1", а на вход К триггера 34 через инвертор HF. 33 — с уровнем логического "0". Поэтому поступающий на Т-вход триггера 34 в промежуток времени t — сигнал 1И Отка!

1 50

3 Ф за" (фиг. 5ж) вызывает переключение

IK-триггера 34 и с момента времени на выходе 0 последнего устанавли4 вается сигнал с уровнем логического

"0". Этот сигнал прекращает прохожде- ние остальных сигналов, поступающих на другие Bxo l схемы И 6, и вызывает срабатывание индикатора 8, сигнализирующего о наличии неисправности (отказа) амплитудного дискриминатора 4. Прекращением прохождения через схему И 6 сигнала с уровнем логической "1" при неисправности амплитудного дискриминатора 4 обеспечивается отключение исполнительного механизма 7, т.е. проведением контроля исправности предотвращается ложная выдача сигнала о превышении уровня вибраций при "активном" отказе амплитудного дискриминатора 4, чем повышается надежность устройства, удобство эксплуатации и достоверность выдаваемых этим устройством сигналов.

Таким образом, ограничитель обеспечивает обнаружение неисправности канала контроля уровня вибрации как на неработающем ГТД, что позволяет проводить контроль и проверку работоспособности устройства без съема последнего с объекта и уменьшает тем самым время предпусковой подготовки системы контроля ГТД и самого

ГТД к работе, так и на работающем ГТД без изменения состояния исполнительного механизма. Это повышает надежность выдачи сигнала о превышении опасной вибрации и позволяет применять устройство в системах автоматизированного контроля объекта, обеспечивая оперативное принятие мер для своевременного устранения неисправностей, могущих повлечь к возникновению аварийных ситуаций. формула и з о б р е т е н и я

Ограничитель вибраций газотурбинного двигателя, содержащий последовательно соединенные датчик вибраций, фильтр, преобразователь и амплитудный дискриминатор, последовательно соединенные тахометрический сигнализатор, схему И и исполнительный механизм, индикатор, о т л и ч а ю щ и йс я тем, что, с целью повышения надежности, он дополнительно содержит блок управления, блок отказа, блок памяти, задатчик порогового уровня, источник эталонного напряжения, схему

И-НЕ, схему ИЛИ-HF,, шину внешнего запуска контроля и шину установки, подключенную к первым входам блока управления, блока отказа и блока памяти и второму входу схемы И, третий вход которой подключен к входу индикатора

1537856 и выходу блока отказа, второй вход которого подключен к первому выходу

I амплитудного дискриминатора, второму входу блока памяти и первому входу схемы И-НЕ, второй вход которой подключен к первому выходу блока управления, а выход — к первому входу схемы ИЛИ-НЕ, второй вход которой подключен к первому входу эадатчика порогового уровня и выходу блока памяти, а выход — к четвертому входу схемы И, шина внешнего запуска контроля подключена к второму входу блока управления, третий вход которого подключен к второму выходу тахометрического сигналиэатора, второй, тре. тий и четвертый выходы — соответственно к третьему, четвертому и пятому входам блока отказа, а пятый выход к второму входу эадатчика порогового уровня, третий вход которого подключен к второму выходу амплитудного дискриминатора, четвертый вход— к выходу источников эталонного напряжения, а выход — к второму входу амплитудного дискриминатора, трет и и четвертый выходы блока управления гадключены к третьему и четвертому вхопам блока памяти.

1537856

АналогоА|й сиеяал

Фиг Ф

Составитель В, Колясников

Техред Л.Олийнык

Корректор О. Кравцова

Редактор F,. Папп

Заказ 154 Тираж 434 Подписное

BHHHIIH IocyäàðñTâåííoão комитета по изобретениям и открытиям прн ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

tl II ,Ip ичводствепно-издательский комбинат Патент,,г. Ужгород, ул. Гагарина, 101