Мажоритарный элемент

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации. Целью изобретения является расширение функциональных возможностей и области применения путем обеспечения мажоритарных функций "5 или более из 9" и "6 или более из 11". Мажоритарный элемент содержит первый 1 и второй 2 коммутаторы "1 из 8" с входами стробирования, семь входов 7-13 переменных, элементы И 18-20, элементы ИЛИ 26 и 27, шины нулевого 21 и единичного 22 логических сигналов. Для достижения поставленной цели в устройство дополнительно введены третий 3 и четвертый 4 коммутаторы "1 из 8", дешифратор 5 с тремя входами и восемью выходами, пороговый элемент 23 "4 или более из 5", пороговый элемент 24 "3 или более из 5", пороговый элемент 25 "2 или более из 5", восьмой 14, девятый 15, десятый 16 и одиннадцатый 17 входы переменных мажоритарного элемента. 5 ил.

СОЮЗ СОВЕТСНИХ

СООИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (!9) (1И (51)5 Н 03 K 19/23

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ф()М) V(XS) 72(Хб) ГОСУДАРСТВЕННЫЙ КОМИТЕТ

Г10 ИЗОБРЕТЕНИЯМ И ОТНРЬГГИЯМ

ПРИ ГКНТ СССР

1 (21) 4479140/24-21 (22) 30.08.88 (46) 23.01.90. Бюл. tF 3 (72) В.Ш.Арутюнян и А.К.Аракелян (53) 681.325.65 (088.8) (56) Абугов Ю.О., Диденко К.И., Загарий Г.И. и др. Микроэлектронные устройства программного и логического управления. - М.:Машиностроение, 1979, с. 41, рис. 21б.

Авторское свидетельство СССР

К 1448406, кл. Н 03 К 19/23, .

16.11.87.

2 (54) МАЖОРИТАРНЫЙ ЭЛЕМЕНТ (57) Изобретение относится к цифровой автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации, Целью изобретения является расширение функциональных воэможностей и области применения путем обеспечения мажоритарных функций "5 или более 9" и

"6 или более из 11". Мажоритарный элемент содержит первый 1 и второй

2 коммутаторы "1 из 8" с входами стро1538249

1 бирования, семь входов 7-13 переменных, элементы И 18-20, элементы ИЛИ

26 и 27, шины нулевого 21 и единичного 22 логических сигналов. Для достижения поставленной цели в устройство дополнительно введены третий 3 и четвертый 4 коммутаторы "1 из 8", дешифратор 5 с тремя входами и восеИзобретение относится к цифровой автоматике и вычислительной технике . и может быть использовано для построf5 ения различных устройств переработки дискретной информа ции.

Целью изобретения является расширение функциональных возможностей и,области применения за счет обеспеI чения мажоритарных функций "5 или более из 9" и "6 или более из 11".

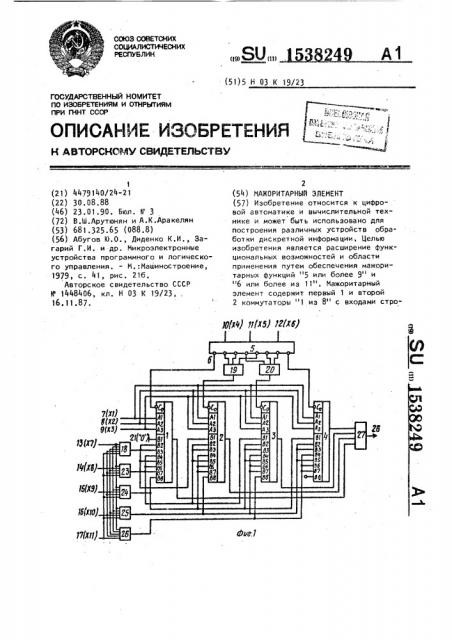

На фиг. 1 представлена функциональная схема предлагаемого мажоритарного элемента; на фиг. 2 — функцио-.

Нальная схема порогового элемента

"4 или более из 5"; на фиг. 3 - функциональная схема порогового элемента

1 3 или более из 5"; на Фиг. 4 - функ30

Циональная схема порогового элемента

"2 или более из 5".

Предлагаемый мажоритарный элемент (фиг.1) содержит первый 1, второй 2, третий 3 и четвертый 4 коммутаторы

"1 из 8", дешифратор 5, первый выход

6 которого соединен со стробирующим входом первого коммутатора 1, а восьмой выход — со стробирующим входом 0 четвертого коммутатора 4, первый 7, второй 8, третий 9 входы переменных соединены соответственно с. адресными входами всех коммутаторов 1-4, четвертый 10, пятый 11 и шестой 12 входы переменных, соединенные соответственно с входами дешифратора 5, седьмой

13, восьмой 14, девятый 15, десятый

16 и одиннадцатый 17 входы переменных, первый логический элемент И 18, входы которого соединены с седьмым 13, восьмым 14, девятым 15, десятым 16 и одиннадцатым 17 входами переменных, а выход - с вторым, третьим, пятым информационными входами первого ком55 мутатора 1 и с первым информационным входом второго коммутатора 2, второй элемент И 19, входы которого соединены с вторым, третьим и пятым выходамью выходами, пороговый элемент 23

"4 или более из 5", пороговый элемент 24 "3 или более из 5", пороговый элемент 25 "2 или более из 5", восьмой 14, девятый 15, десятый 16 и одиннадцатый 17 входы переменных мажоритарного элемента. 3 з.п.ф-лы, 4 ил.,ми дешифратора 5, а выход - со стробирующим входом второго коммутатора

2, третий элемент И 20, входы которого соединены с четвертым, шестым и седьмым выходами дешифратора 5, а выход — со стробирующим входом третьего коммутатора 3, шину 21 нулевого логического сигнала, соединенную с первым информационным входом первого коммутатора 1, шину 22 единичного логического сигнала, соединенную с восьмым информационным входом четвертого коммутатора 4, пороговый элемент

"4 или более из 5" 23, входы которого соединены с седьмым 13, восьмым

14, девятым 15, десятым 16 и одиннадцатым 17 входами переменных, à Bblход — с четвертым, шестым, седьмым информационными входами первого коммутатора 1, с вторым, третьим, пятым информационными входами второго коммутатора 2 и с первым информационным входом третьего коммутатора 3, пороговый элемент "3 или более из 5" 24, входы которого соединены с седьмым 13, восьмым 14, девятым 15, десятым 16 и одиннадцатым 17 входами переменных, а выход - с восьмым информационным входом первого коммутатора 1, с четвертым, шестым, седьмым информационными входами второго коммутатора 2, с вторым, третьим и пятым информационными входами третьего коммутатора

3 и с первым информационным входом четвертого коммутатора 4, пороговый элемент "2 или более из 5" 25, входы которого соединены с седьмым 13, восьмым 14, девятым 15, десятым 16 и одиннадцатым 17 входами переменных, а выход - с восьмым информационным входом второго коммутатора 2, с четвертым, шестым, седьмым информационными входами третьего коммутатора 3 и с вторым, третьим, пятым информационными входами четвертого коммутатора 4, первый элемент ИЛИ 26, входы

1538249

20

45 которого соединены с седьмым 13, восьмым 14, девятым 15, десятым 16, одиннадцатым 17 входами переменных, а выход - с восьмым информационным входом третьего коммутатора 3 и с четвертым, шестым, седьмым информационными входами четвертого коммутатора 4, второй элемент ИЛИ 27, входы которого соединены с выходами коммута торов 1-4, а его выход является выходом 28 мажоритарного элемента.

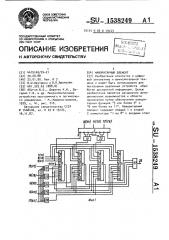

Пороговый элемент "4 или более из

5" 23 (фиг.2) содержит коммутатор

29 со структурой "1 из 8", адресные входы которого соединены соответственно с седьмым 13, восьмым 14 и девятым 15 входами переменных мажоритарного элемента, первый, второй, третий и пятый информационные входы соединены с шиной 21 нулевого логического сигнала, а выход — с выходом порогового элемента 23, элемент

И 30, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выход — с четвертым, шестым и седьмым информационными входами коммутатора 29, элемент ИЛИ

31, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выход - с восьмым информационным входом коммутатора 29.

Пороговый элемент "3 или более из 5" 24 (фиг.3) содержит коммутатор

32 со структурой "1 из 8", адресные входы которого соединены соответственно с седьмым 13, восьмым 14 и девятым 14 входами переменных, первый информационный вход - с шиной 21 нулевого логического сигнала, восьмой информационный вход - с шиной

22 единичного логического сигнала, а выход - с выходом порогового элемента 24, элемент И 33, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выходс вторым, третьим и пятым информационными входами коммутатора 32, элемент ИЛИ 34, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выход - с четвертым, шестым и. седьмым информационными входами коммутатора 32.

Пороговый элемент "2 или более из 5" 25 (фиг.4) содержит коммутатор

35 со структурой "1 из 8", адресные входы которого соединены соответственно с седьмым 13, восьмым 14 и девятым 15 входами переменных, а выход -. с выходом порогового элемента 25, элемент И 36, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выход — с первым информационным входом коммутатора 35, элемент ИЛИ 37, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выход с вторым, третьим и пятым информационными входами коммутатора 35, четвертый, шестой, седьмой и восьмой информационные входы которого соединены с шиной 22 единичного логического сигнала.

Предлагаемый мажоритарный элемент работает следующим образом.

Для реализации мажоритарной функции "6 или более из 11" к шинам 7-17 подаются входные переменные Х1-Х11

При этом, если в кодовых комбинациях входных переменных Х1-Х11 содержатся шесть или более логических единиц ("1"), то на выходе 28 мажоритарного элемента появляется единичный логический сигнал, а в остальных случаях нулевой логический сигнал ("0").

Реализация мажоритарной функции

"5 или более из 9" осуществляется при приложении к двум из входов переменных постоянных нулевых сигналов, а к остальным входам — девяти переменных Х.

Аналогично этому для реализации мажоритарной функции "4 или более из 7" постоянные нулевые сигналы прикладываются к четырем входам переменных, для реализации мажоритарной функции "3 или более из 5" - к шести входам переменных, а для реализации мажоритарной функции "2 или более из

3" — к восьми входам переменных. на выходе порогового элемента "4 или более из 5" 23 единичные сигналы возникают в тех случаях, когда на его входах переменных прилагаются коды с четырьмя и пятью единицами, а в остальных случаях — возникает нулевой сигнал. Единичные сигналы возникают на выходе порогового элемента "3 или более из 5" 24 в тех случаях, когда на его входах переменных подаются коды с тремя, четырьмя и пятью единицами. Единичные сигналы

ВОзникают нд ВыхОде пОрОГОВОГО элемента "2 или более из 5" 25 в тех случаях, когда в кодах входных переменных содержатся два, три, четыре или пять единиц, 153824

Таким образом, мажоритарный элемент реализует широкий класс мажоритарных логических функций, что свидетельствует о его широких функциональных возможностях и области применения, формула изобретения

Мажоритарный элемент, содержа щий первый и второй коммутаторы "I из 8" с входами стробирования, семь

;входов переменных, первый, второй и третий из которых соединены соответственно с адресными входами пер, вого и второго коммутаторов, первый ( элемент И, первый вход которого соединен с седьмым входом переменных, а выход. - с вторым, третьим, пятым 20 информационными входами первого ком мутатора и с первым информационным

:входом второго коммутатора, первый элемент ИЛИ, первый вход которого .соединен с седьмым входом переменных, 25 второй элемент ИЛИ, первый и второй

, входы которого соединены с выходами первого и второго коммутаторов, а выход - с выходом мажоритарного элемента, шину нулевого логического 30 сигнала, которая соединена с первым информационным входом первого комму татора, шину единичного логического сигнала, четвертый, шестой и седьмой информационные. входы первого коммутатора соединены с вторым, третьим и пятым информационными входами второго коммутатора, восьмой информационный вход первого коммутатора соединен с четвертым, шестым и седьмым 0 информационными входами второго коммутатора, отличающийся тем, что, с целью расширения функциональных возможностей и области применения за счет обеспечения мажори gg тарных функций "5 или более из 9" и

"6 или более из 11 дополнительно содержит третий и четвертый коммутаторы "1 из 8", дешифратор с тремя входами, которые соединены соответственно с четвертым, пятым -и шестым входами . переменных мажоритарного элемента, и восьмью выходами, первый из которых соединен с входом стробирования первого коммутатора, а восьмой " с входом стробирования четвертого коммутатора, второй элемент И, входы которого соединены с вторым, третьим и пятым выходами дешифратора, а вы9 в ход - с входом стробирования второго коммутатора, третий элемент И, входы которого соединены с четвертым, шес" тым и седьмым выходами дешифратора, а выход - с входом стробирования третьего коммутатора, пороговый элемент "4 или более из 5", первый вход которого соединен с седьмым входом переменных мажоритарного элемента, а выход - с четвертым, шестым, седьмым информационными входами первого коммутатора, с вторым, третьим, пятым информационными входами второго коммутатора и с первым информационным входом третьего коммутатора, пороговый элемент "3 или более из 5", первый вход которого соединен с седьмым входом переменных мажоритарного элемента, а выход - с восьмым информационным входом первого коммутатора, с четвертым, шестым, седьмым информационными входами второго коммутатора, с вторым, третьим пятым информационными входами третьего коммутатора и с первым информационным входом четвертого коммутатора, пороговый элемент "2 или более из 5"„ первый вход которого соединен с седьмым входом переменных мажоритарного элемента, а выход — с восьмым информационным входом второго коммутатора, с четвертым, шестым, седьмым информационными входами третьего коммутатора с вторым, третьим,. пятым информационными входами четвертого коммутатора, восьмой, девятый, десятый и одиннадцатый входы переменных мажоритарного элемента соединены соответственно с вторыми, третьими, четвертыми и пятыми входами первого элемента И, пороговых элементов н4 или более из 5", "3 или более из 5", "2 или более из

5" и первого элемента ИЛИ, выход которого соединен с восьмым информационным входом третьего коммутатора и с четвертым, шестым, седьмым информационными входами четвертого коммутатора, выходы третьего и четвертого коммутаторов соединены с дополнительно введенным третьим и четвертым входами второго элемента ИЛИ, а восьмой информационный вход четвертого коммутатора соединен с шиной единичного логического сигнала.

2. Элемент по п.1, с т л и ч а юшийся тем, что пороговый элемент

"4 или более из 5" содержит коммутатор "1 из 8", адресные входы которо1538249

5 (Х 70)

77(Х77) го соединены с седьмым, восьмым и девятым входами переменных мажоритарного элемента, первый, второй, третий и пятый информационные входы - с шиной нулевого логического сигнала, а выход - с выходом порогового элемента "4 или более из 5", элемент И, входы которого соединены с десятым и одиннадцатым входами переменных мажо- lg ритарного элемента, а выход - с четвертым, шестым и седьмым информационными входами коммутатора, элемент

ИЛИ, входы которого соединены с десятым и одиннадцатым входами перемен- 15 ных мажоритарного элемента, а выход - с восьмым информационным входом коммутатора.

3. Элемент по п.l, о:т л и ч а юшийся тем, что пороговый эле мент "3 или более из 5" содержит коммутатор "1 из 8", адресные входы которого соединены с седьмым, восьмым и девятым входами переменных мажоритарного элемента, первый информа- 25 ционный вход - с шиной нулевого логического сигнала, восьмой информационный вход - с шиной единичного логического сигнала, а выход - с выходом порогового элемента "3 или ЗО более из 5", элемент И, входы которого соединены с десятым и одиннадцатым входами переменных мажоритарного элемента, а выход - с вторым, третьим и пятым информационными входами коммутатора, элемент ИЛИ, входы которого соединены с десятым и одиннадцатым входами переменных мажоритарного элемента, а выход - с четвертым, шестым и седьмым информационными входами коммутатора.

4. Элемент по п.l, о т л и ч а юшийся тем, что пороговый элемент

"2 или более из 5" содержит коммутатор "1 из 8", адресные входы которого соединены с седьмым, восьмым и девятым входами переменных мажоритарного элемента, четвертый, шестой, седьмой и восьмой информационные входы - с шиной единичного логического сигнала, а выход - с выходом порогового элемента "2 или более из

5", элемент И, выходы которого соединены с десятым и одиннадцатым входами переменных мажоритарного элемента, а выход - с первым информациoHHbIM входом коммутатора, элемент

ИЛИ, входы которого соединены с десятым и одиннадцатым входами переменных мажоритарного элемента, а выходс вторым, третьим и пятым информационными входами коммутатора.

153824

6(n)

t>9e) (spa) г((т)

l6(310) а(ц) ггГ ") о п) .

19(x8)

ts(xs)

5(Ю)

УРЩ

Составитель О.Скворцов

Редактор И.Дербак Техред Л.Сердюкова Корректор Т.Малец

Заказ 173 Тираж 644 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно -издательский комбинат "Патент", r. Ужгород, ул. Гагарина,101