Устройство определения перерывов цифрового сигнала в радиоканале

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Устройство определения перерывов цифрового сигнала в радиоканале содержит выделитель 1 фронтов, блок фазирования 2, формирователи 3 и 4 импульсов, соответствующих центру посылки, а также началу и концу посылки, эл-ты И 5 и 6, блок задержки 7 и интегратор 8. Для повышения помехоустойчивости в устройство введены вычитающий счетчик 9 дешифраторы 10 и 11, блоки задержки 12 и 13, эл-т ИЛИ 14 и RS - триггер 15. 1 з.п.ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

А0 ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

11РИ ГННТ СССР

1 (2!) 4399852/24-09 (22) 28.03 ° 88 (46) 23 ° 01.90. Бил, М 3 (72) В.А.Молотков, И.H.Аронштам, Ю.С.Ицкович, K.È.Крюков и Н.А.Кузнецов (53) 621.396.43(088.8) (56) Шляпоберский В.И. Основы техники передачи дискретных сообщений.

N.: Связь, 1973, с.287-289.

Авторское свидетельство СССР

Р 390676, кл. H 04 1 3/06, !971. (54) УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ПЕРЕРЫВОВ ЦИФРОВОГО СИГНАЛА В РАДИОКАНАЛЕ

„„SU„„ t 538262 Д1 (51) 5 Н 04 J 3/06

2 (57) Изобретение относится к электросвязи. Цель изобретения — повышение помехоустойчивости. Устр-во определения перерывов цифрового сигнала в радиоканале содержит выделитель 1 фронтов, блок фазирования 2, формирователи 3 и 4 импульсов, соответствующих центру посылки, а также началу и концу посылки, эл-ты И 5 и 6, блок задержки 7 и интегратор 8. Для повышения помехоустойчивости в устр-an введены вычитающий счетчик 9, дешйфраторы 10 и 11, блоки задержки

12 и 13, эл-т ИЛИ 14 и RS-триггер 15.

1 з.п. ф-лы, 2 ил.

1538262!!забретение относится к области лектросвязи и может быть использоваЙо в системах радпателеуправления телесигнализацпи, использующих режим 5 синхронной связи с перерывами при

Необходимости фиксации возникновения

g.âàðèéHûõ телесигналов во время перерьиов связи.

Целью изобретения является повыше- 1О ле помехоустойчивости.

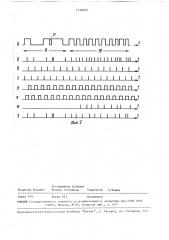

Па фнг.1 представлена электричесая схем» устройства определения песрьшов цифрового сигнала в радиокаж е", па фиг.2 — временные диаграммы 15 игналов, поясняющие работу устройти» о,ределения перерывов цифрового игиала в. радиоканале.

Устройство определения перерывов ифраваго сигнала в радиоканале со- 20 ержит выделитель I франтов, блок 2 азирования, формирователь 3 импульав, соответствующих центру посылки, ормирователь 4 импульсов, соответстующих пачалу и концу посылки, первый 25 ф и второй 6 элементы И, блок 7 заф ержки, интегратор 8, вычитающий счетчик 9, первый 10 и второй 11 дешифратары, первый 12 и второй !3 дополнительные блоки задержки, элемент ИЛИ 30

14, 8S-триггер 15. устройство определения пЕрерывов цифрового сигнала в радиоканале рабо- тает следующим образом. !

Поступивший с линии связи детер35

Мированпый цифровой сигнал !6 (фиг.2a) начинает действовать на входе выделителя (фиг.1), с выхода которого через блок 7 задержки импульсы (фнг.2б) подаются на входы перво-. го 5 и второго 6 элементов.

С второго выхода блока 2 фазирова ния тактовые импульсы (фиг.2в) поступают на формирователь 3, а на его 45

Выходе формируются прямоугольные импульсы (фиг,2д), длительности которых равны половине периода тактовых им"

Пульсов (фиг.2б,г). Тактовые имПульсы (фиг.2г) от блока 2 фаэироваНил подаются на формирователь 4 им50 пульсов, соответствующих началу и

Концу посылки, на выходе которого от

Переднего и заднего фронтов посылки формируются равные по длительности

Импульсы (фиг.2е). Сумма длительностей последних за тактовый период равна половине периода тактовых импуль" сов.

Тактовые импульсы (фиг.2в,г) от блока 2 фазирования имеют одинаковую частоту и сдвинуты между собой на половину тактового периода. С выхода формирователя 3 импульсы поступают на первый элемент И 5, а с выхода формирователя 4 — на второй элемент

И 6.

Поскольку импульсы, полученные на выходе выделителя 1, задерживаются в блоке 7 задержки при этом они находятся примерно в середине фазовых зон, соответствующих началу и концу каждой иэ посылок (фиг.2е), то все импульсы (фиг.2з) от фронтов и . .импульсы от провала 17 (фиг.2а) детерминированной посылки, поступившие с выхода делителя 1, через блок 7 задержки проходят через второй элемент

И 6 и. поступают на вычитающий вход реверсивного счетчика 8. Предварительно сигналом низкого уровня с третьего устанавливающего входа устройства через элемент ИЛИ 14 в интегратор 8, выполненный в виде реверсивного счетчика, записывается числом с первого устанавливающего входа устройства, которое превышает в два раза число., вводимое в реверсивный счетчик 8 (в случае, если разрядность реверсивного счетчика 8 и вычитающего счетчика одна и та же).

Сигнал на выходе второго дешифратора 11 появляется при нулевом состоянии вычитающего счетчика 9, При наличии в канале связи детерминированного. сигнала происходит периодическое формирование импульсов на выходе . первого дешифратора 10, поддерживаю.щих ВВ-триггер 15 в состоянии "1".

При этом содержимое вычитающего счетчика 9 не успевает уменьшиться до нуля, поэтому импульсы на выходе второго дешйфратора 11 не формируются.

При перерыве цифрового сигнала 16 (фиг.2а) на вход выделителя поступает шум 18 (фиг.2а), уровень которого соизмерим с уровнем цифрового сигнала, что объясняется наличием автоматической регулировки усиления в приемном устройстве радиоканала.

На выходе выделителя 1 возникают импульсы (фиг.2ж) в момент прохождения шумового напряжения через нуль, которые через блок 7 задержки поступают на первый 5 и второй 6 элементы И. Поскольку импульсы (фиг.2ж) от случайного шума распределены рав1538262 номерно в интервале всей длительности посылки, а длительность центральных импульсов (фиг.2д) равны сумме длительностей импульсов начала и

5 конца посылки (фиг.2е), то появление импульсов (фиг.2ж,з) с выходов перфого 5 и второго 6 элементов И равновероятно.

Фазовое смещение выходных сигна- 10 лов первого 5 и второго 6 элементов, соответствующих временному расположению центральной части и боковым частям элементарной посылки, интегрируется реверсивным счетчиком 8.

При этом импульсы (фиг.2ж,э) из-за различного управляющего воздействия их на реверсивный счетчик 8 практически не изменяют содержимого последнего, так как после поступления 20 импульса на суммирующий вход реверсивного счетчика 8 с большой вероятностью поступает импульс на его вычитающий вход. Таким образом, импульсы на выходе первого дешифра- 25 тора 10 не формируются, а следовательно, через интервалы, времени, определяемые коэффициентом деления вычитающего счетчика 9, появ яются импульсы на выходе второго дешифратора 30

11, осуществляющие установку в нуль

RS-триггера 15.

Первый 12 и второй 13 дополнительный блоки задержки предназначены для предОтвращення ðìíðoÂÂHHH лОжных 35 выходных сигналов на выходе первого дешнфратора 10 при переключении реверсивного счетчика 8 и увеличения длительности выходного импульса первого дешифратора 10. 4О

Формула изобретения

1. Устройство определения перерывов цифрового сигнала в радиоканале, содержащее последовательно соединенные выделитель фронтов, блок задерж45 ки и первый элемент И, последовательно соединенные блок фазирования, формирователь импульсов, соответствующих началу и концу посылки, и второй элемент И, а также интегратор и формирователь импульсов, соответст вующих центру посылки, вход и выход которого подключены соответственно к второму выходу блока фаэирования и второму входу первого элемента И,второй вход второго элемента И подключен к выходу блока задержки, а вход блока фазирования подключен к выходу выделителя фронтов, причем вход выделителя фронтов является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные первый дополнительный блок задержки, первый дешифратор, второй дополнительный блок задержки, элемент ИЛИ, вычитающий счетчик, второй дешифратор и R+S-триггер, при этом выходы первого и второго элементов И, элемента ИЛИ и блока задержки подсоединены соответственно к первому, второму и третьему управляющим входам интегратора и входу первого дополнительного блока задержки, дополнительный вход формировате.ля импульсов, соответствующих центру посылки, и тактовый вход вычитающего счетчика подключены к первому выходу блока фазирования, второй выход которого подсоединен к допол" ннтельному входу формирователя им.т пульсов, соответствующих началу и концу посылки, и стробирующему входу второго дешифратора, выход интегратора подсоединен к информационному входу первого дешифратора, выход которого подсоединен к S-входу RSтриггера, причем установочные входы интегратора и вычитающего счетчика, второй вход элемента ИЛИ и прямой выход RS-триггера являются соответственно первым, вторым и третьим устанавливающими входами и выходом устройства.

2. Устройство по n.l, о т л и— ч а ю щ е е.с я тем, что формиро-,. ватель импульсов, соответствующих центру посылки, и формирователь импульсов, соответствующих началу и концу посылки-, выполнены в виде RSтриггеров, причем S- u R-входы и прямой выход RS-триггеров являются соответственно входом, дополнительным входом и выходом формирователя импульсов, соответствующих центру посылки, и формирователя импульсов, соответствующих началу и концу посылки, а интегратор выполнен в виде реверсивного счетчика, устанавливающий вход, вход сложения, вход вычитания, вход разрешения записи и выходы разрядов которого являются со ответственно устанавливающим входом, первым, вторым и третьим управляющими входами и выходом интегратора.

1538262

17 иЛ ЛГ L

/б!

Составитель В.Орлов

Редактор В.Данко Техред Л.Олийнык Корректор С.Черни

Тираж 523

Заказ 174

Подписное

ВНИИПИ Государственного комитета по изобретениям и открьгиям при ГКНТ ССС1

113035, 11асква, Ж-35, Раучаская наб., д. 4/5

Производственно-издательский комбинат "TIaTeHT г. Ужгород, ул. Гагарина, 101