Регистр сдвига

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в регистрах сдвига на основе приборов с переносом. Целью изобретения является повышение быстродействия регистра сдвига. Поставленная цель достигается за счет введения усилительного транзистора 14 и форсирующего конденсатора 15, а в блок регенерации четвертого разрядного 13 и четвертого зарядного транзисторов 12. 2 ил.

СОЮЗ COBETCHHX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) (51)5 G 11 С 1 28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

:(21) 4404081/24-24 (22) 04 ° 04.88 (46) 30.01.90. bine. и 4 (72) П.А. Копыл, В.П. Рева, А.11. Торчинский и Л.л. Утяков (53) 681.327.6(088.8) (56) Патент США М 3582909, кл. G 11 С 11/40, 1979 °

Авторское свидетельство СССР и 1298806, кл. G ll С 19/28, 1985.

2 (54) РЕГИСТР СДВИГА (57) Изобретение относится к вычислительной технике и может быть использовано в регистрах сдвига на основе приборов с переносом. Целью изобретения является повышение быстродействия регистра сдвига ° Поставленная цель достигается за счет введения усилительного транзистора 14 и форсирующего конденсатора 15, а в блок регенерации - четвертого разрядного 13 и четвертого зарядного транзисторов 12.

2 ил.

1539842

u = q/(ñ,+ с„,„), где Q — величина информационного заря50 да °

C»„- емкость узла, г;

С,, - емкость конденсатора 4.

Во время действия второго тактового импульса напряжения происходит также заряд узлов Д, е до напряжения

0®> От °

Изобретение относится к вычислительной технике и может быть использовано в регистрах сдвига на основе приборов с переносом заряда.

Целью изобретения является повышение быстродействия регистра сдвига.

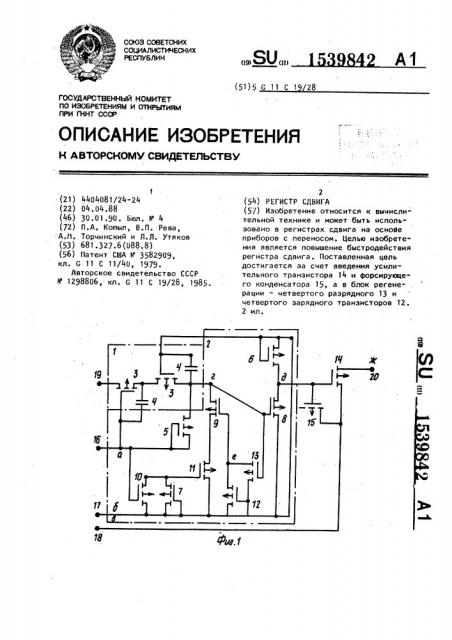

На фиг. 1 приведена принципиальная схема регистра сдвига; на фиг ° 2 временные диаграммы его работы.

Регистр сдвига содержит элементы

1 памяти (показаны два элемента памя,,ти) и блок 2 регенерации. Элемент памяти состоит из передающего транзис-!, тора 3 и накопительного конденсатора

4. Блок регенерации содержит первый, 5, второй 6 и третий 7 зарядные тран зисторы, первый 8, второй 9 и третий

I 10 разрядные транзисторы, коммутирующий транзистор 11, а также четвертый зарядный l2 и четвертый разрядный 13 ,транзисторы. Устройство содержит так же усилительный транзистор 14 с фор сирующим ИДП конденсатором 15, первый

; 16, второй 17 и третий 18 тактовые 2, входы, информационные вход 19 и вы-!, ход 20.

Регистр сдвига работает следующим ,образом.

Под воздействием тактовых импульсов, подаваемых на первый 16 и второй

17 тактовые входы, информация, представленная зарядами в накопительных конденсаторах 4, передается во время действия второго тактового импульса напряжения в накопительный конденсатор 4 последнего элемента 1 памяти.

При отсутствии информационного за ряда потенциал в узле г определяется величиной предварительного заряда этого узла транзистором 5 во время дейст40 вия первого тактового импульса напряжения и вс>льтдобавкой, возникающей за счет емкостной связи этого узла с вторым тактовым входом 1/. При наличии 4 информацис>нного заряда потенциал этого узла понижается на величину где Ц„ - амплитуда второго тактового импульса напряжения;

- пороговое напряжение используемых ИДП-транзисторов.

Детектирование состояния заряда конденсатора 4 последнего элемента 1 памяти происходит во время спада второго тактового импульса напряжения. В первом случае (при отсутствии заряда) транзисторы 8 и 13 открыты напряжением вольтдобавки, и узлы Д и е разряжаются одновременно со спадом второго тактового импульса напряжения. При этом в начальной стадии процесса заперт транзистор 11, а в конечной стадии процесса снижается потенциал узла е, запирая транзистор 9 и предотвращая тем самым протекание тока в цепи транзисторов 11 и 9. Благодаря этому сохраняется потенциал узла г, а узел Д полностью разряжается.

Во втором случае, если -информационный заряд достаточен для того, чтобы компенсировать величину вольтдобавки настолько, что в начальной стадии процесса транзистор 13 заперт, то при уменьшении второго тактового импульса напряжения до значения

0Ф 211т открывается цепочка транзисторов 11 и

9, узел г разряжается, запирая транзисторы 8 и 13. При этом в узле Д потенциал сохраняется. Импульс третьего тактового напряжения, поступающий с третьего тактового входа 18, через конденсатор 15 форсирует потенциал узла Д и через транзистор 14 проходит на выход 20 устройства. Импульс первого тактового напряжения подготавливает схему к следующему циклу, заря1 жая через транзистор 5 узел г. При том транзистор 10 фиксирует нулевой потенциал на затворе транзистора 11, препятствуя протеканию сквозного тока по цепочке транзисторов 5,9 и 11.

Наличие значительной емкости, присоединенной к узлу Д, замедляет процесс разряда этого узла, однако емкость узла е минимальна и транзистор

9 на конечной стадии заперт.

В зависимости от конкретных условий функционирования регистра узловая емкость может быть уменьшена по сравнению с емкостью нагрузки на один-два порядка. При этом примерно на порядок может быть увеличено быстродействие регистра.

5 53

Формула и зоб рет ения

Регистр сдвига, содержащий элементы памяти, каждый из которых состоит иэ передающего транзистора и накопительного конденсатора, обкладки которого соединены соответственно с затвором и стоком передающего транзистора, исток передающего транзистора каждого элемента памяти, кроме первого, соединен со стоком передающего транзистора предыдущего элемента памяти, а исток передающего транзистора первоГо элемента памяти RBJIRBTGR информационным входом регистра, затворы передающих транзисторов нечетных и четных элементов памяти являются соответственно первым и вторым тактовыми входами регистра, блок регенерации, состоящий из трех зарядных транзисторов, трех разрядных транзисторов и коммутирующего транзистора, исток которого соединен с истоками, а затвор— со стоками третьего зарядного и третьего разрядного транзисторов, затворы которых соединены с затворами передающих транзисторов нечетных и четных элементов памяти соответственно, сток коммутирующего транзистора соединен с истоком второго разрядного транзистора, сток которого соединен с истоком первого зарядного транзистора, стоком передающего транзистора }842 6 последнего элемента памяти и затвором первого разрядного транзистора, исток которого соединен с истоком коммути.рующего и затвором третьего зарядного транзисторов, а сток — с истоком второго зарядного транзистора, сток и затвор которого соединены с истоком коммутирующего транзистора, сток и

10 затвор первого зарядного транзистора соединены с затвором третьего разрядного транзистора, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия регистра, он содержит уси-!

5 лительный транзистор и форсирующий конденсатор,,а в блоке регенерации четвертые разрядный и зарядный транзисторы, истоки которых соединены с истоком коммутирующего транзистора, 20 а стоки — с затвором второго разрядного транзистора, затвор четвертого зарядного транзистора соединен с истоком четвертого разрядного транзистора, затвор которого соединен с затво25 ром первого разрядного транзистора, сток которого соединен с затвором усилительного транзистора и первой обкладкой форсирующего конденсатора, вторая обкладка которого соединена с истоком усилительного транзистора и является третьим тактовым входом регистра, сток усилительного транзистора является выходом регистра.