Одноразрядное оперативное запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при создании запоминающих устройств с встроенной коррекцией ошибок в интегральном исполнении. Целью изобретения является повышение надежности устройства. Устройство содержит основной и дополнительный накопители, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, с первого по седьмой, и элементы И, с первого по третий. Цель изобретения достигается тем, что в каждом цикле обращения к устройству, помимо выбираемых информационных и контрольных разрядов строки и столбца итерационного кода, считываются и проверяются по четности все оставшиеся контрольные разряды, что позволяет обнаруживать ошибки в контрольных разрядах, исправлять их и восстанавливать истинное значение в дополнительном накопителе в такте записи цикла обращения. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕаЪБЛИН (19) (И) (51)5 С 11 С 2 /00

3 !

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTGPCH0MY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

f (21) 429871У24-24 (22) 06.07.87 (46) 30.01.90. Бюл. и 4 (72) С.А. Фастов, С.В. Сушко и А.И. Березенко (53) 681.327.6(088.8) (56) Патент США М 4561095, кл. 371-38, опублик. 1985.

Патент СНА Р 4456980, кл. 365-200, опублик. 1984. (54) ОДНОРАЗРЯДНОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК (57) Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при создании запоминающих устройств с встроенной коррекцией ошибок в интегральном исИзобретение относится к вычислительной технике и микроэлектронике и может быть использовано при создании запоминающих устройств с встроенной коррекцией ошибок в интегральном исполнении.

Целью изобретения является повышение надежности устройства.

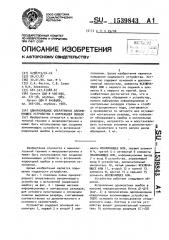

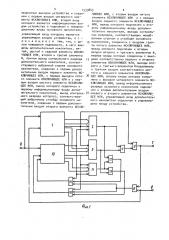

На фиг. 1 показана схема одноразрядного оперативного запоминающего устройства с встроенной коррекцией ошибок; на фиг. 2 - пример массива информационных и контрольных разрядов, для которого пунктирными и сплошными линиями выделены разряды, считываемые соответственно из дополнительного и основного накопителей.

Устройство содержит основной накопитель 1, первый 2 и второй 3 эле- .

2 полнении ° Целью изобретения является повышение надежности устройства. Уст" ройство содержит основной и дополнительный накопители, элементы ИСКЛОЧАЮЩЕЕ ИЛИ с первого по седьмой и элементы И с первого по третий. Цель изобретения достигается тем, что в каждом цикле обращения к устройству, помимо выбираемых информационных и контрольных разрядов строки и столбца итерационного кода, считываются и проверяются по четности все оставшиеся контрольные разряды, что позволяет обнаруживать ошибки в контрольных разрядах, исправлять их и восстанавливать истинное значение в дополнительном накопителе в такте записи цикла обращения. 2 ил. менты ИСКЛЮЧАЮЩЕЕ ИЛИ, первый элемент

И 4, третий 5 и-четвертый 6 элементы

ИСКЛЮЧАЮЩЕЕ ИЛИ ° информационные выход

7 и вход 8 устройства, управляющий вход 9 устройства, дополнительный накопитель 10, пятый элемент ИСКНОЧАЮЦЕЕ ИЛИ 11, второй 12 и третий 13 элементы И, шестой 14 и седьмой 15 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ;

Устройство работает следующим образом.

Исправление однократных ошибок в массиве информационных битов Д1-Д16 (Фиг. 2) в предлагаемом одноразрядном оперативном запоминающем устройстве (ОЗУ) основано на использовании итера-. ционного кода. Поэтому в состав устройства входят дополнительный накопитель 10 контрольных разрядов (С1-С8) 4 допускают устранение ошибок только в

ЭП основного накопителя 1. Если же, ошибка возникает в каком-либо конт--. рольном разряде, то одновременное нарушение четности для строки и столбца не наблюдается и, следовательно, такая ошибка сохраняется либо до момента выключения питания ОЗУ и следующей после повторного включения питания начальной установки его ЭП, либо до момента возникновения ошибки в любом другом ЭП массива Д1-Д16 и С1-С8, что приводит к сбою в работе устройства.

В отличие от известного устройства, в предлагаемом ОЗУ в каждом цикле записи и считывания, помимо перечисленных выше информационных и контрольных разрядов, считываются также все оставшиеся контрольные разряды (С1, С3-С5,С7,С8). Это позволяет при любом обращении к ОЗУ осуществлять проверку на сохранение четности для всех контрольных разрядов с помощью элемента ИСКЛОЧАЮЩЕЕ ИЛИ 11. Если, например, имеет место ошибка в разряде С2, то она обнаруживается элементом И 12, исправляется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и переэаписывается в дополнительный накопитель 10. В ис-". правлении ошибки в разряде.С6 участвуют элемент И 13 и элемент ИСКЛЮЧАЮЦЕЕ. ИЛИ 1 .

Таким образом, преимущество предлагаемого устройства состоит в повышении надежности работы ОЗУ эа счет обнаружения ошибок в контрольных разрядах полных слов данных, их исправления и перезаписи исправленных данных в дополнительный накопитель. формула изобретения

Одноразрядное оперативное запоминающее устройство с коррекцией ошибок, содержащее основной накопитель, выходы выбираемых при обращении в соответствии с матрицей кодирования разрядов строки и столбцы- которого соединены с входами группы соответственно первого и второго элементов ИСКНЮЧЙОЩЕЕ ИЛИ, выходы которых подключены к входам первого элемента И, выход которого соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к вы-. ходу информационного разряда основного накопителя, а выход является инфор3 1539843 и единый блок кодирования / декодирования, построенный на логических элементах 2-6 и 11-15. В целях упрощения описания, устройства из его состава исключены адресные цепи выборки элементов памяти (ЭП) основного 1 и дополнительного 1О накопителей.

Так как предлагаемое устройство, с коррекцией ошибок имеет однораэряд- 10 ную организацию, то любое обращение к нему начинается со считывания данных из основного 1 и дополнительного 10

| накопителей. Если внешнее обращение к ОЗУ производится в режиме записи,, считанные данные модифицируются и пе, ; резаписываются в накопители 1 и 10. В

, режиме внешнего считывания по считан1 ным данныи восстанавливается истинное значение выбираемого бита (поступаю.,цего на первый выход основного нако), пителя 1)., которое передается на ин формационный выход 7 устройства.

В устройстве, принятом за прототип,, за один цикл обращения к ЭП разряда

Д6 считываются информационные разряды Д2, ДЦ„ Дб, Д7, Д8, Д10, Д14 и ,контрольные разряды С2 и С6, причем содержимое контрольных разрядов С2 и

С6 отражает соответственно результаты суммирования по модулю 2 содержимых битов строки и столбца, на пересечении которых находится искомый разряд Д6„ Следует отметить, что разделение указанного на фиг. 2 массива разрядов на строки и столбцы является З5 условным, поскольку в реальной матри" це все ЭП разрядов вытянуты в одну строку и выбираются за один цикл обрац ения к ОЗУ.

В известном устройстве по выбранным разрядам"производится проверка сохранения четности для строки (элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2) и столбца (элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3), и при на-„ рушении четности и для строки, и для столбца одновременно элемент И 4 фор" мирует сигнал уровня "1", указывающий элементу ИСКЛЮЧАЮЩЕЕ ИЛИ 5 на необходимость инвертирования содержимого разряда Д6. В режиме внешней записи исправленное содержимое разряда Д6 сравнивается с битом данных, поступив шим íà информационный вход 8 устройства, и в случае несовпадения формируется сигнал на одновременное инвертирование содержимого контрольных разрядов С2 и Сб. Таким образом,. рассмотренные средства коррекции ошибок

5 мационным выходом устройства и соединен с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является информационным входом устройства и подключен к информа. ционному входу основного накопителя, управляющий вход которого является управляющим входом устройства, о т— л и ч а ю щ е е с я тем, что, с целью повышения надежности, в него введены дополнительный накопитель, пятый, шестой и седьмой элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, второй и третий элементы

И, причем выход контрольного разряда дополнительного накопителя, соответствующего выбранной строке основного накопителя, соединен с первым дополнительным входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым выходом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым:;входом шестого элемента ИСКЛЮЧАЮЦЕЕ ИЛИ, выход которого подключен к первому информационному входу дополнительного накопителя, выход контрольного разряда которого, соответствующий выбранному столбцу основного накопителя, соединен с первым дополнительным входом второго элемента ИСКЛЮ398 3

ЧАЮЩЕЕ ИЛИ, с вторым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом седьмого элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, выход которого подключен к второму информационному входу дополнительного накопителя, выходы контрольных разрядов, соответствующих невыбранным строкам и столбцам основного накопителя, соединены с входами группы пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к вторым входам второго и третьего элементов И, первые входы которых соединены с выхо15 дами соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы второго и третьего элементов Иподключены к третьим входам соответственно шестого и седьмого элементов ИСКЛЮЧАЮ о ЦЕЕ ИЛИ, вторые входы которых соединены с выходом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход информационного разряда основного накопителя подключен к вторым дополнительным входам

25 первого и второго элементов ИСКЛЮЧАЮЦЕЕ И11И, управляющий вход дополнительного накопителя подключен к управляющему входу устройства.

1539843

Составитель О. Исаев

Редактор И. Рыбченко Техред А.Кравчук, Корректор И. 1 1арояи .Заказ 223 Тираж 473 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, N-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина,101