Запоминающее устройство с исправлением ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при проектировании запоминающих устройств, к которым предъявляется требование исправления ошибок в процессе работы. Цель изобретения состоит в повышении надежности работы устройства за счет исправления двух ошибок. Устройство содержит блок 1 памяти, блок 2 сравнения, первый 3 и второй 4 блоки приоритета, первый 5 и второй 6 блоки формирования и хранения признаков инвертирования и корректор 7. 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (111 (51}5 С 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

Il0 H30SPETEHHRM И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

t (21) 4382402/24-24 (22) 22.01.88 (46} 30.01.90. Бюл. и 4 (72) К.Р. Бурик, А.И. Кись и О.И.пля" сов (53) 681.327(088.8) (56) Авторское свидетельство СССР

М 970476, кл. G 11 С 29/00, 1980.

Авторское свидетельство CCCP

Н 1285985, кл. G 11 С 29/00, 1984. (54) ЗАИОЙИНА10ЩЕЕ УСТРОЙСТВО С ИС0РАВЛЕНИЕИ ОЩИВОК (57) Изобретение относится к вычис2 лительной технике и может быть исполь. зовано при проектировании запоминаюцих устройств, к которым предьявляется требование исправления ошибок в процессе работы. Цель изобретения состоит в повышении надежности устройства в работе за счет исправления двух ошибок. Устройство содержит блок

1 памяти, блок 2 сравнения, первый 3 и второй 4 блоки приоритета, первый

5 и второй 6 блоки формирования и хранения признаков инвертирования и корректор j. 5 ил.

3 1539845 4

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано при разработке вычислительных машин, к которым предьявляется требование сохранения работоспособности при наличии одной или двух ошибок в ячейках памяти.

Цель изобретения - повышение на:,дежности устройства. !

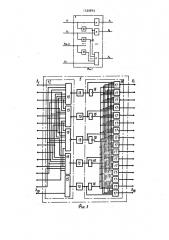

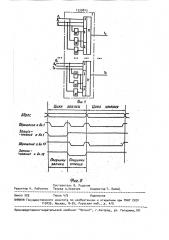

На Фиг. 1 изображена функциональ ная схема устройства; на фиг. Z-,структурная схема варианта выполнения блока приоритета; на Фиг. 3 - структур-15 ная схема блока Формирования и хранения признаков инвертирования для 16разрядного ЗУ; на фиг. 4 - структурная схема корректора; на фиг. 5 - временные диаграммы работы устройства.

Устройство содержит блок 1 памяти, блок 2 сравнения, первый 3 и второй

4 блоки приоритета, первый 5 и второй

6 блоки Формирования и хранения признаков инвертирования и корректор 7 ° 2д

Кроме того, устройство содержит и информационных входов 8 и выходов 9, где Il — количество разрядов устройства. Формирователи необходимых для работы устройства адресных и управляю- 30 щих сигналов (записи — считывания, обращения) и их цепи на фиг, 1 условно не показаны.

Блоки 3 и 4 приоритета (фиг. 2) могут быть выполнены из и-1 элементов НЕ 10, и и элементов ИДИ 11 Бло- З5 ки и 6 контроля (фиг. 3) содержат

t шифратор 12, контрольные блоки 13 памяти и дешифратор 14. Шифратор 12 содержит элементы И-НЕ 15. Дешифратор 14 содержит элементы НЕ 16 и И-НЕ 17.

Корректор 7 содержит в каждом разряде три элемента НЕ 18-20 и один элемент

И-ИЛИ 21,.

Устройство работает следующим об- 4> разом.

Цикл записи разбивается на 2 полуцикла: полуцикл записи и полуцикл считывания. В первом полуцикле произво" дится запись информации, поступающей по входаи 8 в блок 1 памяти, а во

S0 втором полуцикле " считывание записанного в первом полуцикле числа. Считанная информация сравнивается в блоке

2 с записанной, которая в полуцикле считывания еще удерживается на входах 5

Ь, и результаты поразрядного сравнения с блока 2 поступают на входы блоков 3 и 4 приоритета. Один из этих блоков, например блок 3, определяет только один младший из двух отказавших разрядов, а блок 4 выделяет старший из двух отказавших разрядов. Если отказы блока 1 отсутствуют, блоки

3 и 4 не формируют на своих выходах признака отказавшего разряда, а при наличии отказа только в одном разряде блока 1 блок 3 или 4 вырабатывает признак этого разряда.

Сигнал признака отказавшего разряда с выходов блоков 3 и 4 подается на входы блоков 5 и 6, где преобразуется в шифраторе 12 на элементах И-НЕ 15, и код признака ошибки записывается в дополнительные блоки 13 памяти по данному адресу.

В цикле считывания информация до" полнительных блоков 13 памяти (см. фиг. 5) дешифрируется в дешифраторе

14, и на выходах блоков g и 6 появляются сигналы с кодом, например, "0" в отказавшем разряде и.с "1" в остальных разрядах.

Сигналы с выходов дешифраторов 14 блоков 5 и 6 выдаются поразрядно в корректор 7, где производится передача на выходы 9 устройства прямых кодов информации с блока 1 или обратного кода одного или двух разрядов, в которых произошла ошибка.

Формула изобретения, Запоминающее устройство с исправ- лением ошибок, содержащее блок памяти, блоки формирования и хранения признаков инвертирования и корректор, выходы которого являются информационными выходами устройства, причем входы первой группы корректора соединены с, выходами блока памяти, информацион ные и адресные входы, входы обращения и входы записи-считывания являются одноименными входами устройства, о т .- „ л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены блоки приоритета и блок сравнения, входы первой и второй групп которого соединены соответственно с информационными входами устройства и выходами блока памяти, выходы блока сравнения поразрядно подключены к соответствующим входам блоков приорите- .. та, выходы которых соединены с входами соответствующих блоков формирования и хранения признаков инвертирования, выходы которых подключены соответственно к входам второй и третьей групп корректора.

1539845

ЩРащдиае к Й.

Крайние д й.

Залисз-Чааяй ю йfg

Составитель 8. Рудаков

Редактор И. Рыбченко Техред А.Кравчук Корректор Т. Палий

Заказ 223 Тираж 473 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101