Устройство для управления производственными процессами

Иллюстрации

Показать всеРеферат

Изобретение относится к области управления производственными процессами и может быть использовано в дискретных системах управления, например, в угольной и горнорудной отраслях промышленности (управление водоотливными и холодильными установками, шахтным рельсовым транспортом и др.). Целью изобретения является уменьшение потребляемой мощности и повышение надежности устройства в работе. Указанная цель достигается тем, что в устройство для управления производственными процессами, содержащее первую и вторую программируемые логические матрицы 1 и 3, блок 2 памяти технологических команд, блок питания, дополнительно введены таймер 4, D-триггер 5 и формирователь 6 стробов, что позволяет временно задействовать ПЛМ в работу, сберегая при этом их ресурс и снижая потребляемую мощность устройства. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) 5 5 А1 (51)5 Г 05 В 19/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4412258/24-24 (22) 23.02.88 (46) 07.02.90. Бюл. М- 5 (?1) Конотопский электромеханический завод Красный металлист 1 (72) Н.П. Матвиенко и А.Д. Захарюгин (53) 621.503.55(088.8) (56) Баранов С.И. и Баркалов А.А.

Применение программируемых логических матриц в цифровой технике °

Зарубежная радиоэлектроника, 1982, Р 6, с. 74-75. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОИЗВОДСТВЕННЫМИ ПРОЦЕССАМИ (57) Изобретение относится к области управления производственными процессами и может быть использовано в дискретных системах управления, напри2 мер, в угольной и горнорудной отраслях IlpoMblHUIpHHocTH (управление водоотливными и холодильными установками, шахтным рельсовым транспортом и др.). Пелью изобретения является уменьшение потребляемой мощности и повышение надежности устройства в работе. Указанная цель достигается тем, что в устройство для управления производственными процессами, содержащее первую и вторую программируемые логические матрицы 1 и 3, блок 2 памяти технологических команд, блок питания, дополнительно введены таймер 4, D-триггер 5 и формирователь 6 стробов, что позволяет временно задействовать IIJIM в работу, сберегая при этом их ресурс и снижая потребляемую мощность устройства.

3 ил. С:

1541558!

Изобретение относится к области управления производственными процессами и может быть использовано в дискретных системах управления, например, в угольной и горнорудной промышленности (увравление водоотливными и холодиль..ыми установками, шахтным рельсовым транспортом и др.)..

Цель изобретения — уменьшение 10 потребляемой мощности и повышение надежности работы устройства.

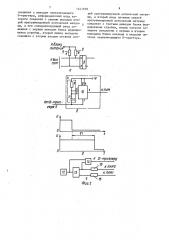

На фиг. 1 представлена схема устройства для управления производственными процессами; на фиг. 2 — примеры 15 реализации функциональных схем; на фиг. 3 — динамические характеристики работы устройства.

На фиг. 2 а — функциональная схема 20 ячейки блока памяти технологических команд; б †таймер, в — временная arpaMMa работы ячейки блока таймера; r — функциональная схема блока формирования стробов. 25

Устройство содержит блок 1 формирования адреса, выполненный на программируемой логической матрице, выходы которой соединены с входами блока 2 памяти технологических команд.

Выходы блока 2 памяти подключены к первой группе входов программируемых .ло ических матриц 1 и 3. Вторые входы программируемых логических матриц и 3 соединены с выходами технолог

35 гических датчиков А ... А . Третьи

° ° входы программируемой логической матрицы 1 подклю ены к технологическим датчикам. А а отдельный вход через

rn таймер 4 соединен с выходом переключающего D-триггера 5, информационный вход которого подключен к одному выходу программируемой логической матрицы. Синхронизирующий вход D-триггера 5 соединен с первым выходом блока 45

6 формирования стробов. Второй выход блока 6 формирования стробов подключен к первому входу питания программируемой логической матрицы 3. Второи вход iinaHHa программируемои ло гической матрицы 1 соединен с третьим выходом блока 6 формирования стро ов. б

Первый вход питания программируемых лог.ических матриц 1 и 3 подключен к первому выходу блока 7 питания. Перния вый и второй выходы блока 7 питания

2 соединены с входами питания блока памяти, D-триггера 5, блока 6 формирования стробов.

Блок 2 памяти технологических команд состоит из RS-триггеров 8 и резисторов 9. Функциональная схема ячейки блока 2 памяти приведена на фиг. 2а.

Резисторы 9 предназначены для поддержания потенциала на входах

RS-триггера 8 во время отсутствия питания на программируемой логической матрице 1, что способствует более надежной работе блока 2 памяти.

Блок таймера 4 предназначен для .формирования выдержек времени, необходимых при использовании устройства согласно алгоритму управления технологическим процессом. Пример ячейки принципиальной схемы таймера 4 приведен на фиг. 2б, а временная диаграмма ее работы — на фиг, 2в. Ячейка таймера 4 состоит из микросхемы

10 КР1006ВИ1 и задающей RC-цепочки 11.

Блок 6 формирования стробов предназначен для формирования стробов питания программируемых логических матриц 1 и 3 и строба синхронизации

D-триггера

Блок 6 стробов (фиг. 2г) состоит из задающего генератора 12, выход которого соединен с входом распределителя 13 сигналов и с первым входом элемента И 14. Первый выход распределителя 1.3 сигналов через первый формирователь 15 подключен к шинам питания программируемой логической матрицы 1, а второй выход распределителя

13 соединен с вторым входом элемента

И 14 и через второй формирователь 15 подключен к шинам питания программируемой логической матрицы 3. Выход элемента И 14 соединен с синхронизирующим входом D-триггера 5.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти блока 2 технологических команд находятся в "0" состоянии.

При поступлении на входы А, ... A„ программируемой логической матрицы

1 сигналов от датчиков и наличии строба на ее шинах питания производится включение ячеек памяти блока 2 в соответствии с программой, заложенной в логическую матрицу 1. Включение (выключение) элементов памяти блока 2 производится по алгоритму работы устройства, который задается программой логической матрицы 1. При

45

15415 исчезновении строба на шине питания программируемой логической матрицы 1 ячейки памяти блока 2 остаются в состояниях, в которые они должны войти

5 согласно программе работы матрицы 1.

В это время на выходах программируемой логической матрицы 3 присутствуют сигналы, равные "0", так как стробовый сигнал на шине питания 10 программируемой логической матрицы 3 отсутствует.

При поступлении сигнала стробового питания с выхода блока 6 на шины питания программируемой матрицы 3 производится выдача 7.„ сигналов на исполнительные механизмы, а также включение (отключение) D-триггера 5.

Выдача сигналов 2 включение (отключение) D-триггера 5 производится 20 по совокупности переменных А, ... А„, Р, ... Р;, которые программируются в матрице 3 согласно алгоритму работы данного устройства.

Включение D-триггера 5 производит- 25 ся следующим образом. При наличии сигнала "1" с выхода программируемой логической матрицы 3 и наличии синхроимпульса с первого выхода блока 6 формирования стробов, по его перед- 30 нему фронту производится включение

D-триггера 5.

Отключение П-триггера 5 производится при наличии сигнала "0" на выходе матрицы 3, соединенной с его информационным входом, и наличии синхроумпульса с блока 6 формирования стробов.

Включение D-триггера 5 приводит к включению ячейки блока таймера 4, 40 который через время ; выдает сигнал на вход программируемой логической матрицы 1. Данный сигнал . в совокупФ 1,ности с переменными А ... А и

tV

P ... Р; обрабатывается матрицей 1 согласно алгоритму работы устройства.

Сигналы на включение (выключение) ячеек памяти блока 2 поступают в него в следующий момент времени только при наличии стробового питания, которое подается с третьего выхода блока

6 формирования стробов на матрицу 1.

В дальнейшем работа устройства производится аналогично описанному вьппе.

Блок 2 памяти технологических ко5 манд работает следующим образом. При поступлении сигнала на вход S RS-триггер 8 включается, а при поступлении его на вход R выключается. Если в

58 качестве управляющих сигналов для

RS-триггеров 8 используются сигналы

"0", то резисторы 9 блока памяти подключают к положительному полюсу источника 7 питания и наоборот.

Ячейка таймера 4 работает следующим образом. При поступлении сигнала

"0" с D-триггера 5 на вход ячейки на ее выходе формируется сигнал "0" с задержкой, например,,, равной постоянной времени RC-цепочки 11.

Блок 6 формирования стробов работает следующим образом. Импульсы с задающего генератора 12 поступают на распределитель 13 сигналов и на первый вход элемента И 14. Распределитель 13 формирует на своих выходах сдвинутые во времени стробовые сигнала, которые в виде стробового питания, сформированного на формирователях 15 поступают на программируемые логические матрицы 1 и 3. Элемент И 14 позволяет сформировать синхроимпульс на

D-триггер 5.

Формула изобретения

Устройство для управления производственными процессами, содержащие блок памяти технологических команд, адресные входы которого соединены с выходами первого блока формирования адреса, каждый иэ которых выполнен на программируемой логической матрице, а его выходы подключены к первой группе входов первой и второй программируемых матриц, вторые группы входов которых соединены между собой и соединены с выходами технологических датчиков первой группы, а выходы технологических датчиков второй группы соединены с третьей группой входов первой программируемой логической матрицы, первый вход. nut тания которой соединен с первым входом питания второй программируемой логической матрицы и соединен с первым выходом блока питания, первый и второй выходы которого соединены с входами питания. блока памяти, о т" л и ч а ю щ е е с я тем, что, с целью уменьшения потребляемой мощности и повышения надежности работы устройства, в него введены блок формирования стробов, переключающий D-триггер и таймер, выход которого соединен с входом первой программируемой логической матрицы, а вход таймера

f54l558

Рдлокд

ПОЛ70Н0

Кои

ПЛ .

0m3HP соединен с выходом переключающего

D-триггера, информационный вход которого соединей с первым выходом второй программируемой логической матрн5 цы, а его синхрониэирующий вход соединен с первым выходом блока формирования,стробов, второй выход которого соединен с вторым входом питания второй программируемой логической матрицы, а второй вход питания первой программируемой логической матрицы соединен с третьим выходом блока формирования стробов, входы питания которого соединены с первым и вторым выходами блока питания и входами ttnтания переключающего D-триггера.

1541558 r йи.

8емрапю

Оа 11

hummus

ПЛИ1

0пцеанл

/ИмЯ

0&1 .УЛ. H

Ю с-&ада л-mp-ра

ОюФада

3-лО ра

Составитель Е. Титов

Техред N.Дидык

Корректор Л. Патай

Редактор Е. Папп

Заказ 279 Тираж 670 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва,.Ж-35, Раушская наб °, д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101