Устройство для вычисления функции @

Иллюстрации

Показать всеРеферат

Устройство для вычисления функции Z=√X<SP POS="POST">2</SP>+Y<SP POS="POST">2</SP> относится к области вычислительной техники и может быть использовано в специализированных устройствах для обработки сейсмических, акустических, видео и других сигналов, цель изобретения - повышение производительности при одновременном упрощении устройства, что достигается введением в устройство, содержащее схемы сравнения 5 и 6, коммутаторы 8, 9, 10, сумматор-вычитатель 7, регистров 1 - 4 и блока управления 11 с соответствующими связями. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (19> Е11) (51) 5 С 06 Г 7/552

Н AB ГОРСКОМУ СВИДЕТЕЛЬСТВУ

7718 ff Ш

gl,ЦОЕМ,Л

VZ.

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4385831/24-24 (22) 29.02.88 (46) 07.02.90. Вюл. Р 5 (71) Киевский политехнический институт им. 50-летия Великой Октябрьской социалистической революции (72) YJ.Ñ.Êàíåâñêèé, N.Ê.Êëèìåíêî, Л.И.,Цогинова и А.М.Сергиенко (53) 681.326(088.8) (56) Авторское свидетельство СССР

Р 1159014, кл. G 06 1 7/544, 1983, Авторское свидетельство СССР

Р 1208551, кл. Г 06 Г 7/544, 1984.

2, (54) УСТРОЙСТВО IIII I ВИЧИСЛЕИИЯ ФУНКИИИ Z=.J ã еуг (57) Устройство для вычисления функПии я=,Гх +y относится к вычислительной технике и может быть использо-, вано в специализированных устройствах для обработки сейсмических, акустических, видео- и других сигналов.

Цель изобретения — повынение производительности при одновременном упрощении устройства. Это достигается введением в устройство, содержащее схемы 5 и 6 сравнения, коммутаторы 8

10, сумматор-вычитатель 7, регистров 1 — 4 и блока 11 управления с соответствующими связями. 3 ил.

1541601

Изобретение относится к вычислительной технике и может быть использовано в специализированных устройствах для обработки сейсмических, акустических, видео- и других акустических сигналов.

Цель изобретения — повышение производительности при одновременном упрощении устройства. 10

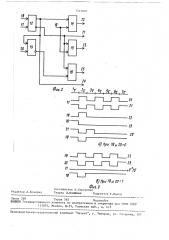

На фиг. 1 представлена структурная схема устройства; на фиг. 2 — схема блока управления, на фиг, 3 — диаграмма работы блока.

Устройство содержит регистры 1-4, схемы 5 и 6 сравнения, сумматор-выч гтатель 7, коммутаторы 8-10, блок 11 управления, содержащий триггеры 12 и 13, элементы И 14-16, входы 17-20 и выходы 21-25.

Работа устройства начинается при подаче сигнала на вход 17 начальной установки и синхроимпульса устройства на вход 18 (прием информации будет происходить по заднему фронту синхро- 25 серии,,по нулевому сигналу разрешения.

Вычисление функннн z= x +ó производится по формулам юа» () ю;„ггр А н о А,» 3 (1 — 2 )А„„„+2 А„„„при 2A jn

>А где А » =max(x,ó); А,„;„=шз-п(х »У) р 35 х > 0; у >, 0; z — выходной отсчет

Входные данные х; и у; поступают г оочередно соответственно в нечетные четные такты на вход регистра 1, абота начинается при подаче сигнала 40 ачальной установки 17.

В нулевом такте с информационного входа устройства в первый регистр 1 принимается первый отсчет х . В первом такте на входы первой схемы 5

=равнения с входа устройства и выхода регистра i поступают xð и у происходит сравнение; и при условии, что ;>х, на выходе 19 схемы 5 сравнеGyneT HyHeBoA cHrHaH Hepe3 пер вый коммутатор 8 во второй регистр 2 записывается А,„;„ =хо, а в регистр

1 — А „. =y . На управляющих выходах

22 и 23 блока 11 управления, посту55 пающих на управляющие входы регистра

1 и коммутатора 8, .будут нулевые сигналы. При условии, что y,сх „на выходе схемы 5 сравнения будет единич" ный сигнал и в регистр 2 записывается y, а в регистре 1 останется х,.

На управляющих выходах 22 и 23 блока t1 управления, поступающих на управляющий вход регистра 1 будет нулевой сигнал, а на управляющий вход коммутатора 8 — единичный.

Во втором такте на входы второй схемы 6 сравнения с выходов регистров 1 и 2 поступают А „ и А

O О происходит сравнение и A ;„ поступает сдвинутым на один разряд влево, и при условии, что 2А»„„,1 А „,, на выходе 20 схемы 6 сравнения будет нулевой сигнал, а при условии 2А „;д .

«(А

«»к, единичный. А ;„переписыО вается с регистра 2 в регистр 3, а в регистр 2 записывается A Ä . В этом а с », ряд вправо, а на второй вход сумматора-вычитателя 7 с выхода регистра 2 через вход второго коммутатора 9 поступает А „, сдвинутое на три разD ряда вправо. На сумматоре-вычитателе 7 происходит суммирование, результа которого (1-2 )А,„„„„записывается в регистр 4 ° А а» с регистра 2 переписывается в регистр 3. По нулевому сигналу схема 5 сравнения будет

I производить cpaBHeHHp y ) х„где yi

4 вновь поступившее данное на вход устройства, При условии, что на выходе

20 схемы 6 сравнения будет единичный сигнал, с выхода регистра 3 через вход коммутатора 10 сдвинутое на три разряда вправо Aj„,„, поступает на первый вход сумматора-вычитателя 7, на второй вход которого с выхода коммутатора 9, через его вход сдвинутое на четыре разряда вправо A«„4 поступает также с выхода регистра 3. На сумматоре-вычитателе 7 происходит

-з суммирование, результат которого (2 +

+2 )А,„;», записывается в регистр 4.

-4

В четвертом такте при условии, что на выходах 19 и 20 схем 5 и 6 такте х» поступает с входа устройства в регистр 1.

В третьем такте при условии, что на выходе 20 схемы 6 сравнения нулевое состояние, на первый вход сумматора-вычитателя 7 с выхода регистра 3 через вход третьего коммутатора 10 по" ступит А ;„, сдвинутое на один раз зП зз

1541601 сравнения будет нулевое состояние, с выхода регистра 4 на третий вход коммутатора 9 поступает результат суммирования и через выход коммутатора 9 поступает на второй вход сумматора5 вычитателя 7, на первый вход которого через вход коммутатора 10 поступает А „ с выхода регистра 3, Результат суммирования (1-2 )А„„„ +2 A 10

=z, поступает в регистр 4. При условии, что на выходах 19 и 20 схем срав нения 5 и 6 единичное состояние, с выхода регистра 4 результат суммирования через коммутатор 9 поступает на второй вход сумматора-вычитателя 7, на первый вход которого через коммутатор 10 поступает A „ . Результат суммирования А,„„ +(2 +? ). А ;„, =z 20 поступает в регистр 4, В этом такте в схеме б сравнения происходит сравнение 2А „;„, и А „„ . В регистр 3 записывается А,.„,, а в регистр 2 - A<><< 25

В регистр 1 записывается х с входа устройства.

В пятом такте на выход устройства поступает выходной отсчет z, Дальнейшая работа устройства происходит аналогично. Устройство работает в конвейерном режиме с периодом два такта и на выход устройства каждый второй такт поступает выходной отсчет z.; при условии непрерывной подачи исходных данных 35 х,. и у„. на его вход. формула изобретения

Устройство для вычисления функции

z= x +ó, оодервапее первый, второй и третий коммутаторы, первую и вторую .схемы сравнения и сумматор-вычитатель, первый и второй входы которого подключены к выходам соответственно второго 45 и третьего коммутаторов, о т л ич а ю щ е е с я тем, что, с целью повышения производительности при одновременном упрощении устройства, оно содержит с первого по четвертый регистры и блок управления, содержащий два триггера и три элемента И, причем информационный вход устройства соединен с первым входом первой схемы сравнения, первым информационным входом первого коммутатора и информационным входом первого регистра, .выход которого подключен к второму входу первой схемы сравнения, первому входу второй схемы сравнения и второму информационному входу IlppBoI 0 коммутатора, выход которого через второй регистр соединен со сдвигом на один разряд влево с вторьрм входом второй схемы сравнения, а со сдвигом на три разряда вправо — с первым информационным входом второго коммута тора и с входом третьего регистра, выход которого сс сдвигом на четыре. разряда вправо подключен к второму информационному входу второго коммутатора, а со сдвигом на ноль, один, два, и три разряда вправо — соответственно к информационным входам, с первого по четвертый, третьего коммутатора, выход сумматора-вычитателя соединен с входом четвертого регистра, выход которого является выходом устройства и подключен к третьему информационному входу второго коммутатора, первый и второй входы блока управления являются входом начальной уста- новки и синхровходом устройства и подключены к входу установки в "0" и счетному входу первого триггера, прямой выход которого соединен с первым входом первого элемента И и синхровходом второго триггера, а инверсный выход — с первыми входами второго и третьего элементов И и является первым выходом блока управления, второй и третий выходы которого соединены соответственно с выходами первого и второго элементов И и являются управляющими входами первого регистра и первого коммутатора соответственно, выход первой схемы сравнения соединен с вторыми входами первого и второго элементов И и является третьим входом блока управления, четвертый вход которого соединен с информационным входом второго триггера и является выходом второй схемы сравнения, прямой выход первого триггера и выход третьего элемента И являются четвертым и пятым выходами блока управления и соединенш с первым и вторым чправляющими входами второго коммутатора, инверсный выход второго триггера соединен с вторым входом третьего элемента И, первый и пятый выхопы блока управления соединены с первым и вторым управляющими входами третьего коммутатора, четвертый выход блока управления подключен к управляющему входу сумматора-вычитателя и третье го коммутатора соответственно. 541б01 а) /7ри !ди гр=а ф/1ри!9и10=!

Фиг, l

Составитель А.Сергиенко

Техред Л.Олийнык Корректор Т.Малец

Редактор А.Козориз

Заказ 281 Тираж 562 Подписное

ВЯИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская. наб., д. 4/5

Производственно-издательский комбинат Патент", r. Ужгород, ул. Гагарина, 101