Устройство для отладки микроэвм

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано для настройки, отладки и проверки работы специализированных микроЭВМ. Цель изобретения - уменьшение времени отладки. Устройство содержит блок 1 останова по адресу и блок 2 готовности, регистр 3, схему 4 сравнения, три элемента И 5, 6 и 10, два элемента ИЛИ 8 и 11, триггер 9, элемент НЕ 7. Изобретение позволяет ускорить локализацию ошибок в программном обеспечении микроЭВМ, что особенно важно при отладке многоуровневых программ большого объема. 1 ил.

СОО3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 06 F 11/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ CHHT СССР (21) 4402812/24-24 (22) 04 ° 04.88 (46) 07,02.90. Бюл. Р 5 (72) Я.И.Торошанко, В.А.Каустов, В.С.Погорелов, Б,И.Мовчан, И.Л.Тарнопольский и В.N,Ïîëèùóê (53) 681.3 (088.8) (56) Авторское свидетельство СССР

Р 962945, кл. G 06 F 11/28, 1978.

Авторское свидетельство СССР

Р 1432531, кл. G 06 F 11/28, 1986. (54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ МИКРОЭВМ (57) Изобретение может быть использо„„SU 1541615 А 1

2 вано для настройки, отладки и проверки работы специализированных микроЭВМ.

Цель изобретения — уменьшение времени отладки. Устройство содержит блок

1 останова по адресу и блок 2 готовности, регистр 3, схему 4 сравнения, трп элемента И 5, 6 и 10, два элемента ИЛИ 8 и 11, триггер 9, элемент HE

7. Изобретение позволяет ускорить локализацию ошибок в программном обеспечении микроЭВ11, что особенно важно при отладке многоуровневых программ большого объема. 1 ил, 1541615

Изобретение относится к вычислительной технике и может быть использовано для настройки, отладки и проверки работы специализированных микроЭВГ1.

Цель изобретения — сокращение времени отладки программ.

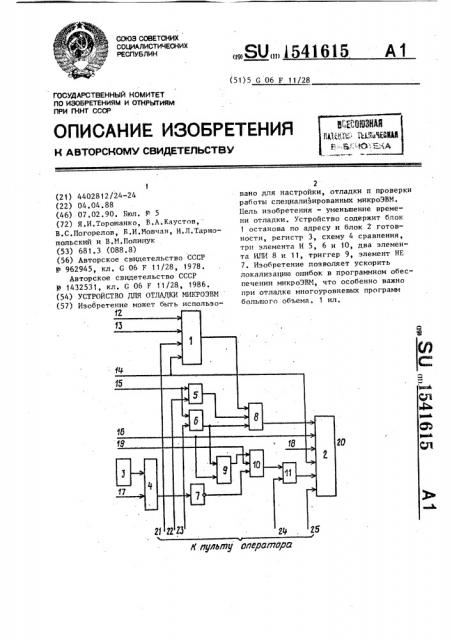

На чертеже представлена схема устройства для отладки микроЭВМ.

1О

Устройство для отладки микроЭВМ содержит блок 1 останова по адресу, блок 2 готовности, регистр 3, схему

4 сравнения, первый 5 и второй 6 элементш И, элемент HE 7, первый элемент ИЛИ 8, триггер 9, третий элемент И 10, второй элемент ИЛИ 11, выходы отлаживаемой микроЭВМ, соответствующие входам устройства: адрес- ный 12, модификации останова по адресу 13, признака начала команды

14, подтверждения прерывания 15, синхронизации 16, вектора прерывания 17, тактовый 18, приема вектора прерывания 19, вход 20 готовности отлаживаемой микроЭВМ, входы от пульта оператора: останова по адресу 2 1, останова по прерыванию 22, останова по вектору прерывания 23, пуска

24 и задания режима 25.

Устройство для отладки микроЭВМ обеспечивает следующие аппаратные режимы отладки: останов по адресу илн зоне общий, останов по адресу либо зоне адресов при записи в ОЗУ микрсЭВМ, при записи в стек, при записи

35 в область ОЗУ, не являющую< я стеком „ останов по адресу либо зоне адресов при чтении памяти, при чтении стека, при чтении области памяти, не являющейся стеком; останов по адресу либо

1 зоне адресов при вводе информации нэ внешнего устройства, останов по адресу либо зоне адресов при выводе информации вЬ внешнее устройство, останов по адресу либо зоне адресов при чтении кода команды, останов по адресу либо зоне адресов при чтении операндов команды, шаговый режим поциклового прохождения програьсы, шаговый режим покомандного прохождения

50 программ, останов по определенному вектору прерывания, останов по прерыванию.

Работа устройства для отладки микроЭВМ в режимах: останова по адресу 55 или зоне общий, останова по адресу либо зоне адресов при записи в ОЗУ, при записи в стек, при записи в область ОЗУ, не являющуюся стеком; останова по адресу; останова по адресу или зоне адресов при вводе информации из внешнего устройства, останова по адресу либо зоне адресов при выводе информации во внешнее устройство, останова по адресу либо зоне адресов при чтении кода команды, останова по адресу либо зоне адресов при чтении операндов команды, шаговый режим поциклового прохождения программы, шаговый режим покомандного прохождения программы описаны в известном устройстве.

Режим останова по определенному вектору прерывания реализован следующим образом.

В регистр 3 необходимо занести код, соответствующий заданному вектору прерывания. На вход останова по вектору прерывания 23 подать высокий уровень. При появлении сигнала подтверждения прерывания на входе

15 на выходе блока 2 готовности появится низкий уровень, который вызывает останов отлаживаемой микроЭВМ.

Одновременно на выходе триггера 9 появится высокий уровень, Если пришедший в последующий момент времени по входу 17 вектора прерывания код совпадает с занесенным в регистр 3, то на выходе схемы 4 сравнения появится высокий уровень, который, пройдя через элемент HE 7, приходит низким уровнем на третий вход третьего элемента И 10. В этом случае на выходе второго элемента ИЛИ 11 будет низкий уровень и микроЭВМ останется в режиме останова. Вывести ее из этого режима можно, подав на вход пуска 24 высокий уровень. Если пришедший по входу

17 вектора прерывания код не совпадает с занесенным в регистр 3, то на выходе третьего элемента И 10 появится высокий уровень, который, пройдя через второй элемент ИЛИ 11, вызовет установление высокого уровня на выходе блока 2 готовности, и отлаживаемая микроЭРМ продолжит работу.

Режим останова по признаку прерывания реализуется при высоком уровне на входе 22 останова по прерыванию.

При приходе сигнала подтверждения прерывания Hà í .Oö 15 на выходе первого элемента И 5 появится высокий уровень, который, гройдя через первый элемент ШП1 8, вызовет останов отлаживаемой ЭВ. 1. Так как на выхопе

1541615 второго элемента И Ь присутствует низкий уровень, то на выходе триггера 9 будет также низкий уровень, который предотвращает поступление высокого уровня на пятый вход блока 2 готовности и тем самым запрещает работу отлаживаемой микроЭВМ. Для того, чтобы отлаживаемая микроЭВМ продолжила работу, необходимо подать на вход 24 пуска высокий уровень.

Составитель И.Сигалов

Техред H.Äèäûê

Корректор M.Kó÷åðÿâàÿ

Редактор А.Козориз

Заказ 282 Тираж 568 Подписное

ВНИИПИ Государственного комитета .по изобретениям н открытиям при ГКПТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,101

Формула изобрет ения

Устройство для отладки микроЭВМ, содержащее блок останова по адресу, 15 блок готовности, причем адресный вход, вход модификации останова по адресу и вход останова па адресу устройства соединены соотве IcTBpHHo с первым„ вторым и третьим входами блока останова ио адресу, вход признака начала команды устройства соединен с четвертым входом блока останова по адресу и с первым входом блока готонности, выход которого является выходом останова устройства, вход синхронизации и тактовый вход устройства соединены соответственно с вторым и третьим входами блока готовности, вход задания режима устройства сое- 30 динен с четвертым входом блока готов-. ности, о т л и ч а ю щ е е с я тем, что, с целью сокращения времени отладки, в устройство введены регистр, схе- . ма сравнения, первый, второй и третий элементы И, первый и второй элементы

ИЛИ, триггер и элемент HF., причем входы вектора прерывания, остан .ва пп прерыванию, останова по вектору прерывания и приема вектора прерывания устройства соединены соответственно с первым входом схемы сравнения, с первым входом первого элемента И, с первым входом второго элемента И, и с первым входом третьего элемента

И, вход подтверждения прерывания устройства соединен с вторыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, вход синхронизации устройства соединен с тактовым входом триггера, выход которого соединен с вторым входом третьего элемента И, выходы блока останова по адресу и второго элемента И соединены соответственно с третьим входом первого элемента ИЛИ и информационным входом триггера, выход регистра соединен с вторым входом схемы сравнения, выход равенства которой через элемент

НЕ соединен с третьим входом третьего элемента И, выход третьего элемента И соединен с первым входом второго элемента ИЛИ, выход первого элемента ИЛИ и вход пуска устройства соединены соответственно с пятым входом блока готовности и с вторым входом второго элемента ИЛИ, выход которого соединен с шестым входом блока готовности.