Устройство для расширения непосредственно адресуемой памяти микропроцессора

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может использоваться для расширения непосредственно адресуемой памяти микропроцессора 580 ИК 80. Цель изобретения - увеличение быстродействия. Устройство содержит регистр 1 управления, дешифратор 2 команд, фиксатор 3 слова состояния, элементы И и ИЛИ, схему 6 сравнения кодов и счетчик 11 циклов команды. Устройство в течение выполнения машинного цикла микропроцессором анализирует тип функциональной памяти (память команд, память данных или стек) и разрешает доступ к выбранному типу памяти. Каждый функциональный тип памяти может иметь максимальный объем, допустимый для данного микропроцессора. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„154 I 620 (51) 5 С 06 Г 12/08

А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4351447/24-24 (22) 05. 10.87 (46) 07.02.90, Бюл, К"- 5 (72) M.È.1Нмулевич (53) 621.325 (088.8) (56) Иевкопляс Б.В. Микропроцессорные структуры. Инженерные решения. М,:

Радио и связь, 1986, с. 38-45.

Авторское свидетельство СССР

У 1361564, кл, 0 06 F 12/08, 1986. (54) УСТРОЙСТВО ЩИ РАСШИРЕНИЯ НЕПОСРЕДСТВЕННО АДРЕСУЕМОЙ ПАМЯТИ МИКРОПРОЦЕССОРА (57) Изобретение относится к вычислительной технике и может использоваться дпя расширения непосредствен2 но адресуемой памяти микропроцессора 580 ИК 80. I

6 сравнения кодов и счетчик 11 циклов команды. Устройство в течение выполнения машинного цикла микропроцессором анализирует тип функциональной памяти (память команд, памать данных или стек) и разрешает доступ к выбранному типу памяти, Каж- . дый функциональный тип памяти может иметь максимальный объем, допустимый для данного микропроцессора. 3 ил.

1541620

Изобретение относится к вычислительной технике и может использоваться в устройствах, построенных с применением процессоров, выставляющих на внешних выводах сигналы, информирующие о предстоящих действиях в следующем машинном цикле (слово состояния) и имеющих строб начала машинного цикла, например микропроцессора 580 ИК 80.

Цель изобретения — увеличение быстродействия.

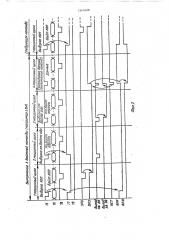

На фиг.1 представлена структурная схема устройства; на фиг.2 — временные диаграммы, поясняющие принцип работы устройства; на фиг.3 — таблица для программирования микросхемы

ПЗУ, используемой в качестве дешифратора команд (для микропроцессора

580 ИК 80), где однобайтным командам соответствует значение 04, двухбайтным 02, трехбайтным 03; значение адреса соответствует коду команды.

Устройство (фиг.1) содержит регистр 1 управления, дешифратор ? команд, фиксатор 3 слова состояния, элемент И 4,,элемент ИЛИ 5, схему 6 сравнения кодов, элементы И 7-9, элемент ИЛИ 10, счетчик 11 циклов команды и ключи 12-14.

Устройство, построенное, например, для применения с .широко ра;"-пространенным микропроцессором 580

ИК 80, работает следующим образом.

В фиксатор 3 слова состояния, представляющий собой двухраэрядный параллельный регистр, срезом строба состояния (STSTB) на входе 15 записываются разряды Д2 и Д5, поступающие по входу 16. В первом машинном ,цикле любой команды на выходе 17 фиксатора 3 -должен быть активный сигнал (фиг.2, 1/), который поступает на вход элемента ИЛИ 5 и устанавливает на его выходе сигнал выбора памяти команд (фиг.2, ВПК). Одновременно сигнал с выхода 17 фиксатора 3 поступает на элемент И 4 и открывает его. Срезом сигнала "Чтение памяти"

ЧТЗУ с шины управления, поступающим на вход 18 элемента И 4 (фиг.2, 18), записывается в регистр 1 управления (фиг.2, 3 ру) байт, содержащий код операции (команды), который одновременно считывается микропроцессором.

С выходов регистра в параллельном виде байт, содержащий КОП (код операции) поступает на входы дешифратор;, 2 команд. Дешифратор 2 реализован на микросхеме ПЗУ. В ячейках ПЗУ, адресуемых КОП, в зависимости от длины данной команды (один, два или три байта), хранятся числа 0100, 0010 или 0011 для одно-, двух- и трехбайтных команд соответственно, Если команда двух- или трехбайтная, то сигнал на третьем выходе дешифратора 2 (фиг.2, ДЗ) удерживает на выходе элемента ИЛИ 5 сигнал выбора памяти команд (фиг.2, ВПК), когда во втором и в третьем машинном цикле на выходе 17 фиксатора 3 снимается активный сигнал. Одновременно этот сигнал QTKphlB÷åò элемент И 8 и пропускает сигнал с линии STSTB на счетный вход счетчика 11 циклов команды.

По срезу сигнала STSTB счетчик 11 переходит в следующее состояние (начальное состояние). Комбинация с выходов счетчика 11 поступает на входы схемы, где сравнивается с комбинацией на первом и втором выходах дешифратора 2 °

В случае совпадения комбинаций на выходе схемы 6 устанавливается активный сигнал, который открывает элеЗО мент И 9 и следующий сигнал по линии

STSTB (фиг. 2, 1.5) через элементы

И 9 и ИЛИ 10 поступает на входы установки счетчика 11 циклов команды, устанавливая счетчик 11 в начальное положение 01 (фиг,2, УСТ). Одновре35 менно сигнал установки .с выхода элемента ИЛИ 10 поступает на вход сброса регистра 1 управления, который, обнуляясь, снимает с входов дешифратора 2 байт, содержащий KOII. Ha третьем выходе дешифратора 2 снимается активный сигнал (фиг.2, ДКЗ), что приводит к пропаданию сигнала выбора памяти команд (фиг.2, ВПК).и появлению сигнала выбора памяти данных (фиг,2, BIIP) на выходе элемента И 7, так как на выходе 19 фиксатора 3 также отсутствует активный сигнал. На временной. диаграмме показано выполнение команды (считывание данных иэ памяти в аккумуля50 тор), имеющий длину три байта и выполняемой за четыре машинных цикла. В первом — третьем машинных циклах из памяти команд считывается: КОЛ в пер-. вом машинном цикле и адрес во втсром и третьем машинных циклах. Исполняется команда в четвертом мапинном цикле, когда происходиг считывание из памяти данных.

5 154

Таким образом, йредлагаемое устройство автоматически, без управления со стороны программы, исходя из информации, содержащейся в слове состояния процессора и в КОП, выполняемой процессором в данный момент команды, вырабатывает сигналы. селекции памяти по функциональному признаку: память команд, память данных Й стек, Это позволяет иметь три независимые области памяти по 64 К байт, т.е. в 3 раза больше, чем позволяет непосредственно адресовать шестнадцатиразрядная шина адреса микропроцессора 580 ИК 80.

Формула изобретения

Устройство для расширения непосредственно адресуемой памяти микропроцессора, содержащее регистр управления, дешифратор команд и четыре элемента И, информационный вход-выход устройства соединен с информационным входом регистра команд, выход которого соединен с информационным входом дешифратора команд, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, в него введены фиксатор слова состояния, схема сравнения кодов, два элемента ИЛИ и счетчик циклов команды, информационный вход фиксатора слова состояния соединен с третьим и шестым разрядами информационного входавыхода устройства, первый выход фиксатора слова состояния соединен с первы-. ми входами первого элемента И и первого элемента ИЛИ, выход которого соеди1б20 нен с первым входом второго элемента

И, выход первого элемента И соединен с входом записи регистра управления, 5 первый и второй выходы дешифратора команд соединены с первым входом схемы сравнения кодов, третий выход дешифратора команд соединен с первым входом третьего элемента И и вторым входом первого элемента ИЛИ, выход счетчика циклов команды соединен с вторым входом схемы сравнения кодов, выход которого соединен с первым входом четвертого элемента V., выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входами установки в "0" регистра управления и асинхронной загрузки счетчика циклов. команды, счетный вход которого соединен с выходом третьего элемента И, вход сброса устройства соединен с вторым входом второго элемента ИЛИ„ вход строба состояния устройства соединен с входом стробирования фиксатора слова состояния и вторыми входами третьего и четвертого элементов И, второй выход фиксатора слова состояния соединен с вторым входом второго элемента И, выход первого элемента ИЛИ является выходом выборки памяти команд устройства, выход и второй вход второго элемента И являются выходами выборки памяти данных и стека соответственно, вход чтения-записи устройства соединен с вторым входом первого элемента И.

1541620

1541620

ОООО ооЯ

СЯ о о .5 о с11 сЯ ооо Ф 4 -г Ф оо.—. о сф Р3 О> ооо

О о

О

OОO

РЭ РЗ ооо

rv осч ооо

° ф С9 9 ооо 4 1 Осг оооо

ООООЕЕ

О О О О О О

ООО с Ф Ф Ф Ф -г

О О О О О О 1 ооо се< СМ М

ООО г Ф ооо

СМ М СМ СМ се< с)4

О О О О О О

Я Ф Ф Ф Я Ф о

-14

О о о Ф Я

At

O :г

At о Ф

O Ф

О Ф

1 1 3 сР с г Ф

О О О О О О

С 3 ооо с1 Ф Ф сР " 3

О О ) О О О с1 с"Э М

ООО

38OSO

Я Р3 с9

rl4 Ф тР ° .г оооо Р 4

О О 4 ;Р

OOO

О

ЯОРсЯ оооо оооо

O ..Л

О

О О О Я О О () О

О О О О О О О О

O О O O O О O О

О

33

О

О

Дъ

Составитель А. Ушаков

Редактор А.Козориз Техред М.Дидык

М.Иаксимишинец

Корректор

Заказ 282 Тираж 567 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д. 4/5 4 4 Ф

ООО

At Ж СЧ ооо 4 с1 ооо сР г Ф -г сР

О О О О О О

3 3 4 сг 4 3

ОООООО с 4 «ф РЭ С9 с 4 сф

О О О О О О сФ 4 Ф Ф 3 Ф

О О О-О О О

3 Ф " =Р 1

О О О О О О с9 . э м Рэ с сф

О О О О О О

О О О О О О

Производственно-издательский комбинат

"Патент", г. Ужгород, ул. Гагарина., 101